1.本公开内容关于储存数据的技术,特别是关于一种存储器装置及集成电路。

背景技术:

2.集成电路存储器装置正逐渐变得更小、速度更快。储存装置的尺寸的一个限制是取决于页面缓冲电路中感测电容的大小。为了感测储存于储存装置中的数据,感测电容需要具有大的电容,因此导致了较大的面积。因此,亟需一种能提供大且稳定的电容、但具有小体积的页面缓冲电路。

3.公开内容

4.本公开内容描述一种系统及技术,用以管理存储器装置中的页面缓冲器,存储器装置可以是非易失性存储器,例如快闪存储器。

5.本公开内容的一方面为一种存储器装置,包含:存储器阵列,包含多个存储器单元;多个存储器单元线,分别连接至存储器阵列中存储器单元的多条线;以及页面缓冲电路,包含耦接至存储器单元线的多个页面缓冲器。每个页面缓冲器包含感测闩锁电路及储存闩锁电路。感测闩锁电路包含感测晶体管,其中感测晶体管耦接于感测节点及至少一个感测闩锁单元,感测闩锁单元具有耦接于该感测节点的第一节点及耦接于感测晶体管的第二节点。储存闩锁电路包含至少一个储存闩锁单元,其中储存闩锁单元包含第三节点及第四节点,第三节点及该第四节点耦接于感测节点。感测晶体管包含第一端、栅极端及第二端。第一端耦接于该至少一个感测闩锁单元的第二节点,栅极端耦接于感测节点及该至少一个储存闩锁单元的第三节点及第四节点,且第二端耦接于接地端。

6.在部分实施例中,至少一个感测闩锁单元包含:第一闩锁器,包含第一反相器;第一闩锁控制电路,耦接于第一闩锁器及感测晶体管的第一端。该至少一个储存闩锁单元包含:第二闩锁器,包含第二反相器;以及第二闩锁控制电路,耦接于第二闩锁器及感测晶体管的栅极端。

7.在部分实施例中,第二闩锁控制电路包含第一控制晶体管及第二控制晶体管。第一控制晶体管及第二控制晶体管的多个源极端耦接于感测节点及感测晶体管的栅极端。

8.在部分实施例中,每一个感测闩锁单元包含第一耦合电路及第一闩锁器。第一耦合电路耦接于该感测节点。每一个储存闩锁单元还包含第二耦合电路及二闩锁器,第二耦合电路耦接于感测节点。

9.在部分实施例中,每一个页面缓冲器还包含:预充电电路,耦接于感测节点,且用以在预充电阶段中对感测节点预充电;以及位线控制电路,包含第一控制节点及第二控制节点。第一控制节点耦接于这些存储器单元的其中一个的位线,且第二控制节点耦接于感测节点。位线控制电路用以:在预充电阶段中对该位线充电;以及在预充电阶段后的放电阶段中,通过导通感测节点及位线,使位线放电,以提供感测电流至存储器单元的其中一个。

10.在部分实施例中,页面缓冲器用以在预充电阶段中,使位线切断感测节点的连线,以及在放电阶段中,导通感测节点。

11.在部分实施例中,储存闩锁电路用以导通该至少一个储存闩锁单元中的一个或多个闩锁控制电路,以更新至少一个储存闩锁单元中一个或多个闩锁器的感测结果。

12.在部分实施例中,感测闩锁电路中的感测闩锁单元的数量及储存闩锁电路中的储存闩锁单元的数量系关联于这些存储器单元的存储器类型。

13.在部分实施例中,储存闩锁电路中的储存闩锁单元的数量是由该存储器类型的可储存位的数量来决定。

14.在部分实施例中,感测闩锁电路及储存闩锁电路用以:当存储器单元的存储器类型是单层单元(single level cell,简称slc)时,感测闩锁电路包含一个感测闩锁单元、储存闩锁电路包含一个储存闩锁单元。若存储器单元的存储器类型是多层单元(multi level cell,简称mlc),感测闩锁电路包含一个感测闩锁单元、储存闩锁电路包含二个储存闩锁单元。若存储器单元的存储器类型是三层单元(triple level cell,简称tlc),感测闩锁电路包含二个感测闩锁单元、储存闩锁电路包含三个储存闩锁单元。若存储器单元的存储器类型是四层单元(quad-level cells,简称qlc),感测闩锁电路包含二个感测闩锁单元、储存闩锁电路包含四个储存闩锁单元。

15.在部分实施例中,储存闩锁电路并不包含与感测晶体管实质上相同的晶体管。

16.在部分实施例中,感测闩锁电路包含实质上与感测晶体管相同的一个或多个晶体管。感测闩锁电路包含多个感测闩锁单元,该一个或多个晶体管的数量小于这些感测闩锁单元的数量。

17.本公开内容的另一方面为一种集成电路,包含感测闩锁电路及储存闩锁电路。感测闩锁电路包含:一感测晶体管,耦接于感测节点;至少一个感测闩锁单元,包含第一节点及第二节点,其中第一节点耦接于感测节点,第二节点耦接于感测晶体管。储存闩锁电路包含:至少一个储存闩锁单元,包含第三节点及第四节点,其中第三节点及第四节点耦接于感测节点。感测晶体管包含:第一端,耦接于该至少一个感测闩锁单元的第二节点;第二端,耦接于接地端;以及栅极端,耦接于感测节点及该至少一个储存闩锁单元的第三节点及第四节点。

18.在部分实施例中,每一个感测闩锁单元包含:第一闩锁器,包含第一反相器;以及第一闩锁控制电路,耦接于第一闩锁器及感测晶体管的第一端。每一个储存闩锁单元包含:第二闩锁器,包含第二反相器;以及第二闩锁控制电路,耦于第二闩锁器及感测晶体管的栅极端。

19.在部分实施例中,第一闩锁控制电路包含用以接收设定信号的第一晶体管及接收重置信号的第二晶体管。

20.在部分实施例中,每一个感测闩锁单元包含:第一耦合电路,耦接于感测节点及第一闩锁器。每个储存闩锁单元包含:第二耦合电路,耦接于感测节点及第二闩锁器。

21.在部分实施例中,感测闩锁单元包含多个感测闩锁单元,且这些感测闩锁单元的每一个分别包含第一节点及第二节点。第一节点耦接于感测节点,且第二节点耦接于感测晶体管的漏极端。储存闩锁单元包含多个储存闩锁单元,这些储存闩锁单元的每一个分别包含第三节点及第四节点,其中第三节点耦接于感测节点,第四节点耦接于感测晶体管的栅极端。

22.在部分实施例中,感测闩锁电路包含至少一个感测晶体管,且该至少一个储存闩

锁单元并不包含实质上与感晶体管相同的晶体管。

23.在部分实施例中,感测闩锁电路及储存闩锁电路用以具备一个等效电容。等效电容关联于栅极电容,栅极电容则关联于感测晶体管,等效电容还关联于一个或多个结电容。该一个或多个结电容关联于感测闩锁电路及储存闩锁电路中的晶体管。

24.在部分实施例中,等效电容关联于感测闩锁电路及储存闩锁电路中的一个或多个金属布线。

25.在部分实施例中,栅极电容与结电容相比,具有更接近于阈值电压的大电容值变化。

26.在部分实施例中,还包含预充电电路及位线控制电路。预充电电路耦接该感测节点,且用以在预充电阶段中对感测节点预充电。位线控制电路包含第一控制节点及第二控制节点。第一控制节点耦接于存储器单元中的位线,且第二控制节点耦接于感测节点。位线控制电路用以:在预充电阶段中,对位线进行预充电;以及在预充电阶段后的放电阶段中,通过导通感测节点及位线,对感测节点进行放电,以提供感测电流至存储器单元。

27.在部分实施例中,位线控制电路用以在预充电段中,切断位线与感测节点之间的连线。

28.在部分实施例中,感测闩锁电路用以:当存储器单元储存0位时,感测节点上的感测电压大于阈值,且感测晶体管被导通,以将被该至少一个感测闩锁单元所闩锁的位值改变为0;以及当存储器单元储存1位时,感测节点上的感测电压小于或等于阈值,且感测晶体管被关断,以将被该至少一个感测闩锁单元所闩锁的位值维持为1。

29.在部分实施例中,储存闩锁电路用以:导迪至少一个储存闩锁单元中的一个或多个闩锁控制电路,以更新至少一个储存闩锁单元中一个或多个闩锁器的感测结果。

30.在部分实施例中,感测闩锁单元包含第一类型闩锁器,储存闩锁单元包含第二类型闩锁器。第一类型闩锁器与第二类型闩锁器不同。

31.在部分实施例中,闩锁器的第一类型及第二类型中的其中一个是三态闩锁器(triple-state latch)或抑制闩锁器(fighting latch)。

32.本公开内容的另一方面为一种集成电路,包含第一闩锁电路及第二闩锁电路。第一闩锁电路包含感测晶体管及一个或多个第一闩锁单元。感测晶体管耦接于感测节点,且第一闩锁单元耦接于感测晶体管。第二闩锁电路包含一个或多个第二闩锁单元。每一个第二闩锁单元系与第一闩锁单元相同。感测晶体管与第二闩锁电路中的晶体管的差异在于,感测晶体管的栅极端耦接于感测节点,且用以作为栅极电容。

33.在部分实施例中,集成电路还包含第三电路,用以:在第一阶段中,分别对感测节点及位线预充电,其中位线耦接于存储器装置中的存储器单元,且用以断开该感测节点的连接;以及在第一阶段后的第二阶段中,通过将感测节点导通至该位线,根据等效电容放电感测节点的感测电压,以通过位线在存储器单元上产生感测电流。等效电容系依据栅极电容,栅极电容关联于感测晶体管。等效电容还依据于一个或多个结电容,结电容关联于第一闩锁单元及第二闩锁单元中的多个晶体管。结电容中的整体电容值实质上大于栅极电容的电容值。第一闩锁电路用以:在第二阶段后,根据感测节点上被放电的感测电压,更新被第一闩锁电路所闩锁的数据。第二闩锁电路用以:导通第二晶体管中的至少一个,以将被第一闩锁电路所闩锁的数据更新至第二闩锁电路中的至少一个闩锁器。

34.在部分实施例中,结电容中的整体电容值实质上大于栅极电容的电容值。

35.在部分实施例中,第一闩锁单元用以:当存储器单元储存位0,且感测节点的感测电压值大于阈值电压时,导通感测晶体管,以改变被感测闩锁器闩锁至0的位值;或当存储器单元储存位1,且感测节点的感测电压值小于或等阈值电压时,关断感测晶体管以维持被感测闩锁单元闩锁于1的位值。

36.本公开内容的另一方面为一种管理存储器装置中页面缓冲器的方法,包含下列步骤:对耦接于存储器装置中的存储器单元的位线进行预充电;对页面缓冲器中的感测节点进行预充电,其中页面缓冲器包含感测闩锁电路及储存闩锁电路,感测闩锁电路包含耦接于感测节点的感测晶体管及至少一个感测闩锁单元,感测闩锁单元具有耦接于感测节点的第一节点及耦接于感测晶体管的第一端的第二节点,储存闩锁电路包含至少一个储存闩锁单元,储存闩锁单元具有耦接于感测节点及感测晶体管的栅极端的第三节点及第四节点,感测节点的第二端耦接于接地端;导通位线及感测节点,以在感测节点上放电感测电压,以通过位线提供感测电流至存储器单元;以及根据感测节点上所放电的感测电压,更新被感测闩锁电路闩锁的数据。

37.在部分实施例中,根据感测节点上所放电的感测电压,更新被感测闩锁电路闩锁的数据的方法包含:当存储器单元储存0的位值且感测节点上的感测电压大于阈值电压时导通感测晶体管以改变被至少一个感测闩锁单元闩锁于0的位值;或当存储器单元储存1的位值,且感测节点的感测电压大于或等于阈值电压时,关断感测晶体管,以维持被感测闩锁单元闩锁于1的位值。

38.在部分实施例中,该方法还包含:导通储存闩锁单元中的一个或多个闩锁控制电路,以将感测结果写入储存闩锁单元中的一个或多个储存闩锁单元。

39.本公开内容的另一方面为一种快闪存储器,包含页面缓冲电路及位线。页面缓冲电路包含子电路及预充电电路。子电路具有耦接于位线节点及感测端(或感测节点)之间的钳位电路。预充电电路耦接于供电节点及感测端之间。钳位电路用以稳定流经钳位电路的电流。预充电电路用以提供预充电电压至感测端。供电节点耦接于供电电源。位线节点耦接于位线。页面缓冲电路还包含感测闩锁电路及储存闩锁电路。感测闩锁电路具有感测晶体管及第一闩锁单元。储存闩锁电路具有第二闩锁单元。

40.在部分实施例中,第一闩锁单元包含闩锁电路、第一晶体管、第二晶体管、第三晶体管及第四晶体管,闩锁电路耦接于数据线节点及数据线反相节点之间。第一晶体管耦接于切换节点及数据线反相节点之间。第一晶体管的栅极用以接收第一控制信号。第二晶体管耦接于切换节点及数据线节点之间。第二晶体管的栅极用以接收第二控制信号。第三晶体管耦接于感测连接节及连结节点之间。第三晶体管的栅极用以接收第三控制信号。第四晶体管耦接于连结节点及接地端之间。第四晶体管的栅极耦接于数据线节点。感测晶体管耦接于切换节点及接地端之间。感测晶体管的栅极耦接于感测连接接点。感测连接节点耦接于感测端。感测闩锁电路用以根据第三控制信号及数据线节点的信号,放电感测端上的电压,以及通过感测晶体管感应感测端的电压。

41.在部分实施例中,第二闩锁单元包含闩锁电路、第一晶体管、第二晶体管、第三晶体管及第四晶体管。闩锁电路耦接于数据线节点及数据线反相节点之间。第一晶体管耦接于切换节点及数据线反相节点之间。第一晶体管的栅极用以接收第一控制信号。第二晶体

管耦接于切换节点及数据线节点之间。第二晶体管的栅极用以接收第二控制信号。第三晶体管耦接于感测连接节点及连结节点之间,感测连接节点耦接于切换节点。第三晶体管的栅极用以接收第三控制信号。第四晶体管耦接于连结节点及接地端之间。第四晶体管的栅极耦接于数据线节点。第二闩锁单元的切换节点耦接于感测晶体管的栅极。储存闩锁电路用以闩锁感测端的电压至预设电平。

42.上述技术的实现包括方法、系统、电路、计算机程序产品和计算机的可读存储介质。在一实施例中,可以在非易失存储器中执行一种方法,并且该方法可以包括上述动作,例如,用于管理页面缓冲电路的动作。在另一实施例中,一个前述的计算机程序产品可适当地实现在储存一个或多个处理器执行的指令的非暂时性机器可读取媒体中。上述动作可被一个或多个处理器中配置的指令来执行。前述计算机的可读取媒体用以储存指令,当一个或多个处理器执行时,这些指令用以使一个或多个处理器执行上述动作。

43.技术可由具有任何类型的多个闩锁器且可实现各种功能的电路或设备来实现。闩锁器可以分成两组或更多组,每组被配置为执行对应的功能。这些组可以使用不同类型的闩锁器,例如,三态闩锁器或抑制闩锁器。本公开内容的技术能减小装置面积(例如,页缓冲电路和/或储存器件的尺寸)、最小化电容器变化(例如,通过栅极电容)、降低功耗(例如,通过大面积电容),并提高设备性能(例如,感测的精确度)。

44.举例而言,存储器中的页面缓冲器包括多个闩锁器,这些闩锁器被配置为实现包含读取、写入和擦除等功能的操作。相较于将所有闩锁器视为相同的技术,本公开内容使页面缓冲器中的闩锁器可被分类为至少两种电路:感测闩锁电路和储存闩锁电路。感测闩锁电路包含具有栅极端的感测晶体管。栅极端耦接至用于通过位线感测数据的感测节点。储存闩锁电路不加入感测,而只储存来自快取数据闩锁(cache data latch;cdl)电路或感测闩锁电路的数据。因此,储存闩锁电路可以不包括感测晶体管。由于与感测晶体管相关联的栅极电容在阈值电压附近具有较大的电容变化,因此最小化感测晶体管的数量可以大大降低电容变化,从而增加感测节点处电容的稳定性。例如,由于不同的pvt(过程-电压-温度)效应,提高感测精度和/或感测良率。

45.本公开内容可以用任何类型的储存晶体管(或储存单元)、任何类型的金属氧化物硅(mos)晶体管(例如n通道和/或p通道晶体管)、任何类型的双极性晶体管(bjt)、以及任何类型的运算放大器来实现。这些技术可以应用于不同类型的储存系统,例如二维(2d)储存系统或三维(3d)储存系统。这些技术可以应用于各种存储器类型,例如slc装置、mlc装置如二阶单元装置(2-level)或tlc装置。这些技术可以应用于各种类型的非易失性储存设备,例如静态随机存取存储器(sram)、动态随机存取存储器(dram)、快取存储器(例如nor和/或nand)、电阻随机存取存储器(rram)、磁阻随机存取存储器(mram)、相变随机存取存储器(pcram)等。另外,这些技术可以应用于各种类型的装置和系统,例如安全数据(sd)卡、嵌入式多媒体卡(emmc)或固态驱动器(ssd)、嵌入式系统等。

46.以下描述及附图中说明了本公开内容的实施方式的细节。实施方式、附图及权利要求范围已清楚呈现出本公开内容的各特征、观点和优点。

附图说明

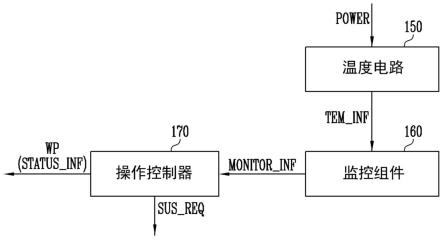

47.图1a为根据本公开内容的部分实施例的存储器系统的示意图。

48.图1b为根据本公开内容的部分实施例的二维存储器(2d)的示意图。

49.图1c为根据本公开内容的部分实施例的三维存储器(3d)的示意图。

50.图2为根据本公开内容的部分实施例的具有多个页面缓冲器的页面缓冲电路的示意图。

51.图3为根据本公开内容的部分实施例中,结电容与栅极电容的电压电容的关系示意图。

52.图4为根据本公开内容的部分实施例的具有感测闩锁电路及储存闩锁电路的页面缓冲器的示意图。

53.图5为根据本公开内容的部分实施例的闩锁单的示意图。

54.图6a~6c为图5的页面缓冲器于不同阶段的示意图。

55.图7为根据本公开内容的部分实施例,图6a~6c中页面缓冲器的不同节点于不同阶段的电压变化示意图。

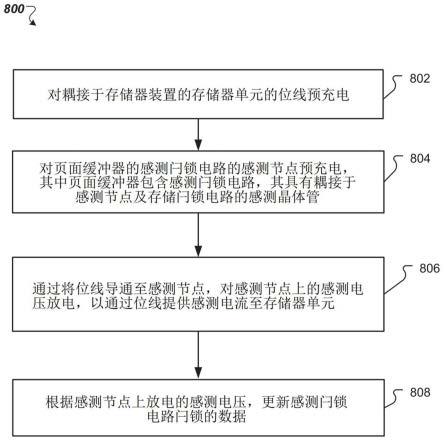

56.图8为根据本公开内容的部分实施例的管理存储器装置的页面缓冲器的方法流程图。

57.附图标记说明

58.100:系统

59.110:装置

60.112:装置控制器

61.113:处理器

62.114:内部存储器

63.116:存储器

64.120:主机

65.140:二维存储区块

66.141:存储器单元

67.142-150:晶体管

68.152:存储分页

69.154:存储串列

70.156:串列选择线

71.157:存储器单元

72.158:接地选择线

73.159:共同源极线

74.200:存储器装置

75.202:存储器界面

76.204:控制逻辑电路

77.206:x-译码器

78.208:数据缓冲器

79.210:存储器阵列

80.215:位线

81.220:页面缓冲电路

82.222:页面缓冲器

83.230:快取数据闩锁电路

84.300:电压电容的关系示意图

85.302:曲线

86.304:曲线

87.306:线

88.402:放电电路

89.406:结电容

90.408:栅极电容

91.410:预充电电路

92.420:位线控制电路

93.430:感应闩锁电路

94.440a-460c:闩锁单元

95.450:储存闩锁电路

96.410:预充电电路

97.420:位线控制电路

98.430:感应闩锁电路

99.450:储存闩锁电路

100.500:闩锁单元

101.502:第一节点

102.504:第二节点

103.510:耦合电路

104.520:闩锁器

105.522:第一反相器

106.524:第二反相器

107.530:闩锁控制电路

108.sst:串列选择晶体管

109.ssl:串列选择线

110.gsl:接地选择线

111.csl:共同源极线

112.bl

0-bln:位线

113.wl

0-wln:字线

[0114]vth

:阈值电压

[0115]

vddi:供电电压

[0116]

pos:信号

[0117]

stb:信号

[0118]

pre:信号

[0119]

psen:信号

[0120]

disch:信号

[0121]

blc1-blc3:信号

[0122]

r:信号

[0123]

802-808:步骤

具体实施方式

[0124]

以下将以附图通过本公开的多个实施方式,为明确说明起见,许多实务上的细节将在以下叙述中一并说明。然而,应了解到,这些实务上的细节不应用以限制本公开。也就是说,在本公开部分实施方式中,这些实务上的细节是非必要的。此外,为简化附图起见,一些已知惯用的结构与元件在附图中将以简单示意的方式示出。

[0125]

于本文中,当一元件被称为“连接”或“耦接”时,可指“电性连接”或“电性耦接”。“连接”或“耦接”亦可用以表示二或多个元件间相互搭配操作或互动。此外,虽然本文中使用“第一”、“第二”、

…

等用语描述不同元件,该用语仅是用以区别以相同技术用语描述的元件或操作。除非上下文清楚指明,否则该用语并非特别指称或暗示次序或顺位,亦非用以限定本公开。

[0126]

图1a为用于说明系统100的示意图。系统100包含装置110及主机120。装置110包含装置控制器112及存储器116。装置控制器112包含处理器113及内部存储器114。在部分实施例中,装置110包含耦接于装置控制器112的多个存储器116。

[0127]

在部分实施例中,装置110是一种储存装置。举例而言,装置110可以是一种嵌入式多媒体存储卡(embedded multi media card)、一种安全数字卡(secure digital card)、一种固态硬盘(solid-state drive)或任何其他适合的储存媒体。在部分实施例中,装置110是一种智慧手表、数字相机或媒体播放器。在部分实施例中,装置110是一种客户端装置,耦接于主机120。举例而言,装置110是一种sd卡,设置于数字相机或媒体播放器等主机120中。

[0128]

装置控制器112是一种通用微处理器,或一种特殊应用微处理器(application-specific microcontroller)。在部分实施例中,装置控制器112为装置110的存储器控制器。以下描述基于装置控制器112是存储器控制器所实现的各项技术。然而,以下部分描述的技术也适用于装置控制器112不是存储器控制器的其他情况。

[0129]

处理器113用以执行指令及处理数据。指令包括固件指令和/或其他程序指令,分别作为固件代码和/或其他程序代码储存在辅助存储器中。数据包含对应于固件的程序数据和/或由处理器执行的其他程序,以及其他合适的数据。在部分实施例中,处理器113是通用微处理器或专用微控制器。处理器113也作为中央处理单元(cpu)。

[0130]

处理器113处理(access)来自内部存储器114的指令和数据。在部分实施例中,内部存储器114是静态随机存取存储器(sram)或动态随机存取存储器(dram)。例如,在部分实施方式中,当装置110是emmc、sd卡或智慧手表时,内部存储器114是sram。在部分实施方式中,当装置110是数字相机或媒体播放器时,内部存储器114是dram。

[0131]

在部分实施例中,内部存储器是包含在装置控制器112中的快取存储器,如图1a所示。内部存储器114用以储存指令代码及/或处理器113于运行时所需的数据。指令代码对应于处理器113执行的指令。

[0132]

装置控制器112将指令代码和/或数据从存储器116传送到内部存储器114。存储器

116可为半导体装置。在部分实施例中,存储器116是非易失性存储器,用以指令和/或数据的长期储存,例如nand快取存储器装置,或其他合适的非易失性存储器。在存储器116是nand快取存储器的实施例中,装置110是快取存储器设备,例如存储卡,并且装置控制器112是nand快取控制器。举例而言,在部分实施例中,当装置110为emmc或sd卡时,存储器116为nand快取;在部分实施例中,当装置110为数字相机时,存储器116为sd卡。在部分实施例中,当装置110是媒体播放器时,存储器116是硬件。

[0133]

存储器116包含多个存储区块。存储器116可为二维存储器,包含二维存储区块。存储器116亦可为三维存储器,包含三维存储区块。

[0134]

图1b所示为根据本公开内容的部分实施例中,在存储器116为二维存储器时,二维存储区块140示意图。存储区块140包含存储器单元141。存储器单元141彼此串联,并耦接于多列位线(bit lines;bl)bl0、bl1、...、bl

n-1

及bln以形成多个的存储串列144。存储器单元141还耦接于多排字线(word lines;wl)wl0、wl1、

…

、wl

n-1

及wln以形成多个的存储分页142。

[0135]

存储区块中每一个存储器单元包含一个晶体管结构,晶体管结构具有栅极、漏极、源极以及由漏极与源极所定义的通道。每一个存储器单元位于字线和位线间的交叉处,其中栅极连接字线、漏极连接位线、源极连接源极线,使存储器单元依序地连接至接地端。在部分实施例中,快闪存储器单元的栅极具有双栅极结构,包括控制栅极和浮动栅极(floating gate),其中浮动栅极悬浮(suspended)在两个氧化物层之间,以捕捉(trap)对单元进行编程的电子。

[0136]

存储区块中每一个存储器单元包含一个晶体管结构,晶体管结构具有栅极、漏极、源极以及由漏极与源极所定义的通道。每一个存储器单元位于字线和位线间的交叉处,其中栅极连接字线、漏极连接位线、源极连接源极线,使存储器单元依序地连接至接地端。在部分实施例中,快闪存储器单元的栅极具有双栅极结构,包括控制栅极和浮动栅极(floating gate),其中浮动栅极悬浮(suspended)在两个氧化物层之间,以捕捉(trap)对单元进行编程的电子。

[0137]

存储串列144包含互相串联的多个存储器单元141、串列选择晶体管(string select transistor;sst)143及接地选择晶体管(ground select transistor;gst)145。串列选择晶体管143的栅极连接至串列选择线(string select line;ssl)146。不同存储串列中的串列选择晶体管143的栅极会连接至相同的串列选择线(ssl)。存储器单元141的栅极分别连接至字线wl0、wl1、

…

、wln-1、wln。存储串列144或存储器单元141通过接地选择晶体管145(gst)连接至共同源极线(common source line;csl)149。共同源极线(csl)149可耦接于接地端。接地选择晶体管(gst)145的栅极连接于接地选择线(ground select line;gsl)148。不同存储串列144的接地选择晶体管(gst)145的栅极连接至相同的接地选择线(gsl)148。

[0138]

存储分页142包含多个存储器单元141。存储分页142中存储器单元141的栅极分别串联于字线(wl)。当输入电压被施加至字线时,输入电压也会被施加至存储分页142中的存储器单元141。于读取操作中,为了读取存储区块140的存储分页142,较低的电压将被施加到对应于特定存储分页142的字线。同时,较高的电将被压施加到存储区块140中的其他存储分页。

[0139]

图1c所示为根据本公开内容的部分实施例中,当存储器116(如图1a所示)是一种

3d存储器时的3d存储区块150的示意图。3d存储器150可以是图1b中2d存储区块140的堆叠。存储器单元157被布置在三个维度中,例如xyz坐标系,并且耦接至多个字线以形成多个存储分页(导电层或字线层)152,以及耦接至多个位线以形成多个存储串列154。存储分页152可以是在xy平面中的层,且同一层上的存储器单元157可以耦合到一条字线并具有相同的电压。每个存储分页152可以连接到驱动电路中各自的接触点(contact pad),驱动电路例如是x-译码器(或扫描驱动器)。

[0140]

存储串列154包含沿着z方向垂直串联的多个存储器单元157,其中存储器单元可以被配置为耦合到串列选择线(ssl)156的串列选择晶体管sst,且存储器单元可以被配置为耦合到接地选择线(gsl)158的接地选择晶体管gst。存储串列154连接到一个或多个驱动器,例如数据驱动器。存储器单元157的存储串列154经由接地选择晶体管(gst)连接到共同源极线(csl)159。共同源极线csl 159可以是形成在3d存储器的基板上的导电层(或多条导线)。共同源极线csl 159可耦接至接地端。

[0141]

图2为用以说明存储器装置200的示例性设置的示意图。存储器装置200可以被实现为图1a所示的存储器116。存储器装置200包含存储器阵列210。存储器阵列210包含相互串联的多个存储器单元,例如图1b所示的存储器单元141或图1c所示的存储器单元157,这些存储器单元耦接于多列字线及多行位线。

[0142]

存储器单元包含被配置为存储元件的存储晶体管。存储晶体管可以包括硅-氧化物-氮化物-氧化物-硅(silicon-oxide-nitride-oxide-silicon;sonos)晶体管、浮栅晶体管、氮化物只读存储器(nitride read only memory;nrom)晶体管或可以存储电荷的任何合适的非易失性mos装置。

[0143]

存储器装置200包括存储器界面202,存储器界面202具有多个用于接收数据的输入/输出(i/o)端口,例如从一存储器控制器接收数据,像是第1图的装置控制器112,或个输入/输出(i/o)端口可用于从存储器阵列210输出数据。存储器装置200包括数据缓冲器208,数据缓冲器208被配置为缓冲通过存储器界面202接收和输出的数据。

[0144]

存储器装置200还包括x-译码器(或列译码器)206和y-译码器(图中未示)。每个存储器单元通过各自的字线耦接到x-译码器206并且通过各自的位线215(bl1、bl2、...、bln)耦接到y-译码器。因此,x-译码器206和y-译码器可以通过对应的字线和对应的位线215,选择每个存储器单元用于读取或写入操作。

[0145]

存储器装置200包括页面缓冲电路220,其包括多个页面缓冲器222。每个页面缓冲器222(pb1、pb2、pb3、...、pbn)通过对应的位线215(bl1、bl2、bl3、...、bln)连接到存储器阵列210。在部分实施例中,页面缓冲器222通过与对应的位线215相关联的数据线连接到y译码器,位线215连接至存储器阵列210中对应存储器单元线(a corresponding line of memory cells)。页面缓冲器用以控制对应的位线的电压,以对耦接至对应位线的存储器单元执行操作,例如读取、编程或擦除。

[0146]

在部分实施例中,存储器装置200还包括快取数据缓冲电路230(cdl),其耦接于页面缓冲电路220和数据缓冲器208之间。在编程或擦除操作期间,快取数据缓冲电路230用以储存存储器的数据,或个用以将数据输出至页面缓冲电路220中的一个或多个页面缓冲器222。在读取操作期间,快取数据缓冲电路230用以储存来自页面缓冲电路220中一或多个页面缓冲器222的数据,或个输出数据至数据缓冲器208。

[0147]

存储器装置200还包含控制逻辑电路204、数据缓冲器208、页面缓冲电路220及快取数据缓冲电路230。控制逻辑电路204耦接于存储器装置200中的元件。存储器装置200包含x-译码器及y-译码器。控制逻辑电路204用以接收指令(command)、地址信息(address information)及/或数据,例如通过存储器界面202,接收来自于如图1a所示的装置控制器112的存储器控制器的数据。控制逻辑电路204还可处理指令(command)、地址信息(address information)及/或数据,例如,用以产生存储器阵列210中(例如:区块或页面的)实体地址信息。

[0148]

在部分实施例中,控制逻辑电路204包含数据暂存器、sram缓冲器、地址产生器、模式逻辑电路(mode logic)及状态机器(state machine)。模式逻辑电路用以确认是否存在读取或写入操作,并将确认结果提供给状态机器。

[0149]

在写入操作期间,控制逻辑电路204中的数据暂存器可暂存来自存储器界面202的输入数据,且控制逻辑电路204中的地址产生器可以产生对应的实体地址,以将输入数据储存在存储器阵列210的指定存储器单元中。地址产生器可以连接并控制x-译码器206和y-译码器,以通过对应的字线和位线选择指定的存储单元。只要有供电电压,sram缓冲器就可以将来自数据暂存器的输入数据保留在其存储器中。状态机器用以处理来自sram缓冲器的写入信号,且向电压产生器提供控制信号。电压产生器可以向x-译码器206和/或y-译码器提供写入电压。y-译码器用以将写入电压输出到多条位线(bl),以将输入数据储存在指定的多个存储器单元中。

[0150]

在读取操作期间,状态机器可对电压产生器和页面缓冲电路220提供控制信号。电压产生器提供读取电压至x-译码器206和y-译码器,以选择存储器单元。页面缓冲器222可以通过耦接至页面缓冲器222及被选择的存储器单元的位线215,感测代表储存于被选择的存储器单元中的数据位(“1”或“0”)的小功率信号(如:电流信号)。感测放大器可将小功率信号的振幅(swing)放大至可被识别的逻辑电平,因此数据位可被存储器装置200内部或外部的逻辑电路正确解译(interpreted)。在部分实施例中,感测放大器包含页面缓冲电路220和/或快取数据闩锁电路230。数据缓冲器208可接收来自感测放大器的已放大电压,并通过存储器界面202,将放大的功率信号输出到存储器装置200外部的逻辑电路。

[0151]

为了通过感测流经对应位线的电流,以感测存储器单元中储存的数据,页面缓冲器须在感测节点上具备电容,以对感测节点预充电或放电。在页面缓冲器的预充电阶段,感测节点的电容被预充电至预设的感测电压。接着,在预充电阶段后的放电阶段,被储存于电容中的电荷通过感测电流放电,感测电流流经对应的位线而至存储器单元。被页面缓冲器中一个或多个栓锁器所闩锁的位值可以根据感测节点上的放电感测电压v

sen

更新。

[0152]

在放电阶段后的感测阶段(或称选通(strobing)阶段),若存储器单元储存的位为“0”,感测节点上的放电感测电压v

sen

可以大于预设的阈值电压v

th

,例如:关联于页面缓冲器内闩锁器的选通电压(strobe voltage)v

strobe

。据此,页面缓冲器可用以将一个或多个闩锁器所闩锁的位值“1”更新为感测值“0”,或将感测值“0”至一个或多个闩锁器。相对地,若存储器单元储存的位值为“1”,则感测节点上的放电感测电压v

sen

可以小于或等于阈值电压v

th

。据此,页面缓冲器可被用以维持(或保持)被一个或多个闩锁器闩锁的位值“1”。

[0153]

若感测节点上的电容值并不稳定且突然变化,例如趋近于阈值电压vth,则感测结果可能是错误的。若感测节点上的电容过小,预充电及放电阶段将无法完整执行以进行感

测。因此,页面缓冲器需要大且稳定的电容值,使感测节点上的电容能被完整地预充电或放电,进而实现精准的感测。

[0154]

在部分实施例中,晶体管(如mosfet)被应用为耦接于页面缓冲器的感测节点的电容(如,mos电容)。然而,具有高电容值的晶体管倾向于具有大体积因而会占用大面积,导致页面缓冲器的整体面积上升。

[0155]

在部分实施例中,页面缓冲器包含相同的多个闩锁单元。每个闩锁单元包含耦接于对应的感测晶体管及对应的耦合晶体管之间的闩锁器,其中感测晶体管及耦合晶体管皆耦接于感测节点。每个感测晶体管具有耦接于感测节点的栅极端,且能作为栅极电容。每个耦合晶体管具有耦接于感测节点的漏极端(或源极),且能作为结电容。代替在页面缓冲器中的mos电容器,页面缓冲器的感测节点上的等效电容由“关联于闩锁单元中对应的感测晶体管的栅极电容”、“关联于闩锁单元中对应的耦合晶体管的结电容”和“页面缓冲器中的金属线布线”来确定。

[0156]

图3所示为根据本公开内容的部分实施例中,结电容与栅极电容的电压电容的关系示意图300。当感测晶体管的栅极和源极之间的电压vgs变化时,结电容的电容值根据电容值-电压(capacitance-voltage;cv)曲线302变化、栅极电容的电容值根据cv曲线304变化。线306表示页面缓冲器的电压v

gs

的感测工作范围。cv曲线302和304表示在阈值电压v

th

附近,栅极电容的电容值比结电容的电容值有更大变化(如斜率变化)。因此,若栅极电容的数量与结电容器的数量的比值很大,例如等于1,则感测节点处的电容值可能在预定阈值电压v

th

附近有明显变化,而可能导致错误的感测结果。

[0157]

本公开内容提供具有大且稳定的电容值的页面缓冲器以侦测存储单元中储存的数据,例如:通过最小化页面缓冲器中栅极电容的影响。在部分实施例中,如图4所讨论的细节,页面缓冲器中的闩锁单元可被分类为至少两种电路:“感测闩锁电路”及“储存闩锁电路”。感测闩锁电路包含一个或多个闩锁单元,这一或多个闩锁单元耦接于感测晶体管,且其栅极连接于感测节点,以通过位线感测数据。一个或多个闩锁单元系共享(share)感测晶体管。储存闩锁电路并不加入感测,仅储存感测闩锁电路或快取数据闩锁电路(如图2所示的快取数据闩锁电路230)中的数据。因此,储存闩锁电路可不包含该感测晶体管。据此,将可最小化关联于页面缓冲器中感测晶体管的栅极电容的影响,以增加感测节点处的电容值的稳定性,从而提高页面缓冲器的感测精度和/或感测良率。

[0158]

在部分实施例中,页面缓冲器中这些闩锁单元的数量是根据存储器阵列的存储器单元的存储器单元类型所决定。举例而言,若存储器单元的存储器单元类型是slc,则存储器单元的页面缓冲器可包含两个闩锁单元。若存储器单元的存储器单元类型是mlc,则存储器单元的页面缓冲器可包含三个闩锁单元。若存储器单元的存储器单元类型是tlc,则存储器单元的页面缓冲器可包含五个闩锁单元。若存储器单元的存储器单元类型是qlc,则存储器单元的页面缓冲器可包含六个闩锁单元。仅用于举例说明,以下描述包含五个闩锁单元且适用于tlc的页面缓冲器。

[0159]

图4所示为根据本公开内容的部分实施例的页面缓冲器400示意图。页面缓冲器400可以由图2的页面缓冲器222来实现。页面缓冲器400包含五个闩锁单元440a、440b、460a、460b、460c,且这五个闩锁单元可被分类为两种电路:“感测闩锁电路430”及“储存闩锁电路450”。感测闩锁电路430用以通过位线401,感测存储器单元中储存的数据。储存闩锁

电路450用以储存感测闩锁电路430或快取数据闩锁电路(如图2所示的快取数据闩锁电路230)的数据。

[0160]

前述五个闩锁单元的每一个可具有相同结构。如第5图所示,闩锁单元500包含第一节点(如输入节点)502及第二节点(如输出节点)504。闩锁单元500包含闩锁器520。闩锁器520耦接于耦合电路510及闩锁控制电路530之间。耦合电路510耦接于第一节点,闩锁控制电路530耦接于第二节点。

[0161]

闩锁器520包含一对第一反相器522及第二反相器524。闩锁器520可为三态闩锁器或抑制闩锁器。第一反相器522用以接收对应的信号pos。第二反相器524用以接收对应的待命信号stb。对应于lb节点521的电压的数值,相反于对应于l节点523的电压的数值,其中lb节点521在反相器522、524之间,l节点523在反相器522、524之间。闩锁器520通过更新lb节点521及/或l节点523的数值,以储存数据。

[0162]

耦合电路510包含第一耦合晶体管512及第二耦合晶体管514。第一耦合晶体管512及第二耦合晶体管514皆可为n通道晶体管(nmos)。第一耦合晶体管512包含栅极端、漏极端及源极端,栅极端用以接收控制信号rd。漏极端耦接于第一节点502,源极端耦接于第二耦合晶体管514的漏极端。第二耦合晶体管514的源极端耦接于接地端且栅极端耦接于第一反相器522(如耦接于l节点523)。

[0163]

闩锁控制电路530包含闩锁设定晶体管532及闩锁重置晶体管534。闩锁设定晶体管532耦接于lb节点521及第二节点504之间。闩锁重置晶体管534耦接于l节点523及第二节点504之间。闩锁设定晶体管532的栅极用以接收设定信号s,其漏极端耦接于lb节点521、其源极耦接于第二节点504。闩锁重置晶体管534的栅极用以接收重置信号r、其漏极端耦接于l节点523其源极耦接于第二节点504。因此,闩锁设定晶体管532及闩锁重置晶体管534的源极皆耦接于感测节点504。

[0164]

对于本公开内容中的页面缓冲器,感测闩锁电路和储存闩锁电路中的任一个都包含至少一个闩锁单元。对于较少层级的存储器,例如slc或mlc,感测闩锁电路可以只具有一个闩锁单元。对于更高层级的存储器,例如tlc或qlc,感测闩锁电路可以包含一个或多个其他闩锁单元,用以执行快速写入(quick pass write;qpw)操作。举例而言:感测闩锁电路可以包含用于tlc和qlc的两个闩锁单元。储存闩锁电路中闩锁单元的数量是根据储存在存储器单元中的位值而定。例如,储存闩锁电路可包括一个用于slc的闩锁单元、两个用于mlc的闩锁单元、三个用于tlc的闩锁单元以及四个用于qlc的闩锁单元。

[0165]

复请参阅图4,对于tlc存储器单元来说,感测闩锁电路430包含两个感测闩锁单元(或感测闩锁器)440a、440b(在此通称为多个感测闩锁单元440或各自称为感测闩锁单元440)。储存闩锁电路450包括三个闩锁单元(或储存闩锁器)460a、460b、460c(在此通称为多个储存闩锁单元460或各自称为感测闩锁单元460)。

[0166]

感测闩锁电路430还包含感测晶体管432,其耦接于多个感测闩锁单元440,储存闩锁电路450并不包含感测晶体管。感测闩锁电路430及储存闩锁电路450中的闩锁器可为三态闩锁器、抑制闩锁器或任何适合类型的闩锁器。在部分实施例中,这些闩锁器为相同类型。在部分实施例中,由于感测闩锁电路430及储存闩锁电路450用以执行不同功能,例如感测数据相对于储存数据,因此感测闩锁电路430和储存闩锁电路450中的闩锁器亦可为不同类型。

[0167]

感测晶体管432的栅极端耦接于感测节点(sen)431、其源极端耦接于接地端,其漏极端耦接于感测闩锁单元440。感测晶体管432的功能用以作为栅极电容408。每个感测闩锁单元440的第一节点(如:图5所示的第一节点502)耦接于感测节点431。举例而言,感测闩锁单元440的耦合电路(如:图5所示的耦合电路510)中的第一耦合晶体管(如:图5所示的耦合晶体管)耦接于感测节点431。第一耦合晶体管的功能作为结电容406。每一个感测闩锁单元440的第二节点(如,图5所示的第二节点504)耦接于感测晶体管432的漏极端。举例而言,感测闩锁单元440的闩锁控制电路(如:图5所示的闩锁控制电路530)耦接于感测晶体管432的漏极端。感测闩锁电路430通过更新“dlb节点或l1b节点(如:图5所示的lb节点521)”的数值及/或“dl节点或l1节点(如:图5所示的l节点523)”的数值来感测数据。

[0168]

在部分实施例中,感测闩锁电路430包含放电晶体管434,其栅极用以接收放电信号、其源极耦接于接地端、其漏极端耦接于感测闩锁单元440,例如:感测闩锁单元440的第二节点。

[0169]

储存闩锁电路450包含三个可并联的储存闩锁单元460。每个储存闩锁单元460的第三节点(如图5所示的第一节点502)耦接于感测节点431,其第四节点(如图5所示的504)耦接于感测节点431。举例而言,储存闩锁单元460的耦合电路中的第一耦合晶体管(如图5所示的耦合晶体管512)耦接于感测节点431。因此,第一耦合晶体管的功能用以作为结电容406。相似地,储存闩锁单元460中闩锁控制电路的晶体管(如:图5所示的闩锁设定晶体管532及闩锁重置晶体管534)亦可耦接于感测节点431及感测晶体管432的栅极。因此,储存闩锁电路460的闩锁控制电路中的晶体管亦可作为结电容406。

[0170]

页面缓冲器400的感测节点431上的等效电容是基于栅极电容408、结电容406及页面缓冲器400的金属线布线而决定。如图4所示,感测闩锁单元440中的第一耦合晶体管、储存闩锁单元460的第一耦合晶体管及储存闩锁单元460的闩锁控制电路中的闩锁设定晶体管和闩锁重置晶体管中的每一个都可以作为结电容器406。相对地,只有一个感测晶体管432作为栅极电容408。因此,在页面缓冲器400中,栅极电容的数量与结电容的数量的比值能大幅降低,如:1/11。据此,感测晶体管432的电容值实质上会小于结电容406的整体电容值,且栅极电容对于等效电容(与等效电容值)的影响能被大幅抑制,增加了等效电容值在阈值电压v

th

(如:v

strobe

)附近的稳定性。

[0171]

在部分实施例中,如图4所示,页面缓冲器400包含预充电电路410及位线控制电路(或钳位电路)420。预充电电路410耦接于感测节点431。位线控制电路420的第一控制节点耦接于位线401,其第二控制节点耦接于感测节点431。图6a~6c及图7说明其细节如后:预充电电路410用以在预充电阶段时对感测节点431预充电。位线控制电路420用以在预充电阶段时,对位线401预充电,以及在预充电阶段后的放电阶段,使感测节点431放电。

[0172]

如图4所示,预充电电路包含两个p通道晶体管412和414(如pmos晶体管),其串联于供电电压vddi及感测节点431之间。晶体管412的源极端用以接收供电电压vddi、其栅极端用以接收预充电控制信号pre。晶体管414的栅极端用以接收预充电致能信号psen,其源极端耦接于晶体管412的漏极端,其漏极端耦接于感测节点431。

[0173]

如图4所示,位线控制电路420包含p通道晶体管422、三个n通道晶体管424、426、428及n通道晶体管427。p通道晶体管422用以接收供电电压vddi。n通道晶体管424、426、428用以分别接收位线控制信号blc1、blc2、blc3。n通道晶体管427用以耦接至接地端。晶体管

422的源极端用以接收供电电压vddi,其栅极端耦接于感测闩锁电路430,如:感测闩锁单元440a的闩锁器中的dlb节点。晶体管426的漏极端耦接于晶体管422的漏极端,其栅极端用以接收位线控制信号blc2,其源极端用以耦接于晶体管427的漏极端。晶体管427的源极端耦接于接地端,其栅极端耦接于晶体管422的栅极端。预充电电路410通过连接“晶体管412的漏极端及晶体管414的源极端之间”的节点及“晶体管422的漏极端及晶体管426的漏极端之间”的节点,以耦接于位线控制电路420。晶体管424的漏极端耦接于位线401,其栅极端耦接于晶体管426的源极端与晶体管427的漏极端之间的节点。晶体管428的漏极端耦接于晶体管424的源极端,其源极端耦接于感测节点431,其栅极端用以接收位线控制信号blc3.

[0174]

在部分实施例中,页面缓冲器400包含放电电路402,其包含放电晶体管404,如:n通道晶体管。放电晶体管404的漏极端耦接于晶体管424的漏极端,其栅极端用以接收放电信号disch,其源极端耦接于接地端。

[0175]

图6a~6c为图4所示的页面缓冲器于不同阶段(或步骤)中的电路示意图600、630、650,阶段包含预充电阶段(step 1)、放电阶段(step 2)及感测阶段(step 3)。图7所示为页面缓冲器400运作于图6a~6c的各阶段中,不同节点的电压变化时序图。

[0176]

最初,图6所示,在感测闩锁电路430中,感测闩锁单元440的dlb节点维持对应于位“0”的低电压(如:v

ss

),且在lb节点为对应于位“1”的高电压。p通道晶体管422在其栅极端耦接至dlb节点时导通,且n通道晶体管427在其栅极端耦接至dlb节点时关断。

[0177]

在预充电阶段时,如图6a及图7的step 1所示,晶体管414通过以其栅极端接收对应的信号psen(低电压电平)而导通。因此,预充电电路410会被导通,以将感测节点431从较低电压电平(如:对应于位“0”)预充电至较高电压电平(如:预设的感测电压)。感测节点431可通过晶体管422及晶体管414,沿着电流路径602自供电电压预充电。

[0178]

在预充电阶段时,n通道晶体管424、426通过接收对应的控制信号blc1、blc2而导通,n通道晶体管428则关断。因此,位线401将通过供电电压,经由晶体管422、426、424的电流路径604,预充电至预设的位线电压。当晶体管428关断时,位线会断开与感测节点431的连接。感测节点431上预设的感测电压可以高于位线401上预设的位线电压。

[0179]

在预充电阶段后的放电阶段时,如图6b及图7的step 2所示,晶体管414通过将其栅极端的信号psen从低电位改变至高电位而关断。因此,电流路径602也被关闭。据此,感测节点431不再被预充电电路410充电。相反地,晶体管428通过其栅极端接收致能信号blc3(高电压)而导通,且感测节点会与位线401电性连接。据此,感测节点431上预设的感测电压会通过提供至位线401的感测电流而放电,感测电流沿着电流路径632流经晶体管428、424而至位线401。

[0180]

在预充电阶段与放电阶段中,如图7所示,感测闩锁单元440的闩锁控制电路(如:图5所示的闩锁控制电路530)被关断,例如:通过在控制信号r0为低电平时维持闩锁重置晶体管(如:图5所示的闩锁重置晶体管534)关断。感测闩锁单元440的闩锁器中的第一反相器(如:图5所示的反相器522)通过接收低电平的信号pos0而导通。据此,储存于感测闩锁单元440中的位值(如,dl节点上的“1”)将会维持相同的数值。

[0181]

在放电阶段结束时,感测节点431上放电后的感测电压可以表示为电压v

sen

。感测闩锁单元440中闩锁的位值会根据放电后的感测电压v

sen

而决定。在放电阶段后的感测阶段(或选通阶段)时,闩锁控制电路会被导通,例如:通过将控制信号r0改变为高电平以导通闩

锁重置晶体管。感测闩锁单元440中的第一反相器会被关断,例如:通过将第一反相器的信号pos0改变为高电平。感测闩锁单元440中的第二反相器(如:图5所示的第二反相器524)可以被导通,使dl节点及dlb节点的位值为相反。

[0182]

当耦接于位线401的存储器单元所储存的位值为“1”时,电压v

sen

小于(或等于)阈值电压,例如:v

strobe

,且感测晶体管432被关断。因此,dl节点上的位值“1”会保持不变,以对应于存储器单元中储存的位值“1”。

[0183]

当耦接于位线的存储器单元所储存的位值为“0”时,电压v

sen

将大于阈值电压,以导通感测晶体管432。如第6c图及第7图所示的step 3,由于闩锁重置晶体管被导通,且dl节点上对应于位值“1”的高电位将会沿着电流路径652,被放电至对应于位值“0”的低电位。据此,dlb节点上的位值“0”将会通过感测闩锁单元440的第二反相器,被改变至位值“1”。因此,感测闩锁单元440中的闩锁器的dl节点上的位值“0”会被更新至对应于存储器单元中储存的位值“0”[0184]

在部分实施例中,储存闩锁电路450用以导通储存闩锁单元460中一个或多个闩锁控制电路,以在储存闩锁单元460中的一个或多个闩锁器写入感测结果,例如:在感测阶段,或于感测阶段后的储存阶段中。举例而言,为了储存感测结果“0”,储存闩锁单元460的闩锁控制电路(如:图5所示的闩锁控制电路530)将被导通,如:通过将控制信号s2从低电位改变至高电位。由于感测电大于阈值电压,储存闩锁单元460中闩锁器的l1b节点上对应于位值“0”的电压值将会被拉高(pull high)至对应于位值“1”的电压,且储存闩锁单元460中闩锁器的l1节点上对应于位值“1”的电压会被拉低(pull down)至对应于位值“0”的电压。

[0185]

图8用于说明根据本公开内容的部分实施例的管理存储器装置中页面缓冲电路的流程800。存储器装置可以是图1a所示的存储器116,或个为图2所示的存储器装置200。存储器装置包含存储器阵列,其具有多个存储器单元,例如图1b所示的存储器单元141或图1c所示的存储器单元157。存储器单元串联于多行(column)且连接于存储器单元线(如:位线)。页面缓冲电路可以是图2所示的页面缓冲电路220。页面缓冲电路包含多个页面缓冲器,例如图2所示的页面缓冲器222或图4所示的页面缓冲器400。每个页面缓冲器通过对应的位线,耦接于对应的存储器单元。每个页面缓冲器可被控制逻辑电路管理或控制,例如:图2所示的存储器装置中的控制逻辑电路204。流程800可以由管理页面缓冲器的控制逻辑电路来执行。

[0186]

页面缓冲器包含感测闩锁电路(如:图4所示的感测闩锁电路430)及储存闩锁电路(如:图4所示的储存闩锁电路450)。感测闩锁电路包含耦接于感测节点的感测晶体管(如:图4所示的感测晶体管432)(如:图4所示的感测节点431)及至少一个感测闩锁单元(如:图4所示的感测闩锁单元440)。至少一个感测闩锁单元的第一节点耦接于感测节点,且其第二节点耦接于感测晶体管。储存闩锁电路包含至少一个储存闩锁单元(如:图4所示的储存闩锁单元460),至少一个储存闩锁单元的第三节点及第四节点皆耦接于感测节点。感测晶体管的第一端(如漏极端)耦接于至少一个感测闩锁单元的第二节点,其栅极端耦接于感测节点及至少一个储存闩锁单元的第三节点及第四节,其第二端(如源极端)则耦接于接地端。

[0187]

感测闩锁电路及储存闩锁电路可以配置为具有感测用的电容(或具有等效电容),其关联于栅极电容(如:图4所示的栅极电容408)及感测闩锁电路与储存闩锁电路中的一个或多个寄生结电容(如:图4所示的结电容406)。栅极电容关联于感测晶体管。感测用的电容

还可以关联于感测闩锁电路及储存闩锁电路中的一个或多个金属布线。与结电容相比,栅极电容在阈值电压附近可以具有更大的电容值变化。

[0188]

在部分实施例中,储存闩锁电路并不包含感测晶体管。感测闩锁电路只包含一个感测晶体管。在部分实施例中,感测闩锁电路包含多个感测晶体管及多个感测闩锁单元,且感测晶体管的数量小于感测闩锁单元的数量。

[0189]

感测闩锁单元及储存闩锁单元可以具有相同类型的闩锁单元,如:图5所示的闩锁单元500。在部分实施例中,每个至少一个感测闩锁单元包含第一闩锁器(如图5所示的闩锁器520)及第一闩锁控制电路(如图5所示的闩锁控制电路530)。第一闩锁器具有第一反相器(如图5所示的反相器522和524)。第一闩锁控制电路耦接于第一闩锁器及感测晶体管的第一端。每个至少一个感测闩锁单元还可包含第一耦合电路(如图5所示的耦合电路510),第一耦合电路耦接于感测节点及第一闩锁器。

[0190]

在部分实施例中,每个至少一个储存闩锁单元包含第二闩锁器(如图5所示的闩锁器520)及第二闩锁控制电路(如图5所示的闩锁控制电路530)。第二闩锁器具有第二反相器(如图5所示的反相器522和524)。第二闩锁控制电路耦接于第二闩锁器及感测晶体管的栅极端。每个至少一个储存闩锁单元还可包含第二耦合电路(如图5所示的耦合电路510),第二耦合电路耦接于感测节点及第二闩锁器。

[0191]

在部分实施例中,感测闩锁单元包含第一类型的闩锁器,储存闩锁单元包含第二类型的闩锁器,其中第一类型的闩锁器与第二类型的闩锁器相异。第一类型的闩锁器及第二类型的闩锁器中的任一个可为三态闩锁器或抑制闩锁器。第一类型的闩锁器与第二类型的闩锁器相异。

[0192]

在部分实施例中,页面缓冲器还可包含预充电电路(如图4所示的预充电电路410)及位线控制电路(如图4所示的位线控制电路402)。预充电电路耦接于感测节点。位线控制电路的第一控制节点耦接于位线,其第二控制节点耦接于感测节点。页面缓冲器还可包含放电电路,例如图4所示的放电电路402,其耦接于位线控制电路。

[0193]

在部分实施例中,感测闩锁电路的至少一个感测闩锁单元的数量及储存闩锁电路中的至少一个储存闩锁单元的数量关连于存储器单元的存储器单元类型。储存闩锁电路的至少一个储存闩锁单元的数量可以根据存储器类型中所储存的位值数量来决定。感测闩锁电路包含两个或多个感测闩锁单元,例如用以快速写入(quick pass write;qpw)操作。

[0194]

在部分实施例中,存储器单元的存储器单元类型为slc,且感测闩锁电路包含一个感测闩锁单元,储存闩锁电路包含一个储存闩锁单元。在部分实施例中,存储器单元的存储器单元类型为mlc,且感测闩锁电路包含一个感测闩锁单元,储存闩锁电路包含两个储存闩锁单元。在部分实施例中,存储器单元的存储器单元类型为tlc,且感测闩锁电路包含两个感测闩锁单元,储存闩锁电路包含三个储存闩锁单元。在部分实施例中,存储器单元的存储器单元类型为qlc,且感测闩锁电路包含两个感测闩锁单元,储存闩锁电路包含四个储存闩锁单元。

[0195]

在步骤802中,在预充电阶段中,通过对应于位线的页面缓冲器,对耦接于存储器装置的存储器单元的位线预充电。举例而言,如图6a及图7所示,位线控制电路会被导通以沿着电流路径(如图6a所示的电流路径604)对位线预充电。位线控制电路包含多个晶体管,如图4所示的晶体管422、424、426、427、428。当控制信号blc2导通电晶体426且晶体管424被

控制信号导通时,位线控制电路可以被导通。位线控制电路用以断开位线至感测节点的导通连接,例如通过保持晶体管428为关断。

[0196]

在步骤804中,在预充电阶段中,对页面缓冲器的感测闩锁电路的感测节点预充电。举例而言,如图6a及图7所示,页面缓冲器的预充电电路会被导通而形成电流路径(如图6a所示的电流路径602),以将感测节点预充电至预设的感测电压。通过预充电致能信号psen导通耦接于感测节点的晶体管(如图4所示的晶体管414),预充电电路将可随的被导通。

[0197]

在步骤806中,在预充电阶段后的放电阶段中,通过连接于感测节点的位线,对感测节点上的预设的感测电压放电,以通过位线提供感测电流至存储器单元。举例而言,如图6b及图7所示,预充电电路被关断,以停止对感测节点充电(例如通过关断耦接于感测节点的晶体管)。感测节点将导通至位线,如通过导通位线控制电路中的晶体管428。预设的感测电压将大于位线电压。因此,电流路径(如电流路径632)将形成以放电感测节点的感测电压。在放电阶段结束时,放电后的感测电压将可被降低至电压v

sen

。

[0198]

在步骤808中,在放电阶段后的感测阶段中,根据感测节点上放电的感测电压,更新感测闩锁电路闩锁的数据。举例而言,如图6c及图7所示,感测闩锁电路中闩锁器的节点(如dl节点)的数据,且被感测闩锁电路闩锁的位值为“1”,且感测闩锁电路中闩锁器的另一节点(如:dlb节点)的位值为“0”。当感测阶段中,感测闩锁电路的闩锁控制电路将被导通。

[0199]

在部分实施例中,若存储器单元储存的位值为“1”、放电感测电压v

sen

小于或等于阈值电压(如图7所示的v

strobe

),则感测晶体管将被关断,且被感测闩锁电路中闩锁器闩锁的位值“1”会被保持固定不变,即对应于存储器单元所储存的位值“1”。

[0200]

在部分实施例中,若存储器单元储存的位值为“0”、放电感测电压v

sen

大于阈值电压,则感测晶体管将被导通,且被感测闩锁电路中闩锁器所闩锁的位值“1”将被改变为位值“0”,即对应于存储器单元中储存的位值“0”。

[0201]

在部分实施例中,在感测阶段或感测阶段后的储存阶段中,储存闩锁电路用以导通一个或多个闩锁控制电路,以在储存闩锁电路的一个或多个闩锁器中写入感测结果。在部分实施例中,被储存闩锁电路闩锁的数据还会被快取数据闩锁电路cdl(如图2所示)所快取。

[0202]

本公开内容的实施例可被实现为一个或多个计算机程序产品,例如一个或多个计算机程序指令模块,其被编码于一种计算机可读取媒体上,用以由数据处理设备执行或控制其操作。计算机可读存储介质可以是可读写储存装置(machine-readable storage device)、可读写储存基板(machine-readable storage substrate)、存储器或以上的一个或多个的组合。前述“数据处理设备”包含处理数据数据的所有装置、设备和机器,例如可编程处理器、计算机或多个处理器或计算机。除了硬件之外,数据处理设备还可以包含计算机程序建立以执行环境的代码,例如,构成处理器固件、协定栈(protocol stack)、数据库管理系统、操作系统或一种或多种的组合的代码。

[0203]

系统可以涵盖用于处理数据的所有装置、设备和机器,包括例如可编程处理器、计算机或多个处理器或计算机。除了硬件之外,数据处理设备还可以包含计算机程序建立以执行环境的代码,例如,构成处理器固件、协定栈(protocol stack)、数据库管理系统、操作系统或一种或多种的组合的代码。

[0204]

计算机程序(或称为程序、软件、应用程序、脚本或代码)可以任何形式的编程语言编写,包括编译或解释语言,并且它可以以任何形式部署,包括作为独立程序或作为模块、元件、子程序或其他适合在运算环境中使用的单元。计算机程序不一定对应于文件系统中的文件。计算机程序可以储存在包含其他程序或数据的文件的一部分中(例如,储存在标记语言文档中的一个或多个脚本)、专用于所讨论程序的单个文件或多个协调文件(例如储存一个或多个模块、子程序或部分代码的文件)。计算机程序可以部署以于一台或多台计算机上执行,以位于一个站点或分布在多个站点,且连接至通讯网路。

[0205]

本公开内容中描述的流程与逻辑可由一个或多个可编程处理器执行,处理器执行一个或多个计算机程序以执行本公开内容所描述的功能。流程与逻辑也可以由专用逻辑电路执行,并且数据处理设备也可以实现为专用逻辑电路,例如现场可编程逻辑门阵列(field programmable gate array;fpga)或特殊应用集成电路(application specific integrated circuit;asic)。

[0206]

适合于执行计算机程序的处理器包括,例如通用和专用微处理器,以及任何类型的数据计算机中的任何一个或多个处理器。一般言,处理器将从只读存储器、随机存取存储器或两个接收指令和数据。计算机的基本元件可以包括用于执行指令的处理器和用于储存指令和数据的一个或多个存储器装置。一般言,计算机还可以包括或可操作地耦合以从一个或多个用于储存数据的大容量存储器装置(例如,磁存储器、磁光存储器或光碟)接收、传输数据或两个。然而,前述设备并非必须。适用于储存计算机程序指令和数据的可读取媒体可以包括所有形式的非易失性存储器和存储器装置,例如半导体储存装置的eprom、eeprom,以及快取存储器、光盘等。处理器和存储器可以由专用逻辑电路实现,或结合在专用逻辑电路中。

[0207]

虽然本公开内容中描述了许多细节,但这些细节不应被解释为对于权利要求范围或主张保护内容的限制,而仅是用于描述特定实施例的特有特征。本公开内容的单独实施例的上下文所中描述的各个特征,其亦可在其他的单个实施例中组合实施。相对地,在单个实施例的上下文中描述的各种特征,其亦可在多个实施例中单独、或以任何合适的子组合来实施。此外,尽管部分特征是作用于特定组合,但在其他情况下,这些组合限制可以被删除,且一个保护组合中的一个或多个特征可以指向至其他子组合或子组合的变体。同理,虽然在附图中以特定顺序描述运作方式,但这不应被理解为本公开内容需依此特定顺序执行,且不应被理解为附图中的所有运作,方能实现其功能。

[0208]

虽然本公开内容已以实施方式公开如上,然其并非用以限定本公开内容,任何本领域技术人员,在不脱离本公开内容的精神和范围内,当可作各种更动与润饰,因此本公开内容的保护范围当视随附的权利要求书范围所界定的为准。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。