1.本发明涉及将低电压侧的信号向基准电位不同的高电压侧传输的电平移位电路。

背景技术:

2.hvic(high voltage mos gate driver ic)等功率器件控制用ic是通过来自微型计算机等的输入信号对开关器件的栅极进行驱动的高耐压ic。hvic例如像在专利文献1的图1中示出的那样,具有对高电压侧(高电位侧)的开关器件进行驱动的高电位侧栅极驱动电路和对低电压侧(低电位侧)的开关器件进行驱动的低电位侧栅极驱动电路。

3.高电位侧栅极驱动电路具有将低电压侧的信号向基准电位不同的高电压侧传输的高压电平移位电路。高压电平移位电路将以接地电位(gnd)为基准的初级侧电路的电压信号通过高耐压mosfet(metal oxide semiconductor field effect transistor)转换为电流信号,向以浮置电位为基准的次级侧电路传输电流信号。传输来的电流信号通过次级侧电路而被恢复为电压信号。

4.更具体而言,高电位侧栅极驱动电路如果被输入了与高电位侧输入信号的上升同步的接通脉冲,则高压电平移位电路的高耐压mosfet的栅极电位从gnd变动至初级侧电路的电源电位,栅极-源极间变为开状态,从而成为接通状态。在接通的期间,电流经由高耐压mosfet从次级侧电路的电源流向初级侧电路的gnd。对于该电流,通过在次级侧电路设置的电阻元件而将电流信号转换为电压信号,由此向次级侧电路传输电流信号。如果被输入了与高电位侧输入信号的下降同步的断开脉冲,则高压电平移位电路的高耐压mosfet的栅极电位从初级侧电路的电源电位变动至gnd,栅极-源极间变为闭状态,从而成为断开状态。

5.专利文献1:日本特开2018-196276号公报

6.在以上所说明的现有的高压电平移位电路的情况下,在次级侧电路的电源变得小于或等于gnd的情况下,传输信号源即从次级侧电路流向初级侧电路的电流衰减,有可能产生无法进行信号传输的现象。

技术实现要素:

7.本发明就是为了解决上述这样的问题而提出的,其目的在于,提供即使在次级侧电路的电源变得小于或等于gnd的情况下也能够传输信号的电平移位电路。

8.本发明涉及的电平移位电路具有:第1导电型的电平移位晶体管,其在以初级侧基准电位为基准的初级侧电路与以独立于所述初级侧基准电位的次级侧基准电位为基准的次级侧电路之间,将来自所述初级侧电路的信号向所述次级侧电路进行电平移位;二极管,其正向地连接在所述电平移位晶体管的第1主电极与所述次级侧电路之间;电容器,其与所述二极管并联连接;以及反相器,其使所述信号反转,所述电平移位晶体管的控制电极与所述初级侧电路的初级侧电源连接,第2主电极与所述反相器的输出连接,所述反相器在所述初级侧基准电位与所述初级侧电源之间进行动作,所述二极管经由电阻元件而与所述次级侧电路的次级侧电源连接。

9.发明的效果

10.根据本发明涉及的电平移位电路,在次级侧电源小于或等于初级侧基准电位的情况下,如果电平移位晶体管成为接通状态,则电容器的初级侧电路侧的电极的电位下降至初级侧基准电位。在发生了下降的瞬间,试图使电容器的2个电极的电位继续得到保持,因此,电容器的次级侧电路侧的电极的电位也随之下降。下降的量的电压施加于电阻元件,因此,能够向次级侧电路传输信号。

附图说明

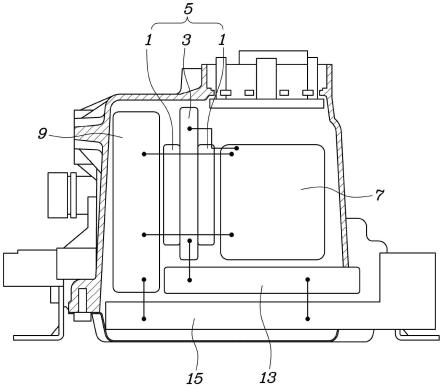

11.图1是表示组装有本发明涉及的高压电平移位电路的hvic的结构的图。

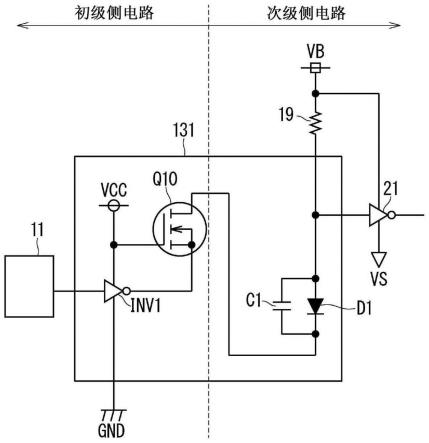

12.图2是表示本发明涉及的实施方式1的高压电平移位电路的结构的电路图。

13.图3是表示本发明涉及的实施方式1的高压电平移位电路的结构的电路图。

14.图4是表示本发明涉及的实施方式2的高压电平移位电路的结构的电路图。

15.图5是表示本发明涉及的实施方式2的高压电平移位电路的结构的电路图。

16.图6是表示本发明涉及的实施方式3的高压电平移位电路的结构的电路图。

17.图7是表示本发明涉及的实施方式3的高压电平移位电路的结构的电路图。

具体实施方式

18.<hvic的结构>

19.图1是表示组装有本发明涉及的高压电平移位电路的hvic 100的结构的图。hvic 100具有对高电位侧开关器件q1进行驱动的高电位侧栅极驱动电路101和对低电位侧开关器件q2进行驱动的低电位侧栅极驱动电路102。高电位侧开关器件q1和低电位侧开关器件q2都是n沟道型mosfet,分别反向并联连接有续流二极管p1、p2。此外,在图1中,高电位侧开关器件q1及低电位侧开关器件q2是mosfet,但也能够使用igbt(insulated gate bipolar transistor)。

20.以下,对高电位侧栅极驱动电路101的结构进行说明。高电位侧栅极驱动电路101具有接通脉冲生成电路11、断开脉冲生成电路12、高压电平移位电路13、高压电平移位电路14、电阻元件19、电阻元件20、not门21、not门22、锁存电路24及输出电路25。

21.输入至高电位侧栅极驱动电路101的高电位侧输入信号hin被输入至接通脉冲生成电路11和断开脉冲生成电路12。接通脉冲生成电路11生成定时(timing)与高电位侧输入信号hin的上升同步的接通脉冲。断开脉冲生成电路12生成定时与高电位侧输入信号hin的下降同步的断开脉冲。

22.接通脉冲生成电路11的输出与高压电平移位电路13内的电平移位用的高耐压mosfet的栅极连接。该高耐压mosfet的漏极经由电阻元件19被固定于次级侧电路的电源(称为“次级侧电源”)即高电位侧电源电压vb,并且经由not门21与锁存电路24的输入端子连接。高耐压mosfet的源极与初级侧电路的基准电位(称为“初级侧基准电位”)即接地电位gnd连接。此外,有时将高电位侧电源电压vb称为高电位侧电源vb,将接地电位gnd简单地记作gnd。

23.断开脉冲生成电路12的输出与高压电平移位电路14内的电平移位用的高耐压mosfet的栅极连接。该高耐压mosfet的漏极经由电阻元件20而被固定于高电位侧电源电压

vb,并且经由not门22与锁存电路24的输入端子连接。高耐压mosfet的源极与接地电位gnd连接。此外,高压电平移位电路13及14的具体结构会在后面进行说明。

24.锁存电路24由rs触发电路等构成,对来自not门21及22的输出进行锁存而输出至输出电路25。

25.输出电路25根据锁存电路24的输出,将向输出端子u

out

的输出电压在成为次级侧电路的基准电位(称为“次级侧基准电位”)的高电位侧电源电压vb与高电位侧浮置电位vs之间进行切换。

26.<实施方式1>

27.<装置结构>

28.图2是表示本发明涉及的实施方式1的高压电平移位电路131的结构的电路图。此外,以下,以电平移位晶体管即高耐压mosfet q10为边界,将接通脉冲生成电路11侧称为初级侧电路,将not门21侧称为次级侧电路。此外,高压电平移位电路131是与图1所示的高压电平移位电路13对应的电路。

29.如图2所示,成为以下结构,即,在高压电平移位电路131的高耐压mosfet q10的栅极连接初级侧电路的电源(称为“初级侧电源”)即低电位侧电源vcc,向源极经由反相器inv1而提供从接通脉冲生成电路11输出的接通脉冲。此外,有时将从低电位侧电源vcc供给的电压称为低电位侧电源电压vcc。

30.反相器inv1在从低电位侧电源vcc供给的低电位侧电源电压vcc与gnd之间进行动作。

31.高耐压mosfet q10的漏极与正向二极管d1的阴极连接。向正向二极管d1并联连接有电容器c1。

32.成为正向二极管d1的阳极经由电阻元件19与高电位侧电源vb连接的结构。另外,正向二极管d1的阳极还与not门21的输入连接。not门21在高电位侧电源电压vb与高电位侧浮置电位vs之间进行动作。

33.图3是表示实施方式1的高压电平移位电路141的结构的电路图。此外,高压电平移位电路141是与图1所示的高压电平移位电路14对应的电路。

34.高压电平移位电路141的结构与图2所示的高压电平移位电路131相同,仅与初级侧电路及次级侧电路之间的连接关系不同。即,成为如下结构,即,向高压电平移位电路141的高耐压mosfet q10的源极经由反相器inv1而提供从断开脉冲生成电路12输出的断开脉冲,向正向二极管d1的阳极经由电阻元件20而提供高电位侧电源电压vb。另外,正向二极管d1的阳极还与not门22的输入连接。not门22在高电位侧电源电压vb与高电位侧浮置电位vs之间进行动作。

35.<动作>

36.以下,对高压电平移位电路131的动作进行说明,但高压电平移位电路141的动作也是相同的,因而省略动作说明。

37.作为初始状态,设为向反相器inv1的输入提供低电平的信号即小于或等于反相器inv1的阈值电压的电压的状态。这里,小于或等于反相器inv1的阈值电压的电压是指,在构成反相器inv1的p沟道型mosfet与n沟道型mosfet的串联连接中,小于或等于n沟道型mosfet的阈值电压且比p沟道型mosfet的阈值电压高的电压。在该状态下,p沟道型mosfet

接通,低电位侧电源电压vcc与高耐压mosfet q10的源极连接,高耐压mosfet q10的栅极电位和源极电位变得与低电位侧电源电压vcc相等,高耐压mosfet q10处于断开状态。

38.接下来,如果高电平的信号被输入至反相器inv1的输入,则构成反相器inv1的p沟道型mosfet截止,n沟道型mosfet导通,高耐压mosfet q10的源极电位下降至gnd,高耐压mosfet q10成为接通状态。此时,在高电位侧电源电压vb高于gnd的情况下,电流从高电位侧电源vb流向高耐压mosfet q10,因此,在电阻元件19产生电压信号δv,向次级侧电路传输信号。

39.另一方面,在高电位侧电源电压vb小于或等于gnd的情况下,如果高耐压mosfet q10成为接通状态,则电容器c1的初级侧电路侧的电极的电位下降至gnd。在发生了下降的瞬间,试图使电容器c1的2个电极的电位继续得到保持,因此,电容器c1的次级侧电路侧的电极的电位也随之下降。如果将下降的量的电压设为δv,则对电阻元件19施加电压δv,因此,向次级侧电路传输信号。然后,电压δv按照由电容器c1和电阻元件19实现的rc电路的时间常数而逐渐下降,电容器c1的次级侧电路侧的电极上升至高电位侧电源电压vb。此时,暂态地流过漏极电流。

40.另外,在高电位侧电源电压vb变得小于或等于gnd的情况下,电流有可能从高耐压mosfet q10的漏极侧流至背栅(gnd),但电流被二极管d1切断。

41.这样,就实施方式1的高压电平移位电路131而言,即使在次级侧电路的高电位侧电源电压vb下降至小于或等于gnd的情况下,也能够向次级侧电路传输信号。

42.<实施方式2>

43.<装置结构>

44.图4是表示本发明涉及的实施方式2的高压电平移位电路132的结构的电路图。此外,在图4中,对与使用图2说明过的高压电平移位电路131相同的结构标注相同的标号,省略重复的说明。此外,高压电平移位电路132是与图1所示的高压电平移位电路13对应的电路。

45.如图4所示,在高压电平移位电路132中,设置有在高耐压mosfet q10的源极与gnd之间连接的p沟道型的mosfet q11,向mosfet q11的栅极提供低电位侧电源电压vcc。

46.图5是表示实施方式2的高压电平移位电路142的结构的电路图。高压电平移位电路142的结构与图4所示的高压电平移位电路132相同,另外,与初级侧电路及次级侧电路之间的连接关系与图3所示的高压电平移位电路131相同。

47.<动作>

48.以下,对高压电平移位电路132的动作进行说明,但高压电平移位电路142的动作也是相同的,因而省略高压电平移位电路142的动作说明。

49.首先,考虑使用高压电平移位电路131,高电位侧浮置电位vs急剧地增大的情况,即,高电位侧浮置电位vs与gnd之间的电位急剧地增大而产生了正的电压变化( dv/dt)的情况。

50.此时,从次级侧电路向初级侧电路流过位移电流。位移电流根据向高压电平移位电路131的输入的状态而进行以下的举动。

51.首先,在向反相器inv1输入了高电平的信号的情况下,构成反相器inv1的n沟道型mosfet接通,位移电流经由n沟道型mosfet而流至gnd。

52.接下来,在向反相器inv1输入了低电平的信号的情况下,构成反相器inv1的n沟道型mosfet断开,反相器inv与gnd之间成为高阻抗,成为电流难以流向gnd的状态。因此,就位移电流而言,电流有可能经由在构成反相器inv1的p沟道型mosfet的本体寄生的二极管而从p沟道型mosfet的漏极侧流向背栅(gnd)。

53.另一方面,高压电平移位电路132如图4所示在高耐压mosfet q10的源极与gnd之间设置有p沟道型的mosfet q11,在向反相器inv1输入了低电平的信号的状态下,mosfet q11处于断开状态。

54.另一方面,反相器inv1与gnd之间成为高阻抗,成为电流难以流向gnd的状态,但如果在此时产生 dv/dt,则能够从次级侧电路向初级侧电路流过位移电流,由此,mosfet q11的源极侧的电位上升,常关的mosfet q11导通,经由mosfet q11而使位移电流流至gnd。

55.这样,实施方式2的高压电平移位电路132能够使在高电位侧浮置电位vs急剧地增大的情况下产生的位移电流与输入的状态无关地释放至初级侧基准电位即gnd,能够抑制由位移电流引起的故障的发生。

56.此外,在高压电平移位电路132中,即使在次级侧电路的高电位侧电源电压vb下降至小于或等于gnd的情况下,也能够向次级侧电路传输信号。

57.<实施方式3>

58.<装置结构>

59.图6是表示本发明涉及的实施方式3的高压电平移位电路133的结构的电路图。此外,高压电平移位电路133是与图1所示的高压电平移位电路13对应的电路。

60.如图6所示,高压电平移位电路133的高耐压mosfet q10的栅极与初级侧电路的低电位侧电源vcc连接,在高耐压mosfet q10的栅极与源极之间连接有p沟道型的mosfet q16。另外,成为如下结构,即,在高耐压mosfet q10的源极与gnd之间连接有n沟道型的mosfet q15,p沟道型的mosfet q16截止,mosfet q15导通,从而高耐压mosfet q10导通。

61.成为向mosfet q16的栅极经由串联连接的反相器inv2及inv3而提供从接通脉冲生成电路11输出的接通脉冲的结构。此外,尽管省略图示,但反相器inv2及inv3在低电位侧电源电压vcc与gnd之间进行动作。

62.高耐压mosfet q10的漏极与正向二极管d1的阴极连接。向正向二极管d1并联连接有电容器c1。

63.成为正向二极管d1的阳极经由电阻元件19与高电位侧电源vb连接的结构。另外,正向二极管d1的阳极还与not门21的输入连接。

64.另外,在低电位侧电源vcc与gnd之间串联连接有p沟道型的mosfet q12、电阻元件r1及n沟道型的mosfet q13,在mosfet q12及mosfet q13的栅极连接有反相器inv2的输出。

65.另外,在电阻元件r1和mosfet q13之间的连接点与gnd之间连接有n沟道型的mosfet q14。mosfet q14的栅极与mosfet q15的栅极共通地连接于电阻元件r1与mosfet q13之间的连接点。mosfet q15构成电流镜电路的初级侧,电阻元件r1及mosfet q14构成电流镜电路的次级侧。

66.图7是表示实施方式3的高压电平移位电路143的结构的电路图。此外,高压电平移位电路143是与图1所示的高压电平移位电路14对应的电路。

67.高压电平移位电路143的结构与图2所示的高压电平移位电路133相同,仅是与初

级侧电路及次级侧电路之间的连接关系不同。即,成为如下结构,即,向高压电平移位电路143的mosfet q16的栅极经由串联连接的反相器inv2及inv3而提供从断开脉冲生成电路12输出的断开脉冲,正向二极管d1的阳极经由电阻元件20与高电位侧电源vb连接。另外,正向二极管d1的阳极还与not门22的输入连接。

68.<动作>

69.以下,对高压电平移位电路133的动作进行说明,但高压电平移位电路143的动作也是相同的,因而省略高压电平移位电路143的动作说明。

70.作为初始状态,设为向反相器inv2的输入提供低电平的信号,即小于或等于反相器inv2的阈值电压的电压的状态。这里,小于或等于反相器inv2的阈值电压的电压的定义与在实施方式1中说明过的小于或等于反相器inv1的阈值电压的电压的定义相同。

71.如果低电平的信号被输入至反相器inv2的输入,则反相器inv2输出高电平的信号。由于反相器inv2所输出的高电平的信号,mosfet q13导通,但mosfet q12截止,因而电流镜电路不进行动作。反相器inv2所输出的高电平的信号被输入至反相器iv3,反相器iv3输出低电平的信号,mosfet q16导通。但是,mosfet q15不导通,因而高耐压mosfet q10处于断开状态。

72.接下来,如果高电平的信号被输入至反相器inv2的输入,则反相器inv2输出低电平的信号。通过反相器inv2所输出的低电平的信号,mosfet q12导通,但mosfet q13截止。反相器inv2所输出的低电平的信号被输入至反相器iv3,反相器iv3输出高电平的信号,mosfet q16截止,低电位侧电源vcc与高耐压mosfet q10的源极之间的连接被断开。

73.这里,在mosfet q14和mosfet q15具有同等能力的情况下,mosfet q14的漏极电流与mosfet q15的漏极电流相同。由于mosfet q15的漏极电流是高耐压mosfet q10的漏极电流,因此,与mosfet q14的漏极电流即流过电阻元件r1的电流同等。即,能够限制高电平的信号被输入至反相器inv2的输入时的高耐压mosfet q10的漏极电流。

74.这样,实施方式3的高压电平移位电路133具有电流镜电路,由此能够限制高耐压mosfet q10的漏极电流,能够限制流过高耐压mosfet q10的过电流。

75.此外,在高压电平移位电路133中,即使在次级侧电路的高电位侧电源电压vb下降至小于或等于gnd的情况下,也能够向次级侧电路传输信号。

76.此外,本发明能够在本发明的范围内对各实施方式自由地进行组合,或对各实施方式适当地进行变形、省略。

77.标号的说明

78.c1电容器,d1二极管,gnd接地电位,iv1、iv2、iv3反相器,q10高耐压mosfet,q11、q12、q13、q14、q15、q16 mosfet,vb高电位侧电源,vcc低电位侧电源,vs高电位侧浮置电位。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。