技术特征:

1.一种非易失性存储器件,所述非易失性存储器件包括:第一芯片,所述第一芯片包括第一衬底和外围电路区域,所述外围电路区域包括被配置为控制所述非易失性存储器件的操作模式的第一控制逻辑电路,其中,所述外围电路区域被布置在所述第一衬底的第一表面上;以及第二芯片,所述第二芯片包括第二衬底和非易失性存储单元的三维阵列,其中,所述三维阵列被布置在所述第二衬底的第一表面上,所述第二芯片垂直堆叠在所述第一芯片上,使得所述第一衬底的所述第一表面面对所述第二衬底的所述第一表面,其中,所述第二芯片还包括第二控制逻辑电路,所述第二控制逻辑电路被配置为控制所述非易失性存储器件的操作条件并且被布置在所述第二衬底的第二表面上,所述第二衬底的所述第二表面与所述第二衬底的所述第一表面相对。2.根据权利要求1所述的非易失性存储器件,其中,所述第二控制逻辑电路包括调度器,所述调度器被配置为根据所述非易失性存储器件的所述操作模式,控制控制信号的电压电平、施加时间点和施加时间段中的至少一者。3.根据权利要求1所述的非易失性存储器件,其中,形成在所述第一芯片的最上金属层上的第一接合金属电接合到形成在所述第二芯片的最上金属层上的第二接合金属。4.根据权利要求1所述的非易失性存储器件,其中,所述第二控制逻辑电路形成在被设置在所述第二衬底的所述第二表面上的多晶硅层的表面上。5.根据权利要求1所述的非易失性存储器件,其中,被配置为控制所述非易失性存储器件的存储器控制器中的电路中的至少一个电路被布置在所述第二衬底的所述第二表面上。6.一种存储装置,所述存储装置包括:非易失性存储器件,所述非易失性存储器件包括非易失性存储单元;以及存储器控制器,所述存储器控制器被配置为控制所述非易失性存储器件,其中,所述非易失性存储器件包括:第一芯片,所述第一芯片包括第一衬底和外围电路区域,所述外围电路区域包括被配置为控制所述非易失性存储器件的操作模式的第一控制逻辑电路,其中,所述外围电路区域被布置在所述第一衬底的第一表面上;以及第二芯片,所述第二芯片包括第二衬底和所述非易失性存储单元的三维阵列,其中所述三维阵列被布置在所述第二衬底的第一表面上,所述第二芯片垂直堆叠在所述第一芯片上,使得所述第一衬底的所述第一表面面对所述第二衬底的所述第一表面,其中,所述存储器控制器包括:第三芯片,所述第三芯片包括第三衬底和控制电路区域,所述控制电路区域包括被配置为设置并改变所述非易失性存储器件的操作条件的第一电路,其中,所述控制电路区域被布置在所述第三衬底的第一表面上,并且其中,所述第二芯片还包括第二控制逻辑电路,所述第二控制逻辑电路被配置为控制所述非易失性存储器件的所述操作条件并且被布置在所述第二衬底的第二表面上,所述第

二衬底的所述第二表面与所述第二衬底的所述第一表面相对。7.根据权利要求6所述的存储装置,其中,所述第二控制逻辑电路包括被配置为设置并改变所述非易失性存储器件的所述操作条件的第二电路,其中,所述第二电路被布置在所述第二衬底的所述第二表面上。8.根据权利要求7所述的存储装置,其中,所述存储器控制器还包括:处理器,所述处理器被配置为控制所述存储器控制器的操作;以及随机存取存储器,所述随机存取存储器包括所述存储器控制器的工作存储器,其中,所述处理器作为所述第一电路之一被布置在所述第三衬底的所述第一表面上,并且其中,所述随机存取存储器作为所述第二电路之一被布置在所述第二衬底的所述第二表面上。9.根据权利要求8所述的存储装置,其中,所述存储器控制器还包括:存储器管理部件,所述存储器管理部件被配置为基于所述非易失性存储器件的劣化状态改变所述非易失性存储器件的所述操作条件,并且其中,所述存储器管理部件作为所述第二电路之一被布置在所述第二衬底的所述第二表面上。10.根据权利要求9所述的存储装置,其中,所述存储器管理部件存储表示所述非易失性存储器件的所述劣化状态的劣化信息,所述劣化信息包括编程/擦除循环数、擦除计数、编程计数、读取计数、损耗水平计数、使用时间和工作温度当中的至少一者。11.根据权利要求10所述的存储装置,其中,所述存储器管理部件基于所述非易失性存储器件的所述劣化信息生成训练数据,并且基于所述训练数据获得所述非易失性存储器件的所述操作条件。12.根据权利要求8所述的存储装置,其中,所述存储器控制器还包括纠错码处理部件,所述纠错码处理部件被配置为检测并纠正在所述非易失性存储器件与所述存储器控制器之间传输的数据的错误,并且其中,所述纠错码处理部件作为所述第二电路之一被布置在所述第二衬底的所述第二表面上。13.根据权利要求6所述的存储装置,其中,所述第二控制逻辑电路包括调度器,所述调度器被配置为根据所述非易失性存储器件的操作模式,控制控制信号的电压电平、施加时间点和施加时间段中的至少一者。14.根据权利要求6所述的存储装置,其中,所述非易失性存储器件还包括形成在所述第一芯片的最上金属层上的第一接合金属,所述第一接合金属电连接到形成在所述第二芯片的最上金属层上的第二接合金属。15.一种存储装置,所述存储装置包括:非易失性存储器件,所述非易失性存储器件包括非易失性存储单元;以及存储器控制器,所述存储器控制器被配置为控制所述非易失性存储器件,

其中,所述非易失性存储器件包括:第一芯片,所述第一芯片包括第一衬底和外围电路区域,所述外围电路区域包括被配置为控制所述非易失性存储器件的操作模式的第一控制逻辑电路,其中,所述外围电路区域被布置在所述第一衬底的第一表面上;以及第二芯片,所述第二芯片包括第二衬底和所述非易失性存储单元的三维阵列,其中,所述三维阵列被布置在所述第二衬底的第一表面上,所述第二芯片垂直堆叠在所述第一芯片上,使得所述第一衬底的所述第一表面面对所述第二衬底的所述第一表面,其中,包括所述存储器控制器所包括的电路中的至少一个电路的控制电路区域形成在所述第二衬底的第二表面上,所述第二衬底的所述第二表面与所述第二衬底的所述第一表面相对。16.根据权利要求15所述的存储装置,其中,所述第二芯片还包括第二控制逻辑电路,所述第二控制逻辑电路被配置为控制所述非易失性存储器件的操作条件并且被布置在所述第二衬底的所述第二表面上。17.根据权利要求16所述的存储装置,其中,所述第二控制逻辑电路包括调度器,所述调度器被配置为根据所述非易失性存储器件的所述操作模式,控制控制信号的电压电平、施加时间点和施加时间段中的至少一者。18.根据权利要求16所述的存储装置,还包括:随机存取存储器,所述随机存取存储器包括被布置在所述第二衬底的所述第二表面上的所述存储器控制器的工作存储器,其中,所述第二控制逻辑电路还被配置为访问所述随机存取存储器。19.根据权利要求15所述的存储装置,还包括:处理器,所述处理器被配置为控制被布置在所述第二衬底的所述第二表面上的所述存储器控制器的操作。20.根据权利要求15所述的存储装置,还包括:纠错码处理部件,所述纠错码处理部件被配置为检测并纠正与所述非易失性存储器件相关的数据的错误,并且被布置在所述第二衬底的所述第二表面上。

技术总结

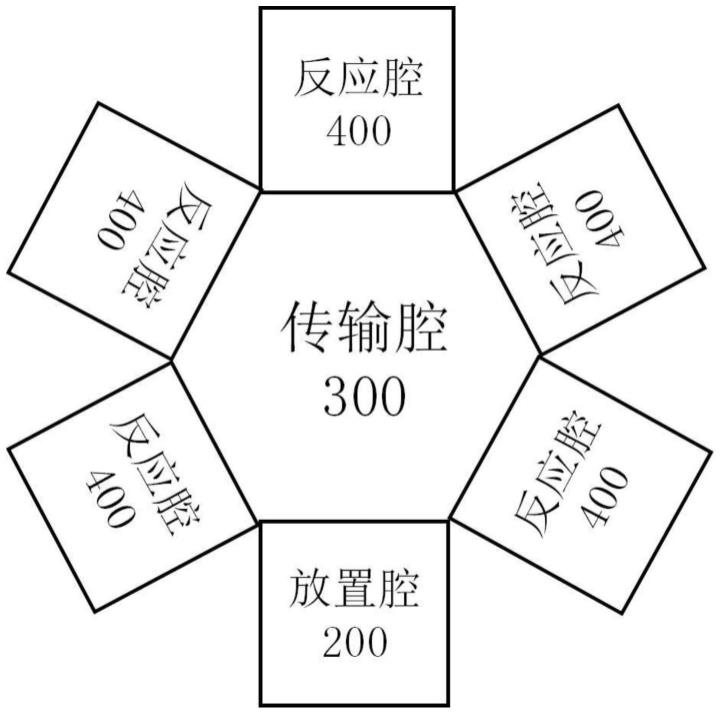

提供的是一种非易失性存储器件及包括其的存储装置。所述存储装置包括:第一芯片,所述第一芯片包括第一衬底和外围电路区域,所述外围电路区域包括被配置为控制所述非易失性存储器件的操作模式的第一控制逻辑电路;以及第二芯片,所述第二芯片包括第二衬底和非易失性存储单元的三维阵列。所述第二芯片可以垂直堆叠在所述第一芯片上,使得所述第一衬底的第一表面面对所述第二衬底的第一表面,并且所述第二芯片还可以包括第二控制逻辑电路,所述第二控制逻辑电路被配置为控制所述非易失性存储器件的操作条件并且被布置在所述第二衬底的第二表面上,所述第二衬底的所述第二表面与所述第二衬底的所述第一表面相对。述第二衬底的所述第一表面相对。述第二衬底的所述第一表面相对。

技术研发人员:吴银珠 张炳哲 昔浚荣 宋英杰 任峻成

受保护的技术使用者:三星电子株式会社

技术研发日:2022.07.27

技术公布日:2023/2/17

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。