1.本发明是关于一种软性电路板,特别是关于一种软性电路板的布线结构。

背景技术:

2.软性电路板具有体积小、具有可挠性、厚度薄的特性,已被广泛地应用于手机、笔记型电脑、智能手表

…

等移动装置上,由于当前移动装置皆朝向轻薄的目标发展,使得软性电路板的厚度及整体尺寸被要求得更加薄、小,但这也意味着软性电路的制程将更加困难。一般软性电路板是使用覆晶制程将芯片设置于软性基板上,而覆晶制程是利用加热及加压使得芯片的凸块与线路层共晶连接,这使得在覆晶制程中芯片的凸块会在软性基板的接触区域产生应力,将会对线路层产生拉扯而导致线路的断裂。

技术实现要素:

3.本发明的主要目的在于借由抗应力线路层加强软性基板与凸块连接的区域,以避免该区域的接合线路因为覆晶制程产生的应力断裂。

4.本发明的一种软性电路板的布线结构包含软性基板、线路层、覆晶元件及抗应力线路层,该软性基板具有上表面,该上表面具有芯片设置区及线路设置区,该线路层具有多个接合线路及多个传输线路,所述接合线路设置于该芯片设置区,所述传输线路设置于该线路设置区,且各该传输线路连接各该接合线路,该覆晶元件设置于该芯片设置区,该覆晶元件具有芯片及多个凸块,该芯片具有长边边缘及多个导接垫,各该凸块连接该芯片的各该导接垫及各该接合线路,该抗应力线路层具有多个抗应力线路,所述抗应力线路设置于该芯片设置区中,所述抗应力线路与该芯片的该长边边缘平行,且所述凸块位于所述抗应力线路及该芯片的该长边边缘之间。

5.较佳地,各该抗应力线路与各该凸块之间具有第一间距,该第一间距小于50um。

6.较佳地,所述抗应力线路沿直线排列,该直线与该芯片的长边边缘平行。

7.较佳地,其中相邻的所述抗应力线路之间具有溢胶空间,该溢胶空间的宽度大于50um。

8.较佳地,该芯片具有短边边缘,该短边边缘的长度大于1.5mm。

9.较佳地,该覆晶元件的各该凸块的高度小于15um。

10.较佳地,该覆晶元件具有多个第一凸块及多个第二凸块,该芯片具有第一长边边缘及第二长边边缘,所述第一凸块邻近该第一长边边缘,所述第二凸块邻近该第二长边边缘。

11.较佳地,该抗应力线路层具有多个第一抗应力线路及多个第二抗应力线路,各该第一抗应力线路与各该第一凸块之间的第一间距小于50um,各该第二抗应力线路与各该第二凸块之间的第二间距小于50um,所述第一抗应力线路及所述第二抗应力线路之间不具有任何凸块或线路。

12.较佳地,该芯片具有两个短边边缘,各该短边边缘的长度大于1.5mm,该覆晶元件

的各该第一凸块及各该第二凸块的高度小于15um。

13.本发明借由平行于该长边边缘的所述抗应力线路降低所述凸块在覆晶制程中对于该软性基板产生的应力,而可避免该线路层的所述接合线路的断裂。

附图说明

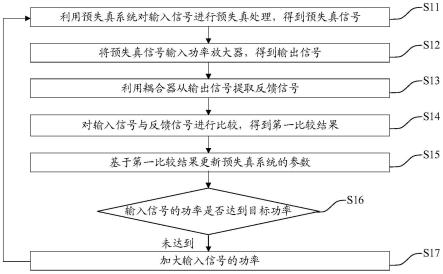

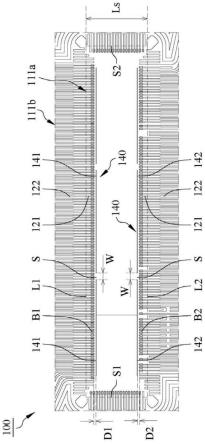

14.图1:依据本发明的一实施例,一种软性电路板的布线结构的俯视图。

15.图2:依据本发明的一实施例,该软性电路板的布线结构的剖视图。

16.图3:依据本发明的一实施例,该软性电路板的布线结构的局部放大图。

17.【主要元件符号说明】

18.100:软性电路板的布线结构110:软性基板

19.111:上表面111a:芯片设置区

20.111b:线路设置区120:线路层

21.121:接合线路122:传输线路

22.130:覆晶元件131:芯片

23.131a:导接垫132:凸块

24.140:抗应力线路层141:第一抗应力线路

25.142:第二抗应力线路l:长边边缘

26.l1:第一长边边缘l2:第二长边边缘

27.s1、s2:短边边缘s:溢胶空间

28.w:溢胶空间的宽度ls:短边边缘的长度

29.d1:第一间距d2:第二间距

30.b1:第一凸块b2:第二凸块

具体实施方式

31.请参阅图1及图2,其为本发明的一实施例,一种软性电路板的布线结构100的俯视图及剖视图,该软性电路板的布线结构100包含软性基板110、线路层120及覆晶元件130,该软性基板110是由聚酰亚胺(polyimide)或其他具有良好电绝缘性、稳定性、耐化学腐蚀性的聚合物制成,该线路层120则是电镀或压合于该软性基板110上的铜层经由图案化蚀刻而成,该覆晶元件130设置于该软性基板110上,且该覆晶元件130与该线路层120电性连接而可通过该线路层120传递电信号。

32.请参阅图1及图2,该软性基板110具有上表面111,该上表面111具有芯片设置区111a及线路设置区111b,该线路层120有多个接合线路121及多个传输线路122,所述接合线路121设置于该芯片设置区111a,所述传输线路122设置于该线路设置区111b,且各该传输线路122连接各该接合线路121。较佳的,所述接合线路121及所述传输线路122的表面镀有锡层,以利于所述接合线路121及所述传输线路122分别与该覆晶元件130及其他电子装置连接,且该线路层120除了与该覆晶元件130或其他电子装置连接的区域外涂布有防焊层(图未绘出),以避免其他的该线路层120受到制程高温的影响。

33.该覆晶元件130设置于该上表面111的该芯片设置区111a,该覆晶元件130具有芯片131及多个凸块132,该芯片131具有长边边缘l及多个导接垫131a,各该凸块132连接该芯

片131的各该导接垫131a及该线路层120的各该接合线路121。其中,所述凸块132是预先通过凸块制程形成于该芯片131上,所述凸块132可由金、铜、镍

…

等金属或其合金构成。

34.请参阅图3,为该软性电路板的布线结构100的局部放大图,在本实施例中,该覆晶元件130具有多个第一凸块b1及多个第二凸块b2,该芯片131具有第一长边边缘l1、第二长边边缘l2及两个短边边缘s1、s2,该第一长边边缘l1、该第二长边边缘l2及该两个短边边缘s1、s2构成长方形区域,该长方形区域对应该芯片设置区111a,该长方形区域以外的区域则对应该线路设置区111b。所述第一凸块b1邻近该第一长边边缘l1,所述第二凸块b2邻近该第二长边边缘l2,部分的所述接合线路121与所述第一凸块b1电性连接,部分的所述接合线路121与所述第二凸块b2电性连接。

35.较佳的,该软性电路板的布线结构100另具有抗应力线路层140,该抗应力线路层140具有多个第一抗应力线路141及多个第二抗应力线路142,所述第一抗应力线路141及所述第二抗应力线路142设置于该芯片设置区111a中。其中,所述第一抗应力线路141邻近该第一长边边缘l1并沿平行于该第一长边边缘l1的直线排列,使得所述第一抗应力线路141也平行于该第一长边边缘l1。该覆晶元件130的所述第一凸块b1位于所述第一抗应力线路141及该第一长边边缘l1之间,使得所述第一抗应力线路141能够减少覆晶制程中所述第一凸块b1对该软性基板110产生的应力,而可避免连接所述第一凸块b1的所述接合线路121的断裂。所述第二抗应力线路142邻近该第二长边边缘l2并沿平行于该第二长边边缘l2的直线排列,使得所述第二抗应力线路142也平行于该第二长边边缘l2。该覆晶元件130的所述第二凸块b2位于所述第二抗应力线路142及该第二长边边缘l2之间,使得所述第二抗应力线路142能够减少覆晶制程中所述第二凸块b2对该软性基板110产生的应力,而可避免连接所述第二凸块b2的所述接合线路121的断裂。

36.在本实施例中,所述第一抗应力线路141及所述第二抗应力线路142之间不具有任何凸块或线路,导致覆晶制程产生的应力对于所述接合线路121影响可能更大,因此,借由所述第一抗应力线路141及所述第二抗应力线路142分别设置于邻近所述第一凸块b1及所述第二凸块b2的区域上,可大幅地降低应力的影响。

37.较佳地,为避免该抗应力线路层140影响该芯片131的底部填充胶(underfill)的流动,相邻的所述第一抗应力线路141及相邻的所述第二抗应力线路142之间具有溢胶空间s,且该溢胶空间s的宽度w大于50um,使得底部填充胶能够经由该溢胶空间s流动至该芯片131与该软性基板110之间。

38.请参阅图2及图3,在本实施例中,各该短边边缘s1、s2的长度ls大于1.5mm,该覆晶元件130的各该第一凸块b1及该第二凸块b2的高度小于15um。这将导致该芯片131可能会在覆晶制程中因为加压下凹接触到该抗应力线路层140而产生压痕,因此,较佳的,各该第一抗应力线路141与各该第一凸块b1之间的第一间距d1小于50um,各该第二抗应力线路142与各该第二凸块b2之间的第二间距d2小于50um,以通过所述第一凸块b1及所述第二凸块b2的支撑,避免该芯片131接触到该抗应力线路层140。

39.本发明借由平行于该长边边缘l的所述抗应力线路降低该覆晶元件130的所述凸块132在覆晶制程中对于该软性基板110产生的应力,而可避免该线路层120的所述接合线路121的断裂。

40.以上所述,仅是本发明的较佳实施例而已,并非对本发明做任何形式上的限制,虽

然本发明已以较佳实施例揭露如上,然而并非用以限定本发明,任何熟悉本专业的技术人员,在不脱离本发明技术方案范围内,当可利用上述揭示的技术内容做出些许更动或修饰为等同变化的等效实施例,但凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所做的任何简单修改、等同变化与修饰,均仍属于本发明技术方案的范围内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。