1.本发明涉及半导体装置及其制造方法,例如涉及接合有半导体芯片的半导体装置及其制造方法。

背景技术:

2.gan hemt(gallium nitride high electron mobility transistor:氮化镓高电子迁移率晶体管)等氮化物半导体装置被用于移动通信的基站用的高频功率放大装置等。已知将gan hemt等的半导体芯片面朝上(face up)安装于散热性构件上(例如专利文献1)。

3.现有技术文献

4.专利文献

5.专利文献1:日本特开2019-176149

6.在面朝上安装中,将接合线用于与半导体芯片的电连接,因此高频特性容易劣化。为了提高高频特性,考虑将半导体芯片倒装(flip chip)接合(即面朝下安装)。在将半导体芯片倒装接合于基板的情况下,使用倒装接合机(flip chip bonder)。但是,倒装接合机的机构复杂,将半导体芯片搭载于基板的生产节拍时间(takt time)长。因此,不适合批量生产,会高成本化。

技术实现要素:

7.本公开是鉴于上述问题而完成的,其目的在于提供能实现低成本化的半导体装置及其制造方法。

8.本公开的一个实施方式是半导体装置的制造方法,包括以下工序:准备第一基板和半导体芯片,所述第一基板在第一面设有第一图案,所述半导体芯片具有第二面和与所述第二面相对的第三面,在所述第二面设有第二图案;从离所述第一基板的所述第一面和与所述第一面相对的面中的所述第一面近的位置识别所述第一图案;从离所述半导体芯片的所述第二面和所述第三面中的所述第三面近的位置透过所述半导体芯片来识别所述第二图案;基于所述第一图案和所述第二图案的识别结果来将所述半导体芯片与所述第一基板对位;以及以所述第二面与所述第一面对置的方式将所述半导体芯片接合于所述第一基板。

9.本公开的一个实施方式是半导体装置,具备:基板,在第一面设有第一图案;以及半导体芯片,具有第二面和与所述第二面相对的第三面,在所述第二面设有第二图案,所述第三面的算术平均粗糙度为0.1μm以下,所述半导体芯片以所述第二面与所述第一面对置的方式接合于所述基板上,所述半导体芯片对于可见光和红外光的波长中的至少一部分波长的光是透明的。

10.发明效果

11.根据本公开,能提供能实现低成本化的半导体装置及其制造方法。

附图说明

12.图1是表示实施例1中的半导体芯片的俯视图。

13.图2是表示实施例1中的半导体芯片的剖视图。

14.图3a是表示实施例1中的半导体芯片的制造方法的剖视图。

15.图3b是表示实施例1中的半导体芯片的制造方法的剖视图。

16.图3c是表示实施例1中的半导体芯片的制造方法的剖视图。

17.图4a是表示实施例1中的基板的制造方法的剖视图。

18.图4b是表示实施例1中的基板的制造方法的剖视图。

19.图4c是表示实施例1中的基板的制造方法的剖视图。

20.图5是表示在实施例1中将半导体芯片搭载于基板的方法的剖视图。

21.图6是表示在实施例1中将半导体芯片搭载于基板的方法的剖视图。

22.图7是从实施例1中的半导体芯片的第三面观察第二面上的图案所见的俯视图。

23.图8是实施例1中的基板的第一面上的图案的俯视图。

24.图9是从实施例1中的半导体芯片的第三面观察搭载半导体芯片后的半导体芯片和基板所见的图。

25.图10a是表示实施例1中的半导体装置的制造方法的剖视图。

26.图10b是表示实施例1中的半导体装置的制造方法的剖视图。

27.图10c是表示实施例1中的半导体装置的制造方法的剖视图。

28.图11a是表示实施例1中的半导体装置的制造方法的剖视图。

29.图11b是表示实施例1中的半导体装置的制造方法的剖视图。

30.图11c是表示实施例1中的半导体装置的制造方法的剖视图。

31.图12是实施例1中的半导体装置的剖视图。

32.图13是安装了实施例1中的半导体装置的剖视图。

33.图14是表示在比较例2中将半导体芯片搭载于基板的方法的剖视图。

34.图15是表示在比较例2中将半导体芯片搭载于基板的方法的剖视图。

35.附图标记说明

36.10:半导体芯片

37.10a:第二面

38.10b:第三面

39.11、11a:基板(第二基板)

40.11b:半导体层

41.12:源极指

42.13:源极焊盘

43.14:漏极指

44.15:漏极焊盘

45.16:栅极指

46.17:栅极焊盘

47.17a:栅极布线

48.18:突起金属层

49.19:图案(第二图案)

50.22a:图案(第一图案)

51.22b、22c、26a、26b:图案

52.20:基板(第一基板)

53.20a:第一面

54.21:绝缘层

55.22:布线层

56.23、58:焊料层

57.24:树脂层

58.25:贯通电极

59.26、57:金属层

60.27:贯通孔

61.28:支承基板

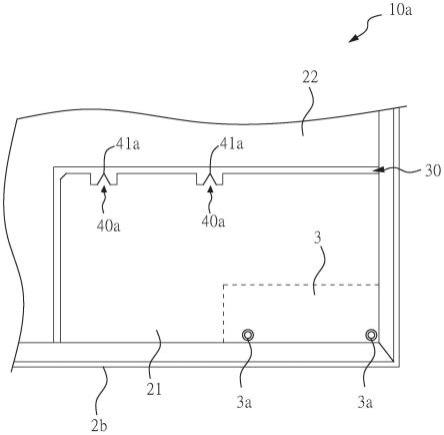

62.30:芯片部件

63.31~33:焊盘

64.40:芯片安装机

65.40a:倒装接合机

66.41:夹头

67.42、42a、42b:摄像机

68.43a~43d、47a、47b、53:箭头

69.44、45:载台

70.46a:半透半反镜面

71.46b:反射镜面

72.46:光学系统

73.48:控制部

74.48a、48b:识别部

75.50:区域

76.52:磨具

77.54:切割膜

78.55:切割刀片

79.56:印刷基板

80.100:半导体装置。

具体实施方式

81.[本公开的实施方式的说明]

[0082]

首先,列举出本公开的实施方式的内容进行说明。

[0083]

(1)本公开的一个实施方式是半导体装置的制造方法,包括以下工序:准备第一基板和半导体芯片,所述第一基板在第一面设有第一图案,所述半导体芯片具有第二面和与所述第二面相对的第三面,在所述第二面设有第二图案;从离所述第一基板的所述第一面

和与所述第一面相对的面中的所述第一面近的位置识别所述第一图案;从离所述半导体芯片的所述第二面和所述第三面中的所述第三面近的位置透过所述半导体芯片来识别所述第二图案;基于所述第一图案和所述第二图案的识别结果来将所述半导体芯片与所述第一基板对位;以及以所述第二面与所述第一面对置的方式将所述半导体芯片接合于所述第一基板。由此,能实现低成本化。

[0084]

(2)优选的是,识别所述第一图案的工序包括在将所述第一基板以所述第一面朝上的方式配置于第一载台上并将所述半导体芯片以所述第三面朝上的方式配置于第二载台上的状态下,从上方识别所述第一图案的工序,识别所述第二图案的工序包括在所述状态下透过所述半导体芯片来识别所述第二图案的工序,所述接合的工序包括吸附所述第二载台上的所述半导体芯片的所述第三面,将所述半导体芯片移动至所述第一载台上,由此将所述半导体芯片搭载于所述第一基板上的工序。

[0085]

(3)优选的是,所述半导体芯片对于具有可见光和红外光的波长中的至少一部分波长的光是透明的,识别所述第二图案的工序包括使用具有所述至少一部分波长的光来识别所述第二图案的工序。

[0086]

(4)优选的是,所述半导体芯片具备:第二基板,该第二基板是sic基板、蓝宝石基板或gan基板,具有所述第三面;以及氮化物半导体层,设于所述第二基板上,具有所述第二面。

[0087]

(5)优选的是,所述第三面的算术平均粗糙度为0.1μm以下。

[0088]

(6)优选的是,所述半导体芯片处理高频信号。

[0089]

(7)优选的是,包括以下工序:在所述接合的工序之后,在所述半导体芯片的所述第三面形成金属层。

[0090]

(8)本公开的一个实施方式是半导体装置,具备:基板,在第一面设有第一图案;以及半导体芯片,具有第二面和与所述第二面相对的第三面,在所述第二面设有第二图案,所述第三面的算术平均粗糙度为0.1μm以下,所述半导体芯片以所述第二面与所述第一面对置的方式接合于所述基板上,所述半导体芯片对于可见光和红外光的波长中的至少一部分波长的光是透明的。

[0091]

[本公开的实施方式的详情]

[0092]

以下,参照附图对本公开的实施方式的半导体装置及其制造方法的具体例进行说明。需要说明的是,本公开并不限定于这些示例,而是由权利要求书示出,意图在于包括与权利要求书等同的含义和范围内的所有变更。

[0093]

[实施例1]

[0094]

实施例1是使用rdl(redistribution layer:再布线层)优先工艺法,通过fo-plp(fan-out panel level package:扇出型面板级封装)来安装gan hemt等的氮化物半导体芯片的例子。fo-plp是在宽度为500mm~700mm的方形基板上制造封装件的方法。rdl优先工艺法是在方形基板上形成再布线层后,将半导体芯片安装于方形基板的方法。

[0095]

图1是表示实施例1中的半导体芯片的俯视图。图2是表示实施例1中的半导体芯片的剖视图。图2相当于图1的a-a剖面。如图1和图2所示,半导体芯片10具有第二面10a和作为与第二面10a相对的面的第三面10b。基板11具备设于第三面10b侧的基板11a和设于第二面10a侧的半导体层11b。在半导体芯片10形成gan-hemt的情况下,基板11a例如是sic基板、

蓝宝石基板或gan基板。基板11a的厚度例如为10μm~500μm。半导体层11b例如是氮化物半导体层,例如是gan层和algan(al的组成比例如为0.3)层。基板11对于可见光和红外光是大致透明的。

[0096]

在半导体芯片10的第二面10a设有图案19。图案19是源极指12、漏极指14、栅极指16、源极焊盘13、漏极焊盘15、栅极焊盘17以及栅极布线17a。源极指12和漏极指14交错地排列。在源极指12与漏极指14之间的基板11上设有栅极指16。栅极指16夹在源极指12与漏极指14之间。多个源极指12连接于源极焊盘13,多个漏极指14连接于漏极焊盘15。多个栅极指16经由栅极布线17a连接于栅极焊盘17。栅极布线17a隔着绝缘层或空气与源极指12和源极焊盘13交叉。在源极焊盘13、漏极焊盘15以及栅极焊盘17上设有突起金属层18。也可以不设置突起金属层18。

[0097]

源极指12和漏极指14是金属膜,例如从基板11侧起是钛膜和铝膜。栅极指16是金属膜,例如从基板11侧起是镍膜和金膜。源极焊盘13、漏极焊盘15、栅极焊盘17以及栅极布线17a例如是金层金属层。突起金属层18例如是金凸块(bump)、铜凸块或铜柱等。突起金属层18的高度例如为5μm~50μm。

[0098]

图3a至图3c是表示实施例1中的半导体芯片的制造方法的剖视图。如图3a所示,基板11是晶片,设有多个成为半导体芯片的区域50。在各区域50的表面11c形成有图案19和突起金属层18。基板11的厚度例如为500μm以上。在基板11的表面11c形成图案19等时,若基板11使红外线透射,则半导体制造装置的红外线传感器无法感测晶片。因此,基板11的背面11d是粗糙面。

[0099]

如图3b所示,使用磨具52如箭头53那样对基板11的背面11d进行磨削,使基板11变薄。基板11的厚度例如为10μm~200μm。此时,将磨具52的粒度设为例如#8000,由此使基板11的背面11d成为镜面。背面11d的算术平均粗糙度ra例如为0.01μm。

[0100]

如图3c所示,将变薄的基板11的背面贴合于树脂制的切割膜(dicing film)54。使用切割刀片55对变薄的基板11进行切割。由此,形成与多个区域50对应的多个半导体芯片10。

[0101]

图4a至图4c是表示实施例1中的基板的制造方法的剖视图。如图4a所示,在支承基板28上贴合绝缘层21。支承基板28例如是树脂基板等绝缘基板,在制造工序中对绝缘层21进行加强。绝缘层21例如是树脂层。绝缘层21的上表面是第一面20a。

[0102]

如图4b所示,例如使用镀覆法在绝缘层21的第一面20a形成布线层22。布线层22例如是铜层或金层等金属层。通过布线层22形成图案22a~22c。由此,形成基板20。需要说明的是,基板20例如是宽度为500mm~700mm的方形基板,这里仅图示出一个半导体装置的区域的截面。如图4c所示,例如使用印刷法在图案22a和图案22b上形成焊料层23。焊料层23例如是锡银铜焊料。

[0103]

图5和图6表示在实施例1中将半导体芯片搭载于基板的方法的剖视图。如图5所示,使用通用的芯片安装机(chip mounter)40来作为将半导体芯片10安装于基板20的安装机。芯片安装机40具备摄像机42a、42b、夹头41、载台44、45以及控制部48。在载台44上搭载有作为大型的方形基板的基板20。在位置校正用的载台45上搭载有半导体芯片10。此时,突起金属层18与载台45的上表面相接,因此能抑制图案19与载台45的上表面接触。由此,能抑制载台45与图案19接触而在图案19上形成损伤以及在图案19上附着异物。

[0104]

摄像机42a如箭头43a那样从第三面10b侧透过基板11来拍摄设于半导体芯片10的第二面10a的图案19。摄像机42a使用会透射过基板11的波长的光来拍摄图案19。被用作基板11a的sic基板、蓝宝石基板或gan基板对于可见光是大致透明的。在将氮化物半导体层用作半导体层11b的情况下,gan层和algan层对于可见光是大致透明的。进而,若半导体芯片10的第三面10b不是镜面,则光会在第三面10b发生漫反射以致摄像机42a无法拍摄图案19。在实施例1中,将第三面10b的算术平均粗糙度ra设为0.1μm以下。因此,能抑制光在第三面10b发生漫反射。

[0105]

在将sic基板用作基板11a的情况下,sic对于0.38μm~5μm的波长的光是大致透明的。若使用0.38μm~0.78μm的可见光和0.78μm~5μm的红外光,则摄像机42a能经由基板11拍摄图案19。例如,作为半导体芯片10的照明,使用照射0.42μm~0.66μm的波长的光的led(light emitting diode:发光二极管)照明或照射0.78μm~3μm的光的近红外线照明。

[0106]

摄像机42b如箭头43b那样拍摄设于基板20的第一面20a的图案22a。控制部48计算摄像机42a拍摄到的图案19与摄像机42b拍摄到的图案22a的相对位置。

[0107]

如图6所示,夹头41吸附半导体芯片10的第三面10b。之后,基于图案19与图案22a的相对位置,夹头41将半导体芯片10移动至基板20的上方。夹头41将半导体芯片10搭载于基板20。

[0108]

图7是从实施例1中的半导体芯片的第三面观察第二面上的图案所见的俯视图。如图7所示,能从第三面10b目视确认第二面10a的图案19。控制部48识别图案19中的识别部48a的图案。为了提高图案19与图案22a的对位精度,识别部48a优选是图案19中的对角的图案,但识别部48a也可以是对角以外的图案。

[0109]

图8是实施例1中的基板的第一面上的图案的俯视图。如图8所示,作为图案22a设有焊盘31~33。在焊盘31~33分别接合源极焊盘13、漏极焊盘15以及栅极焊盘17。控制部48识别图案22a中的识别部48b处的图案。

[0110]

图9是从实施例1中的半导体芯片的第三面观察安装半导体芯片后的半导体芯片和基板所见的图。如图9所示,源极焊盘13、漏极焊盘15以及栅极焊盘17分别接合于焊盘31~33。在图5中,控制部48计算半导体芯片10与基板20的相对位置,在图6中,控制部48基于计算出的相对位置来将半导体芯片10搭载于基板20。因此,图案19与图案22a被对位。如图9那样,在将半导体芯片10接合于基板20后,能从第三面10b侧目视确认图案19和图案22a。由此,能使用自动外观检查装置(aoi:automated optical inspection)来检查焊盘31~33与源极焊盘13、漏极焊盘15以及栅极焊盘17的接合状态。

[0111]

图10a~图11c是表示实施例1中的半导体装置的制造方法的剖视图。如图10a所示,在基板20上搭载半导体芯片10和芯片部件30。半导体芯片10搭载于图案22a,芯片部件30搭载于图案22b。芯片部件30例如是芯片电阻、芯片电容器或芯片电感器。将在图5和图6中说明过的通用芯片安装机40用于半导体芯片10和芯片部件30的搭载。通过进行回流(即热处理),焊料层23熔融,图案22a与图案19被接合。由此,半导体芯片10倒装接合于基板20。使用自动外观检查装置检查图案19与图案22a的接合状态。需要说明的是,在图10a中,焊料层23经由突起金属层18接合于图案19,但也可以不设置突起金属层18,而是焊料层23直接接合于图案19。

[0112]

如图10b所示,以覆盖半导体芯片10和芯片部件30的方式在基板20上形成树脂层

24。树脂层24是通过贴合环氧树脂等树脂片的层压法而形成的。树脂层24也可以使用成型法来形成。如图10c所示,对树脂层24的上表面进行磨削或研磨,使半导体芯片10的第三面10b露出。

[0113]

如图11a所示,例如使用刻蚀法形成贯通树脂层24的贯通孔27。图案22c从贯通孔27露出。如图11b所示,例如使用镀覆法在贯通孔27内形成贯通电极25。贯通电极25例如是铜层或金层等金属层。

[0114]

如图11c所示,例如使用镀覆法在树脂层24上形成金属层26。金属层26例如是铜层。金属层26包括图案26a和图案26b。图案26a作为与半导体芯片10的第三面10b接触从而释放在半导体芯片10产生的热的散热层发挥功能。图案26b经由贯通电极25电连接于布线层22的图案22c。图案22c与图案22a和图案22b电连接。由此,图案22b作为使半导体芯片10和芯片部件30电连接于外部装置的外部端子发挥功能。

[0115]

图12是实施例1中的半导体装置的剖视图。如图12所示,从绝缘层21去除支承基板28。之后,对绝缘层21和树脂层24进行切割来使其单片化。由此,制造出半导体装置100。

[0116]

图13是安装了实施例1中的半导体装置的剖视图。如图13所示,在印刷基板56上设有金属层57。金属层57与半导体装置100的金属层26经由焊料层58被接合。

[0117]

[比较例]

[0118]

gan hemt等氮化物半导体装置被用于移动通信的基站用的高频功率放大装置等。因此,对于半导体装置,要求高频特性的维持、散热性以及低成本化。作为形成了gan hemt等的半导体芯片的安装方法,考虑以面朝上的方式安装于封装件的比较例1。接合线连接于半导体芯片的上表面,经由接合线相对于半导体芯片输入输出高频信号。在比较例1中,由于在对半导体芯片进行面朝上安装时为了确保散热性而使用昂贵的纳米银膏,因此难以实现低成本化。由于经由接合线的电感相对于半导体芯片输入输出高频信号,因此高频特性降低。

[0119]

因此,作为比较例2,考虑通过fo-plp(fan-out panel level package)安装。在比较例2中,由于对半导体芯片10进行倒装接合,因此与比较例1那样使用接合线的情况相比,能抑制高频特性的降低。由于能将金属层26直接接合于半导体芯片10的第三面10b,因此也可以不像比较例1那样使用昂贵的纳米银膏,能实现低成本化。

[0120]

图14和图15是表示在比较例2中将半导体芯片搭载于基板的方法的剖视图。如图14所示,在比较例2中,使用倒装接合机40a来作为将半导体芯片10搭载于基板20的安装机。倒装接合机40a具备摄像机42、夹头41、载台44以及光学系统46。光学系统46具有半透半反镜面46a和反射镜面46b,配置于图案22a与图案19之间。摄像机42能如箭头43c那样拍摄在半透半反镜面46a发生了反射的图案19的图像。此外,摄像机42能如箭头43d那样透过半透半反镜面46a,在反射镜面46b发生反射,拍摄在半透半反镜面46a发生了反射的图案22a的图像。夹头41移动半导体芯片10,使得图案19与图案22a重叠。

[0121]

如图15所示,在半导体芯片10的俯视方向的位置确定后,光学系统46如箭头47a那样退避。如箭头47b那样,将夹头41向下方移动,在基板20上搭载半导体芯片10。在比较例2中,由于使用光学系统46来对图案19与图案22a进行对位,因此能提高对位精度。然而,由于要进行光学系统46的退避,因此生产节拍时间长,不适合批量生产。所以,会高成本化。

[0122]

作为比较例3,也可以使用图5那样的芯片安装机,不进行图案19和图案22a的识别

就将半导体芯片10安装于基板20上。但是,图案19与图案22a的对位精度降低。

[0123]

根据实施例1,如图3a~图3c那样,准备在第二面10a设有图案19(第二图案)的半导体芯片10。如图4a~图4c那样,准备在第一面20a设有图案22a(第一图案)的基板20(第一基板)。如图5、图7以及图8那样,摄像机42a从离半导体芯片10的第二面10a和第三面10b中的第三面10b近的位置透过半导体芯片10来识别图案19,摄像机42b从离基板20的第一面20a和与第一面20a相对的下表面中的第一面20a近的位置识别图案22a。如图6和图9那样,控制部48基于图案19和图案22a的识别结果来将半导体芯片10与基板20对位,以第二面10a与第一面20a对置的方式将半导体芯片10倒装接合于基板20。由此,也可以不使用比较例2的图14和图15那样的复杂的倒装接合机40a,通过使用通用芯片安装机40,从而生产节拍时间变短,能进行半导体装置的批量生产。由此,能将半导体装置100低成本化。此外,能抑制如比较例3那样对位精度降低。

[0124]

如图5那样,将基板20以第一面20a朝上的方式配置于载台44(第一载台)上,将半导体芯片10以第三面10b朝上的方式配置于载台45(第二载台)上。在该状态下,从上方识别图案22a,从上方透过半导体芯片10来识别图案19。如图6那样,夹头41(吸附构件)吸附载台45上的半导体芯片10的第三面10b,将半导体芯片10移动至载台44上,由此将半导体芯片10搭载于基板20上。由此,能使用通用芯片安装机40来实现半导体装置的批量生产。

[0125]

半导体芯片10对于具有可见光和红外光的波长中的至少一部分波长的光是透明的。如图5那样,在将半导体芯片10倒装接合于基板20的工序中,摄像机42a使用会透射过半导体芯片10的光来识别图案19。由此,摄像机42a能从离半导体芯片10的第二面10a和第三面10b中的第三面10b近的位置使用会透射过半导体芯片10的光来识别图案19。半导体芯片10对于识别图案19时使用的光的透射率优选为20%以上,更优选为50%以上,进一步优选为80%以上。由此,摄像机42a能使用会透射过半导体芯片10的光来识别图案19。

[0126]

基板11a(第二基板)是sic基板、蓝宝石基板或gan基板,半导体层11b是氮化物半导体层。由此,基板11a和半导体层11b对于可见光和红外光的波长中的至少一部分波长的光为透明。此外,sic基板的导热率高,能实现从第三面10b的散热。

[0127]

半导体芯片10是处理(例如放大)高频信号的半导体芯片。如此,在处理高频信号的半导体芯片10中,高频特性根据图案19与图案22a的对准位置而变化。由此,根据实施例1,能提高对位精度,使高频特性稳定化。高频信号例如是0.5ghz~100ghz的信号,典型而言是0.5gz~10ghz的信号。

[0128]

在第三面10b是粗糙面的情况下,光会在第三面10b上发生漫反射。因此,摄像机42a无法识别图案19。由此,第三面10b的算术平均粗糙度ra优选为0.1μm以下,更优选为0.05μm以下,进一步优选为0.02μm以下。

[0129]

如图11c那样,在进行倒装接合的工序之后,在半导体芯片10的第三面10b形成金属层26。由此,金属层26与第三面10b被直接接合,能将金属层26用作散热层。若使用镀覆法来形成金属层26,则可以不像比较例1那样使用昂贵的纳米银膏,能将半导体装置100低成本化。

[0130]

根据实施例1的半导体装置100,在第一面20a设有图案22a(第一图案),在第二面10a设有图案19(第二图案)。半导体芯片10以第二面10a与第一面20a对置的方式倒装接合于基板20上。半导体芯片10对于可见光和红外光的波长中的至少一部分波长的光是透明

的,第三面10b的算术平均粗糙度为0.1μm以下。如此,第三面10b是镜面,半导体芯片10对于可见光和红外光的波长中的至少一部分波长的光是透明的,由此,如图5和图6那样,能使用通用芯片安装机来将半导体芯片10倒装接合于基板20上。由此,能将半导体装置100低成本化。

[0131]

在实施例1中,以设置了单体的gan hemt的半导体芯片10为例进行了说明,但半导体芯片10也可以是mmic(monolithic microwave integrated circuit:单片微波集成电路)。作为半导体装置,对使用fo-plp技术的例子进行了说明,但只要半导体芯片倒装接合于基板即可。

[0132]

应该认为本次公开的实施方式在所有方面都是示例而不是限制性的。本公开的范围并不是上述的含义,而是由权利要求书示出,意图在于包括与权利要求书等同的含义和范围内的所有变更。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。