1.本发明系指一种驱动电路,尤指一种使输入端与输出端的工作周期趋于一致的闸极驱动电路。

背景技术:

2.闸极驱动电路(gate driver circuit)会产生电流到电晶体的闸极,以驱动该电晶体。然而,在现有的电路设计中,该电晶体的放电路径的过大负载容易造成较长的放电时间,使输入该闸极驱动电路的电压与该电晶体输出的电压的工作周期(duty cycle)不一致。此外,在闸极驱动电路将该电晶体导通或关闭时,由于该电晶体不会立刻切换到导通或关闭的状态,切换过程中可能会有短暂时间通过极大电流,使该电晶体的闸极与输出端之间的电压差过大,进而使该电晶体过热而被毁损。因此,如何使输入闸极驱动电路的电压与该电晶体输出的电压的工作周期一致为亟待解决的问题。

技术实现要素:

3.因此,本发明的主要目的即在于提供一种驱动电路,其具有使输入端与输出端的工作周期趋于一致的闸极驱动电路,以解决上述问题。

4.本发明揭露一种驱动电路,包含有一第一内部电路及一外部电路。该第一内部电路包含有一第一缓冲器,用来接收一第一输入电压。该外部电路耦接于该第一缓冲器及一接地端之间,包含有一第一电晶体,用来根据该第一输入电压,产生一负载电压。该第一内部电路另包含有一电流镜,用来根据一电流源,提供一电流;一互补式金属氧化物半导体(complementary metal-oxide-semiconductor,cmos),耦接于该电流镜、该第一缓冲器及该外部电路之间,用来驱动该外部电路;以及一第二电晶体,耦接于该互补式金属氧化物半导体及该接地端之间,用来提供该第一电晶体透过该第二电晶体进行一放电运作。

附图说明

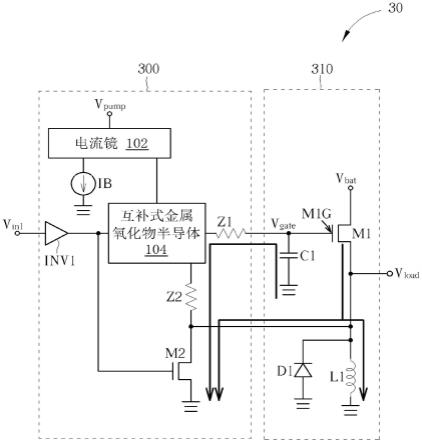

5.第1图为本发明实施例的一驱动电路的示意图。

6.第2图为第1图中的驱动电路相关运作的电压波形图。

7.第3图为本发明实施例的一驱动电路的示意图。

8.第4图为第3图中的驱动电路相关运作的电压波形图。

9.第5图为本发明实施例的一驱动电路的示意图。

10.其中,附图标记说明如下:

11.10、30、50

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

驱动电路

12.100、300、500、510

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

内部电路

13.110、310、520

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

外部电路

14.102

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

电流镜

15.104

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

互补式金属氧化物半导体

16.inv1、inv2

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

缓冲器

[0017]vin1

、v

in2

、v

pump

、v

bat

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

输入电压

[0018]vgate

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

闸极电压

[0019]vload

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

负载电压

[0020]

m1、m2、m3

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

电晶体

[0021]

m1g

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

闸极

[0022]

z1、z2、z3

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

阻抗单元

[0023]

ib

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

电流源

[0024]

c1

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

电容器

[0025]

l1

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

电感器

[0026]

d1

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

二极体

[0027]din

、d

gate

、d

load

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

工作周期

具体实施方式

[0028]

在说明书及后续的申请专利范围当中使用了某些词汇来指称特定的元件。本领域具通常知识者应可理解,硬体制造商可以使用不同的名词来称呼同样的元件。本说明书及后续的申请专利范围并不以名称的差异来作为区分元件的方式,而是以元件在功能上的差异来作为区分的准则。在通篇说明书及后续的权利要求当中所提及的“包含”系为一开放式的用语,故应解释成“包含但不限定于”。另外,“耦接”一词在此系包含任何直接及间接的电性连接手段。因此,若文中陈述一第一装置耦接于一第二装置,则代表该第一装置可直接电性连接于该第二装置,或透过其他装置或连接手段间接地电性连接到该第二装置。

[0029]

第1图为本发明实施例的一驱动电路10的示意图。驱动电路10包含有一内部电路100及一外部电路110。内部电路100包含有一缓冲器inv1、一阻抗单元z1、一电流镜102、一互补式金属氧化物半导体(complementary metal-oxide-semiconductor,cmos)104、一阻抗单元z2。外部电路110包含有一电晶体m1,一电感器l1、一二极体d1及一电容器c1。根据从缓冲器inv1接收的一输入电压v

in1

,驱动电路10在外部电路110产生一负载电压v

load

。

[0030]

如第1图所示,在内部电路100中,根据一电流源ib,电流镜102产生一电流。电流镜102可由一系统电源供电运作,该系统电源可包含有一第一端及一第二端,以及该第一端及该第二端之间的电压为一输入电压v

pump

。在本实施例中,该第二端以一接地端表示,惟不以此为限。互补式金属氧化物半导体104耦接于缓冲器inv1、电流镜102及外部电路110之间,用来驱动外部电路110。阻抗单元z1及阻抗单元z2耦接于互补式金属氧化物半导体104及外部电路110之间。

[0031]

外部电路110中的电晶体m1用来产生负载电压v

load

。电晶体m1的一闸极m1g耦接于阻抗单元z1。电晶体m1可由一系统电源供电运作,该系统电源可包含有一第一端及一第二端,以及该第一端耦接到一输入电压v

bat

。在本实施例中,该第二端以该接地端表示,惟不以此为限。电感器l1耦接于电晶体m1及该接地端之间,以形成外部电路110的一放电路径。二极体d1耦接于电晶体m1及该接地端之间(即以并联方式与电感器l1耦接),用来缓冲流入电感器l1的电流的变化速率。也就是说,二极体d1具有稳定电感器l1两端的电压(即负载电压v

load

)的功能。电容器c1为一外部寄生之负载并耦接于电晶体m1及该接地端之间,用来缓冲

电晶体m1的闸极m1g与该接地端之间的一闸极电压v

gate

的变化速率。也就是说,电容器c1可降低电晶体m1的闸极m1g与该接地端之间该闸极电压v

gate

的变化速率。

[0032]

第2图为根据本发明实施例的驱动电路10相关运作的电压波形图。在第2图中,由上到下依序为输入电压v

in1

、电晶体m1的闸极m1g的闸极电压v

gate

及外部电路110产生的负载电压v

load

的波形图。在驱动电路10中,电晶体m1放电的时间长短与外部电路110中的电感器l1及电容器c1相关。在外部电路110仅可透过电感器l1进行放电运作,以及此放电路径具有较大负载的情形下,电晶体m1放电的时间过长,造成闸极电压v

gate

的工作周期(duty cycle)d

gate

及负载电压v

load

的工作周期d

load

与输入电压v

in1

的工作周期d

in

不一致。此外,在放电时间越长的情形下,驱动电路10中的闸极电压v

gate

及负载电压v

load

之间具有电压差的时间也会越长,也越容易造成电晶体m1因压差过大而毁损。

[0033]

第3图为本发明实施例的一驱动电路30的示意图。驱动电路30为前述驱动电路10的一变化实施例,相同元件的运作方式可参考前述,在此不赘述。与前述驱动电路10不同的地方在于,驱动电路30中的内部电路300另包含有一电晶体m2。电晶体m2耦接于互补式金属氧化物半导体104、阻抗单元z2及该接地端之间,用来提供电晶体m1透过电晶体m2进行一放电运作。也就是说,外部电路310除了可透过电感器l1的进行放电运作以外,也可透过电晶体m2所形成的外部电路310的另一放电路径进行放电运作。

[0034]

第4图为根据本发明实施例的驱动电路30相关运作的波形图。在第4图中,由上到下依序为输入电压v

in1

、电晶体m1的闸极m1g的闸极电压v

gate

及外部电路310产生的负载电压v

load

的波形图。在驱动电路30中,由于电晶体m1进行放电运作时会同时流经电晶体m2及电感器l1的放电路径)。在此情形下,与驱动电路10相比,驱动电路30的电晶体m1放电的时间缩短,与输入电压v

in1

放电时的波形较一致,闸极电压v

gate

的工作周期d

gate

与负载电压v

load

的工作周期d

load

与v

in1

的工作周期d

in

也较一致。此外,由于放电时间大幅缩短,驱动电路30中的闸极电压v

gate

与负载电压v

load

之间具有电压差的时间(与驱动电路10相比)也大幅缩短,使电晶体m1不会因压差过大而毁损。

[0035]

第5图为本发明实施例的一驱动电路50的示意图。驱动电路包含有内部电路500、510及一外部电路520。内部电路500可为前述内部电路100或内部电路300,惟不以此为限。内部电路510包含有一缓冲器inv2及一阻抗单元z3。缓冲器inv2用来接收一输入电压v

in2

。阻抗单元z3耦接于缓冲器inv2。外部电路520除了包含有外部电路100中的电晶体m1以外,另包含有一电晶体m3。电晶体m3耦接于电晶体m1及该接地端之间,用来提供电晶体m1透过电晶体m3进行一放电运作。根据内部电路500中缓冲器inv1所接收的输入电压v

in1

及内部电路510中的缓冲器inv2所接收的输入电压v

in2

,外部电路520产生该负载电压v

load

。

[0036]

在上述实施例中,电晶体m1、电晶体m2及电晶体m3可为一金属氧化物半导体场效电晶体(metal-oxide-semiconductor field-effect transistor,mosfet),电流镜102可由两个金属氧化物半导体场效电晶体耦接而成,惟不以此为限。互补式金属氧化物半导体104可由一p型金属氧化物半导体场效电晶体及一n型金属氧化物半导体场效电晶体耦接而成,以及阻抗单元z1、阻抗单元z2及阻抗单元z3分别可为一电阻或其他阻抗元件。

[0037]

综上所述,本发明提供了一种使输入端与输出端的工作周期较一致的闸极驱动电路。透过在内部电路另耦接一电晶体,使外部电路的电晶体可透过该内部电路的电晶体放电,以使输入端与输出端的工作周期趋于一致,也可保护该外部电路的电晶体不会因压差

过大而毁损。

[0038]

以上所述仅为本发明的优选实施例而已,并不用于限制本发明,对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。