1.本技术案是针对存储器阵列区域中的导电层及其形成方法。

背景技术:

2.高数据可靠性、高速存储器存取、低功耗及缩减芯片大小是半导体存储器所要求的特征。为了缩减芯片大小,存储器单元之间的距离变得更短。

3.半导体装置包含导电层,例如位线及重新分布层(rdl)。例如,rdl是指互连层,其用于重新分布用于具有焊料凸块及倒装芯片连接的封装的端子。rdl将装置的输入/输出焊盘上的信号提供给其它位置。rdl通常安置在半导体装置的最上部分中。rdl往往形成较厚以具有低电阻。

4.形成rdl的常规方法包含形成金属膜及使用硬掩模干法蚀刻金属膜以隔离相邻rdl。然而,在准备对金属膜进行干法蚀刻时,金属膜下方的介电层需要具有相当大的厚度。介电层的厚度增加位线结构的高度。因此,位线结构往往弯曲,此是非所要的。

技术实现要素:

5.在一个方面中,本技术案是针对一种形成半导体存储器装置的方法,所述方法包括:在衬底上形成多个电容器触点;在所述多个电容器触点上形成介电层;移除所述介电层的部分以在所述介电层中形成多个开口;在所述多个所述对应的开口的底部处暴露所述多个电容器接点;及沉积导电材料以在所述多个对应的开口中形成多个互连件。

6.在另一方面中,本技术案是针对一种形成半导体存储器装置的方法,所述方法包括:在衬底上形成位线结构;形成至少一个第一介电层,其包含绝缘体的部分,所述绝缘体覆盖所述位线结构;在所述衬底上且相邻于所述绝缘体形成多个第一开口;在所述多个对应的第一开口中形成多个电容器触点;移除所述多个电容器触点的顶部部分以在所述多个电容器触点的剩余部分上形成多个第二开口;在所述多个对应的第二开口中的所述多个对应的电容器触点上形成多个第一互连件;在所述多个第一互连件、所述绝缘体及所述至少一个第一介电层上形成第二介电层;移除所述第二介电层的部分以在所述第二介电层中形成多个第三开口;在所述多个所述第三开口的底部处暴露所述多个第一互连件中的每一对应的第一互连件的部分;及在所述多个对应的第三开口中形成多个第二互连件。

7.在另一方面中,本技术案是针对一种设备,其包括:多个电容器触点,其位于衬底的有源区域上,所述多个电容器触点中的每一电容器触点在所述衬底中具有底部部分;介电层,其位于所述多个电容器触点上面;及多个互连件,其位于所述介电层中,其中每一互连件的宽度是大体上恒定的,且其中所述多个互连件中的每一互连件以横向偏移量安置在所述多个电容器触点中的每一对应的电容器触点上面。

附图说明

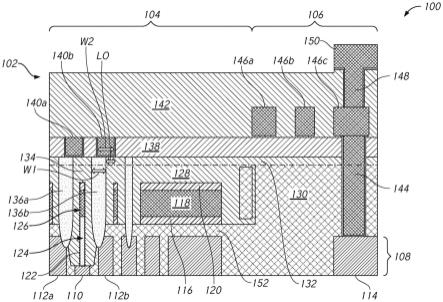

8.图1是根据本公开的实施例的半导体装置的部分的一个示意性结构的竖直横截面

图的图。

9.图2是根据本公开的实施例的半导体装置的部分的一个示意性结构的竖直横截面图的图。

10.图3是根据本公开的实施例的半导体装置的部分的一个示意性结构的竖直横截面图的图。

11.图4是根据本公开的实施例的半导体装置的部分的一个示意性结构的竖直横截面图的图。

12.图5是根据本公开的实施例的半导体装置的部分的一个示意性结构的竖直横截面图的图。

13.图6是根据本公开的实施例的半导体装置的部分的一个示意性结构的竖直横截面图的图。

14.图7是根据本公开的实施例的半导体装置的部分的一个示意性结构的竖直横截面图的图。

15.图8是根据本公开的实施例的半导体装置的部分的一个示意性结构的竖直横截面图的图。

16.图9是根据本公开的实施例的半导体装置的部分的一个示意性结构的竖直横截面图的图。

17.图10是根据本公开的实施例的半导体装置的部分的一个示意性结构的竖直横截面图的图。

18.图11是根据本公开的实施例的半导体装置的部分的一个示意性结构的竖直横截面图的图。

19.图12是根据本公开的实施例的半导体装置的部分的一个示意性结构的竖直横截面图的图。

20.图13是根据本公开的实施例的半导体装置的部分的一个示意性结构的竖直横截面图的图。

21.图14是根据本公开的实施例的半导体装置的部分的一个示意性结构的竖直横截面图的图。

22.图15是根据本公开的实施例的半导体装置的部分的一个示意性结构的竖直横截面图的图。

23.图16是根据本公开的实施例的半导体装置的部分的一个示意性结构的竖直横截面图的图。

24.图17是根据本公开的实施例的半导体装置的部分的一个示意性结构的竖直横截面图的图。

25.图18是根据本公开的实施例的半导体装置的部分的一个示意性结构的竖直横截面图的图。

26.图19是根据本公开的实施例的半导体装置的部分的一个示意性结构的竖直横截面图的图。

27.图20是根据本公开的实施例的半导体装置的部分的一个示意性结构的竖直横截面图的图。

28.图21是根据本公开的实施例的半导体装置的部分的一个示意性结构的竖直横截面图的图。

具体实施方式

29.下面将参考附图详细说明本公开的各种实施例。以下详细描述参考附图,附图通过说明的方式展示可实践本公开的具体方面及实施例。足够详细地描述这些实施例,以使得所属领域的技术人员能够实践本公开。可利用其它实施例,且可在不背离本公开的范围的情况下做出结构、逻辑及电改变。本文中所公开的各种实施例不必相互排斥,因为一些所公开的实施例可与一或多个其它所公开的实施例组合以形成新的实施例。

30.图1是根据本公开的实施例的半导体装置100的部分102的一个示意性结构的竖直横截面图的图。在一些实施例中,半导体装置100可为例如包含存储器单元的存储器装置(例如,动态随机存取存储器(dram))。每一存储器单元可包含晶体管及电容器。例如,部分102可包含晶体管,例如dram中的金属氧化物半导体场效应晶体管(mosfet)。

31.部分102包含半导体装置100的存储器阵列区域104及外围区域106的部分。存储器单元可安置在存储器阵列区域104中,且外围电路可安置在外围区域106中。在一些实施例中,半导体装置100可包含横跨存储器阵列区域104及外围区域106的衬底108。衬底108可在存储器阵列区域104中包含有源区域110、有源区域112a及112b。衬底108可在外围区域106中包含有源区域114。部分102可包含覆盖有源区域110、112a、112b及114的隔离结构152。有源区域110、112a、112b及114可通过隔离结构152彼此隔离。在一些实施例中,隔离结构152可为包含介电材料的浅沟槽隔离(sti)。部分102可在存储器阵列区域104中包含位于衬底108上的介电层116、位于介电层116上的导电层118以及位于导电层118上的介电层120。部分102可包含位于衬底108的有源区域110上的位线结构122。位线结构122可包含位于衬底108的有源区域110上的位线触点124,且进一步包含位于位线触点124上的位线126。在一些实施例中,可在衬底108的顶表面上提供位线触点124。在一些实施例中,位于位线触点124下方的衬底108的顶表面可具有小于衬底108的其余部分的厚度的高度。在一些实施例中,位线126可为导电层118的部分。部分102还可在存储器阵列区域104中包含位于介电层120上面的介电层128。部分102还可在外围区域106中包含介电层130。介电层130可具有距衬底108的高度与介电层128的顶表面的高度相同的顶表面。部分102可包含横跨存储器阵列区域104及外围区域106的介电层132。介电层132可安置在介电层128及130上。部分102可包含分别位于有源区域112a及112b上的电容器触点136a及136b。在一些实施例中,电容器触点136a及136b的下部部分可位于衬底108中。在一些实施例中,电容器触点136a及136b的顶表面可具有距衬底108与介电层132的顶表面相同的高度。部分102可进一步包含围绕位结构122的绝缘体134。位结构122可通过绝缘体134与电容器触点136a及136b绝缘。

32.部分102可包含横跨存储器阵列区域104及外围区域106的介电层138。在一些实施例中,介电层138可安置在介电层132及绝缘体134上。部分102可在介电层138中包含互连件140a及140b。互连件140a及140b可分别以横向偏移量lo安置在电容器触点136a及136b上。互连件140a及140b中的每一个可具有宽度w2,所述宽度大于电容器触点136a及136b中的每一个的宽度w1。在一些实施例中,互连件140a及140b的宽度w2可为大体上恒定的。互连件140a及140b可分别耦合到电容器触点136a及136b。部分102还可包含安置在有源区域114上

的通孔144。通孔144可穿过介电层130、132及138安置。部分102可包含横跨存储器阵列区域104及外围区域106的介电层142。部分102可在介电层142中包含互连件146a、146b及146c。互连件146c可安置在通孔144上。部分102还可包含位于介电层142中的通孔148。通孔148可安置在互连件146c上。部分102可进一步包含安置在介电层142及通孔148上的互连件150。在其它示例中可包含额外的、更少的及/或不同的组件。

33.下文参考图2到图14描述形成例如根据实施例的半导体存储器装置100的设备的方法。在一些实施例中,导电层可为重新分布层(rdl)。每一图式中的每一部分的尺寸及尺寸比不一定与实际的半导体装置的尺寸及尺寸比一致。

34.图2是根据本公开的实施例的半导体装置200的部分202的一个示意性结构的竖直横截面图的图。在一些实施例中,半导体装置200的部分202可为用于制作图1的半导体装置100的部分102的中间结构。部分202包含半导体装置200的存储器阵列区域104及外围区域106的部分。在一些实施例中,半导体装置200可包含横跨存储器阵列区域104及外围区域106的衬底108。在一些实施例中,衬底108可包含例如单晶硅。在以下描述中,以上以衬底108在部分102的底部处来定向。衬底108可在存储器阵列区域104中包含有源区域110以及有源区域112a及112b。衬底108可在外围区域106中包含有源区域114。部分202可包含覆盖有源区域110、112a、112b及114的隔离结构152。有源区域110、112a、112b及114可通过隔离结构152彼此隔离。在一些实施例中,隔离结构152可为包含介电材料的浅沟槽隔离(sti)。在一些实施例中,介电材料可包含氧化硅(sio2)。介电层116可形成在衬底108的隔离结构152上。在一些实施例中,介电层116可包含介电材料。介电材料可包含例如氮化硅(sin)。可通过物理气相沉积(pvd)或化学气相沉积(cvd)来沉积介电材料。

35.在形成介电层116之后,可移除介电层116的部分及衬底108的部分,包含有源区域110的部分及有源区域110周围的隔离结构152的部分。在一些实施例中,可通过蚀刻来执行介电层116及衬底108的部分的移除。因此,可在介电层116及衬底108中形成开口206。可沉积导电材料204以填充开口206。在一些实施例中,导电材料204可包含例如多晶硅(poly-si)。在一些实施例中,导电材料204可通过物理气相沉积(pvd)(例如,溅射导电材料)来沉积。在一些实施例中,可通过化学气相沉积(cvd)来沉积导电材料204。导电层118可形成在存储器阵列区域104中的介电层116及导电材料204上。导电层118可包含导电材料。在一些实施例中,导电材料可包含钨(w)。导电层118可通过物理气相沉积(pvd)(例如,溅射导电材料)来沉积。介电层120可沉积在存储器阵列区域104中的导电层118上。介电层120可包含介电材料。介电材料可包含例如氮化硅(sin)。介电材料可通过物理气相沉积(pvd)来沉积。部分102还可在存储器阵列区域104中包含形成在介电层120上面的介电层128。在一些实施例中,介电层128可包含介电材料。介电材料可包含例如氮化硅(sin)。可通过物理气相沉积(pvd)或化学气相沉积(cvd)来沉积介电材料。部分102还可在外围区域106中包含介电层130。在一些实施例中,介电层130可包含介电材料,例如二氧化硅(sio2)。在一些实施例中,介电材料可为旋涂式介电质(sod)。介电层130可具有距衬底108的高度与介电层128的顶表面的高度相同的顶表面。介电层128及130的顶表面可彼此相邻。部分102可包含横跨存储器阵列区域104及外围区域106的介电层132。介电层132可安置在介电层128及130上。在一些实施例中,介电层132可包含介电材料。介电材料可包含例如氮化硅(sin)。可通过物理气相沉积(pvd)或化学气相沉积(cvd)来沉积介电材料。在一些实施例中,介电层132的厚度可小

于互连件140a及140b的高度。

36.图3是根据本公开的实施例的半导体装置300的部分302的一个示意性结构的竖直横截面图的图。在一些实施例中,半导体装置300的部分302可为用于制作图1的半导体装置100的部分102的中间结构。在一些实施例中,可通过对图2的半导体装置200的部分202执行一或多个制作工艺来制作半导体装置300的部分302。部分302可在存储器阵列区域104中包含开口304a及304b以及位线结构122。可移除导电材料204的部分、介电层116的部分、导电层118、介电层120以及在导电材料204的部分上面的介电层128及132以提供开口304a及304b以及在开口304a与304b之间提供位线结构122。例如,使用光刻,掩模(未展示)可安置在位线结构122的图案中,其覆盖位于位线结构122上面的介电层128及132。可暴露未被掩模覆盖的介电层132的区域以用于蚀刻。例如,蚀刻可为干法蚀刻或湿法蚀刻。在一些实施例中,可执行干法蚀刻直到蚀刻被隔离结构152及有源区域110停止。因此,可移除未被掩模覆盖的导电材料204、介电层116、导电层118、介电层120以及介电层128及132的部分。在蚀刻后工艺(例如,干法灰化及湿法清洁)中,可移除掩模。位结构122可包含位线触点124及位线126,所述位线触点为位于有源区域110上的导电材料204的部分,所述位线为位于位线触点124上的导电层118的部分。

37.图4是根据本公开的实施例的半导体装置400的部分402的一个示意性结构的竖直横截面图的图。在一些实施例中,半导体装置400的部分402可为用于制作图1的半导体装置100的部分102的中间结构。在一些实施例中,可通过对图3的半导体装置300的部分302执行一或多个制作工艺来制作半导体装置400的部分402。半导体装置400可包含安置在图3的部分302上的介电层404。介电层404可横跨存储器阵列区域104及外围区域106覆盖介电层132。介电层404可沉积在存储器阵列区域104中的开口304a及304b中以覆盖开口304a及304b的内表面。因此,可形成开口406a及406b。在一些实施例中,介电层404可包含介电材料。介电材料可包含例如碳氧化硅(sioc)、氧化硅(sio2)或氮化硅(sin),或其组合。可通过物理气相沉积(pvd)或化学气相沉积(cvd)来沉积介电材料。在一些实施例中,覆盖位线结构122以与图1中的电容器触点136a及136b绝缘的绝缘体134可包含介电层404的部分及位于位结构122上面的介电层128的部分。

38.图5是根据本公开的实施例的半导体装置500的部分502的一个示意性结构的竖直横截面图的图。在一些实施例中,半导体装置500的部分502可为用于制作图1的半导体装置100的部分102的中间结构。在一些实施例中,可通过对图4的半导体装置400的部分402执行一或多个制作工艺来制作半导体装置500的部分502。可移除位于介电层132上的介电层404。可藉由蚀刻移除位于开口406a及406b底部处的介电层404。此外,也可通过蚀刻移除位于开口406a及406b底部下面的隔离结构152以及有源区域112a及112b。因此,可在有源区域112a及112b上形成开口506a及506b。开口506a及506b可相邻于绝缘体134。导电材料504可沉积在介电层132及绝缘体134上以填充开口506a及506b。在一些实施例中,导电材料504可包含例如多晶硅(poly-si)。在一些实施例中,导电材料504可通过物理气相沉积(pvd)(例如,溅射导电材料)来沉积。在一些实施例中,可通过化学气相沉积(cvd)来沉积导电材料504。

39.图6是根据本公开的实施例的半导体装置600的部分602的一个示意性结构的竖直横截面图的图。在一些实施例中,半导体装置600的部分602可为用于制作图1的半导体装置

100的部分102的中间结构。在一些实施例中,可通过对图5的半导体装置500的部分502执行一或多个制作工艺来制作半导体装置600的部分602。可移除介位于电层132以及开口506a及506b上面的导电材料504。在一些实施例中,可通过回蚀位于介电层132以及开口506a及506b上面的导电材料504来移除导电材料504。因此,电容器触点136a及136b可形成在开口506a及506b中。电容器触点136a及136b可分别耦合到有源区域112a及112b。电容器触点136a及136b可包含导电材料,例如多晶硅(poly-si)。电容器触点136a及136b的顶表面可具有与介电层132的顶表面的高度相同的高度。如较早参考图5所提及,在也可通过蚀刻移除位于开口406a及406b底部下面的隔离结构152以及有源区域112a及112b之后,可形成开口506a及506b。因此,在一些实施例中,电容器触点136a及136b中的每一个可在衬底108中具有底部部分。

40.在一些实施例中,半导体装置可包含互连件,例如重新分布层(rdl)。在一些实施例中,图1中的互连件140a及140b可使用镶嵌工艺形成在开口中。下文参考图7至图10描述形成互连件140a及140b的方法。图7是根据本公开的实施例的半导体装置700的部分702的一个示意性结构的竖直横截面图的图。在一些实施例中,半导体装置700的部分702可为用于制作图1的半导体装置100的部分102的中间结构。在一些实施例中,可通过对图6的半导体装置600的部分602执行一或多个制作工艺来制作半导体装置700的部分702。部分702可包含形成在图6的部分602上的介电层704。在一些实施例中,介电层704可安置在介电层132、电容器触点136a及136b以及介于电容器触点136a及136b之间的绝缘体134上。介电层704可包含介电材料。介电材料可包含例如氮化硅(sin)。可通过物理气相沉积(pvd)或化学气相沉积(cvd)来沉积介电材料。在一些实施例中,可通过原子层沉积(ald)来沉积介电层704。

41.图8是根据本公开的实施例的半导体装置800的部分802的一个示意性结构的竖直横截面图的图。在一些实施例中,半导体装置800的部分802可为用于制作图1的半导体装置100的部分102的中间结构。在一些实施例中,可通过对图7的半导体装置700的部分702执行一或多个制作工艺来制作半导体装置800的部分802。开口804a及804b可设置在存储器阵列区域104中的介电层704中。在一些实施例中,可使用光图案化及干法蚀刻来形成开口804a及804b。可执行光图案化以在介电层704上方提供图案。所述图案允许蚀刻介电层704的部分以提供开口804a及804b,所述开口从电容器触点136a及136b横向偏移。可执行存储器阵列区域104中的介电层704的干法蚀刻直到在开口804a及804b的底部处暴露电容器触点136a及136b。因此,开口804a及804b可分别以横向偏移量安置在电容器触点136a及136b上面。在一些实施例中,开口804a及804b中的每一个可具有大体上恒定的宽度。在一些实施例中,通过开口804a及804b,可执行离子注入,例如将锗(ge)离子注入到电容器触点136a及136b中。

42.可通过有源区域114上面的介电层704、132及130在外围区域106中形成开口806。在一些实施例中,介电层704的顶表面及开口804a及804b内部可被掩模覆盖。在一些实施例中,可通过化学气相沉积(cvd)沉积非晶碳材料(例如类金刚石碳)以作为掩模。可执行外围区域106中的干法蚀刻以蚀刻穿过非晶碳材料以及介电层704、132及130,直到暴露有源区域114。因此,可在有源区域114上面形成开口806。

43.图9是根据本公开的实施例的半导体装置900的部分902的一个示意性结构的竖直

横截面图的图。在一些实施例中,半导体装置900的部分902可为用于制作图1的半导体装置100的部分102的中间结构。在一些实施例中,可通过对图8的半导体装置800的部分802执行一或多个制作工艺来制作半导体装置900的部分902。在开口804a及804b中,可分别形成互连件140a及140b。在开口806中,可形成通孔144。在一些实施例中,互连件140a及140b可分别耦合到存储器单元的电容器触点136a及136b。互连件140a及140b可分别以横向偏移量安置在电容器触点136a及136b上。在一些实施例中,互连件140a及140b中的每一个可具有大体上恒定的宽度。通孔144可耦合到有源区域114。互连件140a及140b以及通孔144可包含导电材料。导电材料可包含例如钨(w)。

44.在一些实施例中,为了形成互连件140a、140b及通孔144,可形成覆盖介电层704的顶表面以及开口804a、804b及806的内表面的势垒层906。在一些实施例中,开口804a及804b中的势垒层906也可分别形成在电容器触点136a及136b上。开口806中的势垒层906也可形成在有源区域114上。在一些实施例中,可通过物理气相沉积(pvd)或化学气相沉积(cvd)同时沉积势垒层906。在一些实施例中,势垒层906可包含导电材料,例如氮化钛(tin)或钛(ti)。部分902可包含安置在势垒层906上的导电材料904。互连件140a及140b以及通孔144可包含在导电材料904中。在一些实施例中,可通过化学气相沉积(cvd)来沉积导电材料904。在一些实施例中,导电材料可包含钨(w)。

45.图10是根据本公开的实施例的半导体装置1000的部分1002的一个示意性结构的竖直横截面图的图。在一些实施例中,半导体装置1000的部分1002可为用于制作图1的半导体装置100的部分102的中间结构。在一些实施例中,可通过对图9的半导体装置900的部分902执行一或多个制作工艺来制作半导体装置1000的部分1002。在沉积导电材料904之后,可通过平坦化(例如化学机械抛光(cmp))来移除介电层704的顶表面上面的多余导电材料。因此,可在介电层704中形成互连件140a及140b。互连件140a及140b中的每一个在多个电容器触点136a及136b的每一对应的电容器触点的顶表面上具有基部。互连件140a及140b可分别以横向偏移量安置在电容器触点136a及136b上。换句话说,每一个互连件140a及140b的基部的中心远离每一对应的电容器触点136a及136b的顶表面的中心。

46.图11是根据本公开的实施例的半导体装置1100的部分1102的一个示意性结构的竖直横截面图的图。在一些实施例中,半导体装置1100的部分1102可为用于制作图1的半导体装置100的部分102的中间结构。在一些实施例中,可通过对图10的半导体装置1000的部分1002执行一或多个制作工艺来制作半导体装置1100的部分1102。部分1102可包含安置在部分1002的介电层704以及互连件140a及140b上的导电层1104。在一些实施例中,导电层1104可通过物理气相沉积(pvd)来沉积,例如以获得与通过cvd形成的导电层相比更低的电阻。在一些实施例中,导电层1104可包含导电材料,例如钨(w)。部分1102可进一步包含安置在导电层1104上的介电层1106。在一些实施例中,介电层1106可包含介电材料。介电材料可包含例如氮化硅(sin)。

47.图12是根据本公开的实施例的半导体装置1200的部分1202的一个示意性结构的竖直横截面图的图。在一些实施例中,半导体装置1200的部分1202可为用于制作图1的半导体装置100的部分102的中间结构。在一些实施例中,可通过对图11的半导体装置1100的部分1102执行一或多个制作工艺来制作半导体装置1200的部分1202。

48.可在介电层1106上安置光致抗蚀剂1204。涂层1206可安置在光致抗蚀剂1204上。

涂层1206可为抗反射涂层。涂层1206可包含凹部1214a到1214c。可通过光学光刻移除在凹部1214a到1214c下方的介电层1106及导电层1104,以形成图1中的互连件146a、146b及146c。光致抗蚀剂1208可安置在涂层1206上且涂层1210可安置在光致抗蚀剂1208上。涂层1210可为抗反射涂层。可在外围区域106中的涂层1210上形成另一光致抗蚀剂1212。因为存储器阵列区域104中的1210上面不存在光致抗蚀剂,所以可通过光学光刻移除存储器阵列区域104中的介电层1106及导电层1104。

49.在一些实施例中,涂层1206及1210可包含抗反射材料。例如,抗反射材料可为硅(si)、氧化硅(sio2)及/或碳化硅(sic)或其任一组合的混合物。在一些实施例中,硅(si)的比率可大于涂层1206及1210中的任何其它材料。例如,光致抗蚀剂1204、1208及1212可包含碳化硅(sic)。

50.图13是根据本公开的实施例的半导体装置1300的部分1302的一个示意性结构的竖直横截面图的图。在一些实施例中,半导体装置1300的部分1302可为用于制作图1的半导体装置100的部分102的中间结构。在一些实施例中,可通过对图12的半导体装置1200的部分1202执行一或多个制作工艺来制作半导体装置1300的部分1302。

51.在光学光刻之后,可移除光致抗蚀剂1204、1208及1212以及涂层1206及1210,连同介电层1106及导电层1104的部分。因此,可形成互连件146a、146b及146c。可不移除互连件146a、146b及146c上面的介电层1106。可移除未被互连件146a、146b及146c覆盖的介电层704,直到暴露互连件140a及140b的顶表面。在一些实施例中,可移除互连件140a及140b的顶部部分。因此,介电层704与互连件146a、146b及146c之间的界面可高于互连件140a及140b的顶表面。

52.图14是根据本公开的实施例的半导体装置1400的部分1402的一个示意性结构的竖直横截面图的图。在一些实施例中,半导体装置1400的部分1402可为用于制作图1的半导体装置100的部分102的中间结构。在一些实施例中,可通过对图13的半导体装置1300的部分1302执行一或多个制作工艺来制作半导体装置1400的部分1402。

53.介电层1404可形成在图13的部分1302上。在一些实施例中,介电层1404可包含介电材料。介电材料可包含例如氮化硅(sin)。可在互连件146c上面的介电层1404中形成开口。图1中的通孔148可形成在互连件146c上面的开口中。在一些实施例中,导电材料可沉积在介电层1404上。导电材料可通过物理气相沉积(pvd)来沉积,例如以获得与通过cvd形成的导电层相比更低的电阻。在一些实施例中,导电材料可包含导电材料,例如钨(w)。导电材料可填充互连件146c上面的开口。可移除未覆盖介电层1404上面的通孔148的过量导电材料。因此,如在图1中所展示,可形成介电层1404中的通孔148及通孔148上并耦合到通孔148的互连件150。

54.如上文所描述,可使用沉积介电层(例如,介电层704)、形成开口(例如,开口804a及804b)及填充开口的镶嵌工艺而不是沉积导电层及回蚀导电层的过量部分来形成重新分布层(rdl),例如在电容器触点136a及136b上面的互连件140a及140b。

55.在一些实施例中,每一重新分布层(rdl)可形成为彼此耦合的相邻导电层的两个互连件。图15是根据本公开的实施例的半导体装置1500的部分1502的一个示意性结构的竖直横截面图的图。在一些实施例中,半导体装置1500可为例如包含存储器单元的存储器装置(例如,动态随机存取存储器(dram))。每一存储器单元可包含晶体管及电容器。例如,部

分1502可包含晶体管,例如dram中的金属氧化物半导体场效应晶体管(mosfet)。

56.部分1502包含半导体装置1500的存储器阵列区域1504及外围区域1506的部分。存储器单元可安置在存储器阵列区域1504中,且外围电路可安置在外围区域1506中。在一些实施例中,半导体装置1500可包含横跨存储器阵列区域1504及外围区域1506的衬底1508。衬底1508可在存储器阵列区域1504中包含有源区域1510、有源区域1512a及1512b。衬底1508可包含在外围区域1506中的有源区域1514。部分1502可包含覆盖有源区域1510、1512a、1512b及1514的隔离结构1554。有源区域1510、1512a、1512b及1514可通过隔离结构1554彼此隔离。在一些实施例中,隔离结构1554可为包含介电材料的浅沟槽隔离(sti)。部分1502可在存储器阵列区域1504中包含位于衬底1508上的介电层1516、位于介电层1516上的导电层1518以及位于导电层1518上的介电层1520。部分1502可包含位于衬底1508的有源区域1510上的位线结构1522。位线结构1522可包含位于衬底1508的有源区域1510上的位线触点1524及位于位线触点1524上的位线1526。在一些实施例中,位线触点1524可设置在衬底1508的顶表面上。在一些实施例中,衬底1508的顶表面可具有小于衬底1508的其余部分的厚度的高度。在一些实施例中,位线1526可为导电层1518的部分。部分1502还可包含在存储器阵列区域1504中的介电层1520上面的介电层1528。部分1502还可在外围区域1506中包含介电层1530。介电层1530可具有距衬底1508的高度与介电层1528的顶表面的高度相同的顶表面。部分1502可包含分别位于有源区域1512a及1512b上的电容器触点1536a及1536b。在一些实施例中,电容器触点1536a及1536b的下部部分可在衬底1508中。在一些实施例中,电容器触点1536a及1536b的顶表面可具有距衬底1508与介电层1528及1530的顶表面相同的的高度。部分1502可进一步包含围绕位结构1522的绝缘体1534。位结构1522可通过绝缘体1534与电容器触点1536a及1536b绝缘。

57.部分1502可包含横跨存储器阵列区1504及外围区域1506的介电层1532。介电层1532可安置在介电层1528及1530以及电容器触点1536a及1536b上。部分1502可包含在电容器触点1536a及1536b上面的互连件1538a及1538b。互连件1538a及1538b可包含导电材料。部分1502可包含横跨存储器阵列区1504及外围区域1506的介电层1540。在一些实施例中,介电层1540可安置在介电层1532、互连件1538a及1538b以及介于互连件1538a与1538b之间的绝缘体1534上。部分1502可在介电层1540中包含互连件1542a及1542b。互连件1542a及1542b可安置在互连件1538a及1538b上。因此,互连件1538a及1538b可分别安置在电容器触点1536a及1536b与互连件1542a及1542b之间。互连件1542a及1542b可分别以横向偏移量lo'安置在电容器触点1536a及1536b上的互连件1538a及1538b上。在一些实施例中,互连件1542a及1542b中的每一个可具有宽度w2',所述宽度大于互连件1538a及1538b以及电容器触点1536a及1536b的上部部分中的每一个的宽度w1'。互连件1542a及1542b可分别耦合到互连件1538a及1538b。

58.部分1502还可包含安置在有源区域1514上的通孔1546。通孔1546可穿过介电层1530、1532及1540安置。部分1502可包含横跨存储器阵列区1504及外围区域1506的介电层1544。部分1502可在介电层1544中包含互连件1548a、1548b及1548c。互连件1548c可安置在通孔1546上。部分1502还可包含位于介电层1544中的通孔1550。通孔1550可安置在互连件1548c上。部分1502可进一步包含安置在介电层1544及通孔1550上的互连件1552。在其它示例中可包含额外的、更少的及/或不同的组件。

59.下文参考图16至图21描述形成例如根据实施例的半导体存储器装置1500的设备的方法。在一些实施例中,导电层可为重新分布层(rdl)。每一图式中的每一部分的尺寸及尺寸比不一定与实际的半导体装置的尺寸及尺寸比一致。

60.在图15中的衬底1508的有源区域1510、1512a及1512b上形成位线结构1522及电容器触点1536a及1536b可类似于先前参考图2到6所描述且在图2到6中展示的衬底108的有源区域110、112a及112b上形成位线结构122及电容器触点136a及136b,因此为了简洁省略对形成位线结构1522及电容器触点1536a及1536b的描述。

61.图16是根据本公开的实施例的半导体装置1600的部分1602的一个示意性结构的竖直横截面图的图。在一些实施例中,半导体装置1600的部分1602可为用于制作图15的半导体装置1500的部分1502的中间结构。部分1602包含半导体装置200的存储器阵列区1504及外围区域1506的部分。可在介电层1532的存储器阵列区域1504中提供开口1604a及1604a。在一些实施例中,可使用光图案化及干法蚀刻来形成开口1604a及1604a。可执行存储器阵列区域104中的干法蚀刻以移除电容器触点1536a及1536b的顶部部分。因此,开口1604a及1604a可分别安置在其电容器触点1536a及1536b的剩余部分上面。在一些实施例中,通过开口1604a及1604a,离子注入,例如将锗(ge)离子注入到电容器触点1536a及1536b中。

62.图17是根据本公开的实施例的半导体装置1700的部分1702的一个示意性结构的竖直横截面图的图。在一些实施例中,半导体装置1700的部分1702可为用于制作图15的半导体装置1500的部分1502的中间结构。在一些实施例中,可通过对图16的半导体装置1600的部分1602执行一或多个制作工艺来制作半导体装置1700的部分1702。部分1702可包含安置在介电层1532上及开口1604a及1604b内部的导电材料1704。图15中的互连件1538a及1538b可包含在导电材料1704中。在一些实施例中,可通过化学气相沉积(cvd)来沉积导电材料1704。在一些实施例中,导电材料可包含钨(w)。在一些实施例中,在沉积导电材料1704之前,可在介电层1532上及开口1604a及1604b内部安置势垒层1706。形成势垒层1706可类似于先前参考图9所描述且在图9中所展示的形成势垒层906,因此为了简洁省略对形成势垒层的描述。

63.图18是根据本公开的实施例的半导体装置1800的部分1802的一个示意性结构的竖直横截面图的图。在一些实施例中,半导体装置1800的部分1802可为用于制作图15的半导体装置1500的部分1502的中间结构。在一些实施例中,可通过对图17的半导体装置1700的部分1702执行一或多个制作工艺来制作半导体装置1800的部分1802。在沉积导电材料1704之后,可通过平坦化(例如化学机械抛光(cmp))来移除介电层1532的顶表面上面的多余导电材料。因此,可在介电层1532中形成互连件1538a及1538b。互连件1538a及1538b可分别安置在电容器触点1536a及1536b上,以替换被移除的电容器触点1536a及1536b的顶部部分。

64.图19是根据本公开的实施例的半导体装置1900的部分1902的一个示意性结构的竖直横截面图的图。在一些实施例中,半导体装置1900的部分1902可为用于制作图15的半导体装置1500的部分1502的中间结构。在一些实施例中,可通过对图18的半导体装置1800的部分1802执行一或多个制作工艺来制作半导体装置1900的部分1902。部分1902可包含形成在图18的部分1802上的介电层1904。在一些实施例中,介电层1904可安置在介电层1532

及互连件1538a及1538b以及介于互连件1538a与1538b之间的绝缘体134上。介电层1904可包含介电材料。介电材料可包含例如氮化硅(sin)。可通过物理气相沉积(pvd)或化学气相沉积(cvd)来沉积介电材料。在一些实施例中,可通过原子层沉积(ald)来沉积介电层1904。

65.图20是根据本公开的实施例的半导体装置2000的部分2002的一个示意性结构的竖直横截面图的图。在一些实施例中,半导体装置2000的部分2002可为用于制作图15的半导体装置1500的部分1502的中间结构。在一些实施例中,可通过对图19的半导体装置1900的部分1902执行一或多个制作工艺来制作半导体装置2000的部分2002。可移除介电层1904的顶部部分以形成介电层2004。可在介电层2004的存储器阵列区域1504中提供开口2008a及2008b。在一些实施例中,可使用光图案化及干法蚀刻来形成开口2008a及2008b。可执行光图案化以在介电层1904上方提供图案。所述图案允许蚀刻从互连件1538a及1538b横向偏移的介电层2004。可执行存储器阵列区域1504中的介电层2004的干法蚀刻直到暴露互连件1538a及1538b。因此,开口2008a及2008b可分别以横向偏移量安置在互连件1538a及1538b上面。在一些实施例中,通过开口2008a及2008b,可执行离子注入,例如将锗(ge)离子注入到电容器触点1536a及1536b中。

66.开口2006可通过有源区域1514上面的介电层2004、1532及1530形成在外围区域1506中。在一些实施例中,介电层2004的顶表面以及开口2008a及2008b内部可被掩模覆盖。在一些实施例中,非晶碳材料,例如类金刚石碳,可通过化学气相沉积(cvd)沉积以作为掩模。可执行外围区域1506中的干法蚀刻以蚀刻穿过非晶碳材料以及介电层2004、1532及1530直到暴露有源区域1514。因此,可在有源区域1514上面形成开口2006。

67.图21是根据本公开的实施例的半导体装置2100的部分2102的一个示意性结构的竖直横截面图的图。在一些实施例中,半导体装置2100的部分2102可为用于制作图15的半导体装置1500的部分1502的中间结构。在一些实施例中,可通过对图20的半导体装置2000的部分2002执行一或多个制作工艺来制作半导体装置2100的部分2102。在开口2008a及2008b中,可分别形成互连件1542a及1542b。在开口2006中,可形成通孔1546。在一些实施例中,互连件1542a及1542b可分别耦合到互连件1538a及1538b。互连件1542a及1542b可分别以横向偏移量安置在互连件1538a及1538b上。通孔1546可耦合到有源区域1514。互连件1542a及1542b以及通孔1546可包含导电材料,所述导电材料为与互连件1538a及1538b中包含的导电材料相同的导电材料。导电材料可包含例如钨(w)。

68.为了形成互连件1542a及1542b以及通孔1546,可形成覆盖介电层2004的顶表面以及开口2008a、2008b及2006的内表面的势垒层2106。在一些实施例中,开口2008a及2008b中的势垒层2106也可分别形成在互连件1538a及1538b上。开口2006中的势垒层2106也可形成在有源区域1514上。在一些实施例中,可通过物理气相沉积(pvd)或化学气相沉积(cvd)同时沉积势垒层2106。在一些实施例中,势垒层2106可包含导电材料,例如氮化钛(tin)或钛(ti)。部分2102可包含安置在势垒层2106上的导电材料2104。互连件1542a及1542b以及通孔1546可包含在导电材料2104中。在一些实施例中,可通过化学气相沉积(cvd)来沉积导电材料2104。在一些实施例中,导电材料可包含钨(w)。在沉积导电材料2104之后,可通过平坦化(例如化学机械抛光(cmp))来移除介电层2004的顶表面上面的多余导电材料。因此,可在介电层2004中形成互连件1542a及1542b以及通孔1546。

69.在介电层1544中形成互连件1548a、1548b及1548c以及在互连件1548c上面的通孔

1550,及在图15中的通孔1550上面形成互连件1552可类似于先前参考图11到14所描述且在图11到14中所展示在介电层142中形成互连件146a、146b及146c,及在通孔148上面形成互连件150,因此为了简洁省略对形成互连件1548a、1548b及1548c、通孔1550以及互连件1552的描述。

70.如上文所描述,每一重新分布层(rdl)可形成为相邻的导电层的两个互连件,例如互连件1538a及1542a,或彼此耦合的互连件1538b及1542b。因为在电容器触点件1536a与互连件1538a之间或在电容器触点件1536b与互连件1538b之间不存在横向偏移,所以在电容器触点件1536a与互连件1538a之间的界面或电容器触点1536b与互连件1538b之间的界面处的导电效率可增加。互连件1538a与1542a之间的界面或互连件1538b与1542b之间的界面处的电阻可忽略不计,因为互连件1538a、1538b、1542a及1542b包含相同的导电材料。因此,可增加电容器触点1536a与互连件1538a及1542a之间的导电效率以及电容器触点1536b与互连件1538b及1542b之间的导电效率。

71.已公开在电容器触点上面形成互连件(例如重新分布层(rdl))的各种实施例。电容器触点上面的互连件可使用镶嵌工艺,在电容器触点上面形成介电层,在介电层中形成从电容器触点横向偏移的开口,及使用物理气相沉积(pvd)(例如溅射)在开口中填充导电材料来形成。

72.尽管在本公开中已公开各种实施例,但所属领域的技术人员将理解,本公开的范围超出了具体公开的实施例,延伸到其它替代实施例及/或用途及其明显的修改及等同物。另外,基于本公开,所属领域的技术人员将容易明了在本公开的范围内的其它修改。还预期,可进行实施例的具体特征及方面的各种组合或子组合且仍然在本公开的范围内。应该理解的是,所公开的实施例的各种特征及方面可以彼此组合或替代以便形成不同实施例。因此,意味着本公开的至少一些的范围不应受到上文所描述特定的所公开的实施例的限制。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。