1.本发明涉及光电半导体技术领域,具体涉及一种半导体激光器的热沉和芯片上互镀金锡薄膜的方法。

背景技术:

2.随着当今光电半导体技术的发展,半导体大功率器件通常将芯片焊接固定在散热能力更好的热沉基板上,实现散热。而芯片焊接,一方面可以为芯片提供机械连接以及电连接,另一方面可以为芯片提供良好的散热通道,因此,芯片焊接是半导体大功率器件热设计中非常关键的一道工序。

3.常见的钎焊材料包括软焊料和硬焊料,软焊料可以为铟、锡等,硬焊料可以为金锡合金、金锗合金、锡银铜等。对于合金焊料而言,不同的金属与含量往往对于界面间的润湿性和可靠性起到不同的作用。其中,金锡合金由于具备良好的导热性、稳定的化学性能、耐热冲击疲劳、耐腐蚀等性能,成为了焊接的优选材料。

4.目前,传统的焊接工艺一般是将金锡合金预制在热沉上,或者使用金锡焊料片键合,由此可使热沉上的金锡与芯片上的金层之间形成ausn-au界面。由于ausn合金焊料与au层之间的界面反应形成了金属间化合物,而随着焊点热效应引起金属间化合物的长大,反而会降低焊点的热疲劳性能,使其可靠性降低,且金属间化合物的异常长大,降低了焊点的力学性能。因此,传统的焊接工艺形成的ausn-au界面的界面反应及焊点的剪切强度还有待进一步的提高,以期提高焊料的使用寿命。

5.为了进一步提高剪切强度,发明人对传统的焊接工艺进行改进,认为若能在芯片表面和热沉表面预制金锡薄膜,这样的优点一是充分利用芯片制造工艺流程及产品表面质量(表面粗糙度更好及镀金浸润性佳)比传统金属加工更好,且在芯片工艺流程中表面沉积金锡也可以减少生产环节,可以使得芯片与被键合热沉之间更容易焊接。优点二是芯片和热沉表面都是相同比例的金锡合金,在真空共晶过程中是ausn-ausn界面更具有更好的浸润性,更有利于金锡的固溶共晶,键合质量好,相对于传统的热沉上金锡与芯片金层的ausn-au界面的键合更有利,即ausn-ausn浸润界面与ausn-au界面更有利于焊料的铺展、浸润、键合,这样ausn-ausn浸润界面对热沉表面粗糙度等要求也可适当降低,减少制造成本且键合后的结合力远远优于传统的结构。

技术实现要素:

6.为解决上述技术问题,本发明的目的在于提供一种半导体激光器的热沉和芯片上互镀金锡薄膜的方法。

7.为实现上述目的,本发明的技术方案如下。

8.一种热沉和芯片上互镀金锡薄膜的方法,包括以下步骤:

9.s1、采用物理气相沉积的方式在芯片和热沉的表面逐层镀制合金薄膜,得到镀膜芯片和镀膜热沉;所述合金薄膜的材料为金和锡;所述镀膜芯片和所述镀膜热沉的表层材

料为金;

10.s2、将所述镀膜芯片置于所述镀膜热沉上,然后进行真空共晶退火处理,使所述镀膜芯片与所述镀膜热沉之间的浸润界面相互扩散并键合,制得互镀金锡薄膜的热沉-芯片结构。

11.进一步,所述合金薄膜中,金和锡的体积比为1~9:9~1。

12.更进一步,所述合金薄膜中,金和锡的体积比为1:9~4:1。

13.进一步,所述合金薄膜是采用物理气相沉积的方式分别在芯片和热沉的表面交替镀制金层和锡层;镀制金层的速率为2~10a/s;镀制锡层的速率为1~5a/s。

14.进一步,所述合金薄膜的镀层数为2~99层,厚度为0.3~10μm。

15.进一步,所述芯片在镀制所述合金薄膜之前,还包括采用电镀或化学镀在所述芯片的p面和n面以及所述热沉的表面制备钛金层、镍金层、铬金层或钛铂金层。

16.更进一步,所述芯片的p面和n面以及所述热沉的表层材料为金或铂金。

17.进一步,所述真空共晶退火处理的温度为100~350℃,时间为1~200min。既可以热沉、芯片分别单独退火,也可以将二者叠摞在一起退火,主要的目的是促进金锡互扩散,也可以真空镀膜结束后直接在镀膜设备中进行退火处理。

18.进一步,所述芯片的基底材料为砷化镓、磷化铟、硅基、碳化硅、氮化镓、金刚石中的任意一种。

19.进一步,所述热沉的材料为cuw合金、陶瓷、铜金刚石、陶瓷覆铜材料dbc和dpc中的任意一种。

20.本发明的有益效果:

21.1、本发明通过在热沉和芯片的表面分别制备金锡合金薄膜,在回流或贴片键合过程中,由于共晶过程ausn-ausn界面键合更充分,比传统热沉ausn与芯片表面的镀金层的ausn-au界面更具亲润性,产品破坏性推力分析,断面层结合牢固、推力更大。

22.2、与传统的预制金锡工艺在热沉上相比,传统热沉需要制备金锡,需要表面的粗糙度尽量控制在0.4um以内,主要考虑到若粗糙度大,金锡熔化后全部先流淌在沟壑处,且与芯片表面的金不浸润导致焊接不良。而采用本发明在芯片和热沉表面都沉积有金锡焊料,由于两个界面都是金锡,且此时键合界面ausn-ausn熔化呈现互相熔化渗透彼此,对于热沉和芯片表面粗糙度的要求可适当放宽,更有利于生产过程中的加工,对于设备和工艺的要求也可适当降低,同时可提升批量生产的良率,节约成本。

23.3、本发明在真空环境下制备的金锡合金焊料表面清洁无污染且抗氧化性能好、具有合金薄膜结合力牢固,抗热疲劳和蠕变性能优良等优点,交替蒸发镀膜其焊料成分可控、厚度一致性好、金锡共晶时互扩散良好。

24.4、本发明是在传统工艺仅在热沉上制备金锡的方式的基础上,设计一种在热沉和芯片表面分别都镀金锡相结合的方法,原设计厚度可降低一半,这样的优点是芯片和热沉表面都是相同比例的金锡,在真空共晶过程中是ausn-ausn界面更具有更好的浸润性,更有利于金锡的固溶共晶,键合质量好,相对于传统的热沉上金锡与芯片金层的ausn-au界面的键合更有利,即ausn-ausn浸润界面,与ausn-au界面相比,更有利于焊料的铺展、浸润、键合,这样ausn-ausn浸润界面对热沉表面粗糙度等要求也可适当降低,减少制造成本且键合后的结合力远远优于传统的结构。

附图说明

25.图1是采用本发明实施例1的方法在cuw热沉表面镀制金锡的结构示意图。

26.图2是采用本发明实施例1的方法在芯片表面镀制金锡的结构示意图。

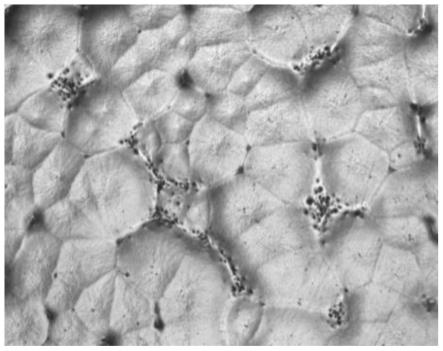

27.图3是采用实施例1的方法将cuw热沉和芯片在表面镀制金锡后进行进行真空共晶退火处理制备的产品在浸润界面处挤出熔化形貌图。

28.图4是采用对比例1的方法将cuw热沉表面镀制金锡,芯片表面未镀金锡后进行真空共晶退火处理制备的产品在浸润界面处挤出熔化形貌图。

29.图5是采用芯片金锡和热沉金锡焊接后的产品1和芯片上无金锡,仅热沉有金锡焊接后产品2,分别3pcs产品采用德国dage4000推力机分析产品焊接质量的推力数据对比图。

具体实施方式

30.为了使本发明的目的、技术方案及优点更加清楚明白,以下结合实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。

31.基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

32.下述各实施例中所述实验方法如无特殊说明,均为常规方法;所述试剂和材料,如无特殊说明,均可在市场上购买得到。

33.一种热沉和芯片上互镀金锡薄膜的方法,包括以下步骤:

34.s1、在热沉的表面采用pvd技术镀制钛铂金层,其中,钛是粘结层,厚度控制在0.01~5um,速率1~10a/s,铂是阻隔层,主要作用是当表面金锡熔融后不要向基材内部扩散,同时基材内部元素因铂的阻隔不能向金锡焊料中扩散而造成焊料“中毒”失效。

35.s2、采用pvd物理气相沉积的方式在s1的热沉表面交替蒸发镀制金层和锡层,镀制金层的速率为2~10a/s,镀制锡层的速率为1~5a/s;最终在热沉的表面逐层镀制金锡合金薄膜,得到镀膜热沉;所述镀膜热沉的表层材料为金。合金薄膜的镀层数为2~499层,厚度为0.3~10μm;所述合金薄膜中金和锡的体积比为1:9~4:1。

36.s3、在芯片的p面和n面采用pvd技术分别镀制钛铂金层,其中,钛是粘结层,厚度控制在0.01~5um,速率1~10a/s,铂是阻隔层,主要作用是当表面金锡熔融后不要向基材内部扩散,同时基材内部元素因铂的阻隔不能向金锡焊料中扩散而造成焊料“中毒”失效。

37.s4、采用pvd物理气相沉积的方式在s3的芯片的p面和n面分别交替蒸发镀制金层和锡层,镀制金层的速率为2~10a/s,镀制锡层的速率为1~5a/s;最终在芯片的p面和n面分别逐层镀制金锡合金薄膜,得到镀膜芯片;所述镀膜芯片的p面和n面的表层材料均为金。合金薄膜的镀层数为2~499层,厚度为0.3~10μm;所述合金薄膜中金和锡的体积比为1:9~4:1。

38.其中,镀制金锡合金薄膜的厚度需求可以根据实际要求而定。所述金锡厚度中的金体积与锡体积按1:9~9:1之间波动,所述焊料材料中的金体积与锡体积对应于处于二元相图中热力学平衡中的金和锡的共晶点(au80%:sn20%与au10%:sn90%)。

39.s5、将s4的镀膜芯片置于s2的镀膜热沉上,并使镀制金锡合金薄膜相互贴合,然后进行真空共晶退火处理,真空共晶退火处理的温度为100~350℃,时间为1~200min,使镀

膜芯片与镀膜热沉之间的浸润界面相互扩散并键合,制得互镀金锡薄膜的热沉-芯片结构。

40.本发明的下述实施例中,所述的芯片的基底材料可以选择砷化镓、磷化铟、硅基、碳化硅、氮化镓、金刚石中的任意一种。所述的热沉的材料可以选择cuw合金、陶瓷、铜金刚石、陶瓷覆铜材料dbc、dpc中的任意一种,当然也可拓展到其他材质的热沉。芯片和热沉均为现有技术,此处不再赘述。

41.本发明的下述实施例中,所述的pvd物理气相沉积制备,涵盖磁控溅射镀膜、电子束蒸发镀膜、电阻蒸发镀膜或采用两两组合,可以根据实际需求选择。

42.下面对热沉和芯片上互镀金锡薄膜的方法进行具体说明。

43.实施例1

44.一种热沉和芯片上互镀金锡薄膜的方法,包括以下步骤:

45.s1、在热沉的表面采用pvd技术镀制钛铂金层,其中,钛是粘结层,厚度控制在1um,速率5a/s,铂是阻隔层,主要作用是当表面金锡熔融后不要向基材内部扩散,同时基材内部元素因铂的阻隔不能向金锡焊料中扩散而造成焊料“中毒”失效。

46.s2、采用pvd物理气相沉积的方式在s1的热沉表面交替蒸发镀制金层和锡层,镀制金层的速率为5a/s,镀制锡层的速率为3a/s;最终在热沉的表面逐层镀制金锡合金薄膜,得到镀膜热沉;所述镀膜热沉的表层材料为金。合金薄膜的镀层数为220层,厚度为8μm;所述合金薄膜中金和锡的体积比为1:9。

47.s3、在芯片的p面和n面采用pvd技术分别镀制钛铂金层,其中,钛是粘结层,厚度控制在1um,速率5a/s,铂是阻隔层,主要作用是当表面金锡熔融后不要向基材内部扩散,同时基材内部元素因铂的阻隔不能向金锡焊料中扩散而造成焊料“中毒”失效。

48.s4、采用pvd物理气相沉积的方式在s3的芯片的p面和n面分别交替蒸发镀制金层和锡层,镀制金层的速率为5a/s,镀制锡层的速率为3a/s;最终在芯片的p面和n面分别逐层镀制金锡合金薄膜,得到镀膜芯片;所述镀膜芯片的p面和n面的表层材料均为金。合金薄膜的镀层数为220层,厚度为8μm;所述合金薄膜中金和锡的体积比为1:9。

49.s5、将s4的镀膜芯片置于s2的镀膜热沉上,并使镀制金锡合金薄膜相互贴合,然后进行真空共晶退火处理,真空共晶退火处理的温度为250℃,时间为15min,使镀膜芯片与镀膜热沉之间的浸润界面相互扩散并键合,制得互镀金锡薄膜的热沉-芯片结构。

50.实施例2

51.一种热沉和芯片上互镀金锡薄膜的方法,包括以下步骤:

52.s1、在热沉的表面采用pvd技术镀制钛铂金层,其中,钛是粘结层,厚度控制在5um,速率10a/s,铂是阻隔层,主要作用是当表面金锡熔融后不要向基材内部扩散,同时基材内部元素因铂的阻隔不能向金锡焊料中扩散而造成焊料“中毒”失效。

53.s2、采用pvd物理气相沉积的方式在s1的热沉表面交替蒸发镀制金层和锡层,镀制金层的速率为10a/s,镀制锡层的速率为5a/s;最终在热沉的表面逐层镀制金锡合金薄膜,得到镀膜热沉;所述镀膜热沉的表层材料为金。合金薄膜的镀层数为99层,厚度为10μm;所述合金薄膜中金和锡的体积比为4:1。

54.s3、在芯片的p面和n面采用pvd技术分别镀制钛铂金层,其中,钛是粘结层,厚度控制在5um,速率10a/s,铂是阻隔层,主要作用是当表面金锡熔融后不要向基材内部扩散,同时基材内部元素因铂的阻隔不能向金锡焊料中扩散而造成焊料“中毒”失效。

55.s4、采用pvd物理气相沉积的方式在s3的芯片的p面和n面分别交替蒸发镀制金层和锡层,镀制金层的速率为10a/s,镀制锡层的速率为5a/s;最终在芯片的p面和n面分别逐层镀制金锡合金薄膜,得到镀膜芯片;所述镀膜芯片的p面和n面的表层材料均为金。合金薄膜的镀层数为99层,厚度为10μm;所述合金薄膜中金和锡的体积比为4:1。

56.s5、将s4的镀膜芯片置于s2的镀膜热沉上,并使镀制金锡合金薄膜相互贴合,然后进行真空共晶退火处理,真空共晶退火处理的温度为350℃,时间为200min,使镀膜芯片与镀膜热沉之间的浸润界面相互扩散并键合,制得互镀金锡薄膜的热沉-芯片结构。

57.实施例3

58.一种热沉和芯片上互镀金锡薄膜的方法,包括以下步骤:

59.s1、在热沉的表面采用pvd技术镀制钛铂金层,其中,钛是粘结层,厚度控制在0.01um,速率1a/s,铂是阻隔层,主要作用是当表面金锡熔融后不要向基材内部扩散,同时基材内部元素因铂的阻隔不能向金锡焊料中扩散而造成焊料“中毒”失效。

60.s2、采用pvd物理气相沉积的方式在s1的热沉表面交替蒸发镀制金层和锡层,镀制金层的速率为2a/s,镀制锡层的速率为1a/s;最终在热沉的表面逐层镀制金锡合金薄膜,得到镀膜热沉;所述镀膜热沉的表层材料为金。合金薄膜的镀层数为2层,厚度为0.3μm;所述合金薄膜中金和锡的体积比为1:1。

61.s3、在芯片的p面和n面采用pvd技术分别镀制钛铂金层,其中,钛是粘结层,厚度控制在0.01um,速率1a/s,铂是阻隔层,主要作用是当表面金锡熔融后不要向基材内部扩散,同时基材内部元素因铂的阻隔不能向金锡焊料中扩散而造成焊料“中毒”失效。

62.s4、采用pvd物理气相沉积的方式在s3的芯片的p面和n面分别交替蒸发镀制金层和锡层,镀制金层的速率为2a/s,镀制锡层的速率为1a/s;最终在芯片的p面和n面分别逐层镀制金锡合金薄膜,得到镀膜芯片;所述镀膜芯片的p面和n面的表层材料均为金。合金薄膜的镀层数为2层,厚度为0.3μm;所述合金薄膜中金和锡的体积比为1:1。

63.s5、将s4的镀膜芯片置于s2的镀膜热沉上,并使镀制金锡合金薄膜相互贴合,然后进行真空共晶退火处理,真空共晶退火处理的温度为100℃,时间为1min,使镀膜芯片与镀膜热沉之间的浸润界面相互扩散并键合,制得互镀金锡薄膜的热沉-芯片结构。

64.对比例1

65.一种热沉和芯片上互镀金锡薄膜的方法,包括以下步骤:

66.s1、在热沉的表面采用pvd技术镀制钛铂金层,其中,钛是粘结层,厚度控制在1um,速率5a/s,铂是阻隔层,主要作用是当表面金锡熔融后不要向基材内部扩散,同时基材内部元素因铂的阻隔不能向金锡焊料中扩散而造成焊料“中毒”失效。

67.s2、采用pvd物理气相沉积的方式在s1的热沉表面交替蒸发镀制金层和锡层,镀制金层的速率为5a/s,镀制锡层的速率为3a/s;最终在热沉的表面逐层镀制金锡合金薄膜,得到镀膜热沉;所述镀膜热沉的表层材料为金。合金薄膜的镀层数为220层,厚度为8μm;所述合金薄膜中金和锡的体积比为1:9。

68.s3、在芯片的p面和n面采用pvd技术分别镀制钛铂金层,其中,钛是粘结层,厚度控制在1um,速率5a/s,铂是阻隔层,主要作用是当表面金锡熔融后不要向基材内部扩散,同时基材内部元素因铂的阻隔不能向金锡焊料中扩散而造成焊料“中毒”失效。

69.s4、将s3的芯片置于s2的镀膜热沉上,并使镀制金锡合金薄膜相互贴合,然后进行

真空共晶退火处理,真空共晶退火处理的温度为250℃,时间为15min,制得热沉-芯片结构。

70.实施例1~3的方法产生的效果基本相同,因此仅以实施例1和对比例1制备的产品进行效果对比。

71.试样包括:试样1、试样2和试样3。

72.试样1是实施例1制备的cuw热沉表面镀金锡,数量6pcs,其结构如图1所示。

73.试样2是实施例1制备的芯片表面镀金锡,数量3pcs,其结构如图2所示。

74.试样3是在芯片表面未镀金锡,数量3pcs。

75.实验组别包括:实验组和对照组。

76.实验组:将试样1和试样2进行真空退火处理,制得实施例1的产品1。

77.对照组:将试样1和试样3进行真空退火处理,制得对比例1的产品2。

78.产品1的在浸润界面处挤出熔化形貌图如图3,产品2的在浸润界面处挤出熔化形貌图如图4,产品的键合质量及性能表征采用国际认可的德国dage4000设备。

79.图5是产品1和产品2以剪切推力判定产品焊接质量的对比柱形图,其剪切推力数据对比结果见表1。

80.表1产品1和产品2的剪切推力数据对比结果

81.试验次数123平均值产品1的剪切推力(kgf)43.9542.2947.9544.73产品2的剪切推力(kgf)5.585.365.615.52

82.根据图3至图5可知,采用热沉和芯片表面都镀制金锡的产品1,表面焊料熔化饱满,且两侧有明显的焊料挤出,且熔化界面的金锡形貌呈推力验证结合力44.73kgf,比传统热沉上镀金锡的产品2提高5~8倍,说明采用热沉和芯片均镀制金锡的产品键合焊接效果明显提升。

83.以上仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。