1.本实用新型总体上涉及超高频电磁波发射/接收器件。

背景技术:

2.超高频电磁波发射/接收器件可包括结合到包括超高频电磁波发射/接收天线的支撑件的集成电路芯片,所述集成电路芯片和所述支撑件放置在包含超高频电磁波从/到所述天线的导引件的封装中。

3.希望在天线和波导之间传输超高频电磁波期间的损耗尽可能小。还希望器件的制造成本尽可能低。

技术实现要素:

4.本公开的目的是提供电路器件,以至少部分地解决现有技术中存在的上述问题。

5.本公开的一方面提供了一种电路器件,包括:多层有机衬底;集成电路芯片,倒装组装在所述多层有机衬底上;以及封装,包括第一腔体,所述第一腔体包含所述多层有机衬底和所述集成电路芯片,所述第一腔体被配置为通过通道与第二腔体连通,所述第二腔体形成用于电磁波的波导,所述封装包括:天线,在所述衬底中并且耦合到所述集成电路芯片,所述天线在所述第一腔体中延伸并部分地延伸到所述第二腔体中。

6.根据一个或多个实施例,其中所述第一腔体包括第一凹陷,所述集成电路芯片位于所述第一凹陷中。

7.根据一个或多个实施例,其中所述第一腔体包括位于所述第二腔体和所述第一凹陷之间的第二凹陷。

8.根据一个或多个实施例,其中所述多层有机衬底包括所述第一腔体中的主要部分和从所述主要部分延伸到所述通道中并穿透进入所述第二腔体中的突起。

9.根据一个或多个实施例,其中所述衬底中的电绝缘支撑件包括:相对的第一表面和第二表面、在所述第一表面上延伸的导电轨、以及覆盖所述导电轨的电绝缘层。

10.根据一个或多个实施例,其中所述多层有机衬底进一步包括涂层,所述涂层包括覆盖所述电绝缘层的石墨烯层。

11.根据一个或多个实施例,其中所述多层有机衬底包括在所述第二腔体中的突起上的所述天线,并且其中所述多层有机衬底包括将所述天线耦合到所述集成电路芯片的导电线,其中所述涂层不覆盖所述第一腔体中的所述导电线。

12.本公开的又一方面提供了一种电子器件,包括:封装,具有与第二表面相对的第一表面;所述封装中的第一腔体;第一多个导电层,在所述第一腔体中,所述第一多个导电层相对于第二表面更靠近所述第一表面;第一绝缘层,在所述第一腔体中,所述第一绝缘层被所述第一多个导电层与所述第一表面间隔开;第二多个导电层,在所述第一腔体中,所述第二多个导电层相对于所述第一表面更靠近所述第二表面;第二腔体,在所述封装中,所述第二腔体相对于所述第一表面更靠近所述第二表面;集成电路芯片,在所述第一绝缘层上;波

导,耦合到所述集成电路并且至少部分地在所述第二腔体中;以及多个电连接器,从所述封装的一侧延伸,所述波导从所述封装的与所述一侧不同的一侧延伸。

13.根据一个或多个实施例,其中所述第一多个导电层、所述第一绝缘层和所述第二多个导电层是在所述封装中的衬底。

14.根据一个或多个实施例,其中所述多个电连接器从所述封装延伸到外部环境中。

15.根据一个或多个实施例,其中所述第二腔体从所述衬底延伸到所述封装的边缘。

16.利用本公开的实施例有利地减小在天线和波导之间传输超高频电磁波期间的损耗。

附图说明

17.前述特征和优点以及其他特征和优点将在以下具体实施例的描述中参考附图以说明而非限制的方式给出,在附图中:

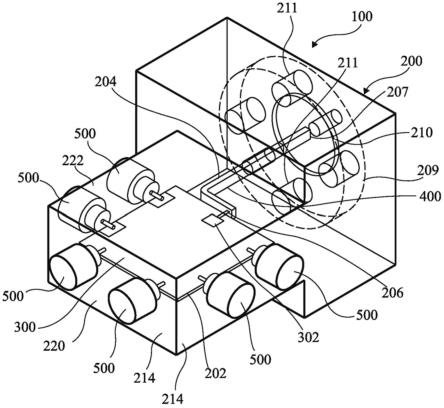

18.图1是超高频电磁波发射/接收器件的实施例的部分简化透视图;

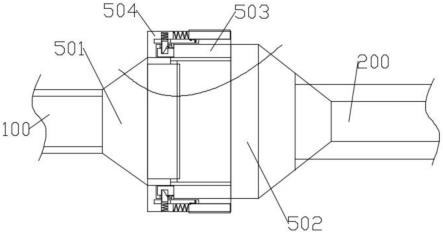

19.图2是图1的器件的局部简化剖视图;

20.图3是图1的器件的部分简化剖视图,示出了器件的多层有机衬底的实施例;

21.图4是多层有机衬底的另一实施例的部分简化截面图;

22.图5是多层有机衬底的实施例的部分简化透视图;

23.图6是图5的多层有机衬底的部分简化顶视图;

24.图7是图1和图2的器件的封装的局部简化剖面顶视图;

25.图8是图1和图2的器件的封装的局部简化剖面侧视图;

26.图9是图1和图2的器件的局部简化放大剖面侧视图;

27.图10是图1和图2的器件的局部简化放大剖面顶视图;

28.图11是在图9的横截面中的多层有机衬底的实施例的部分简化横截面图;

29.图12是在图9的另一横截面平面中的多层有机衬底的实施例的部分简化横截面图;

30.图13是在图9的另一横截面平面中的多层有机衬底的实施例的部分简化横截面图;

31.图14是用于模拟的器件的局部简化剖面顶视图;

32.图15是图14的光电器件的局部简化剖面顶视图;

33.图16是图14的器件的多层有机衬底的透视图;

34.图17是示出图16的多层有机衬底在图14和15的器件的封装中的布置的透视图;以及

35.图18示出了图14的器件的插入损耗根据频率的变化的曲线。

具体实施方式

36.在各个附图中,相同的特征由相同的附图标记表示。特别地,在各个实施例中共同的结构和/或功能特征可以具有相同的附图标记并且可以设置相同的结构,尺寸和材料特性。为了清楚起见,仅示出和详细描述了对理解本文所述的实施例有用的步骤和元件。特别地,集成电路芯片和多层有机衬底制造步骤没有详细描述,所描述的实施例与通常的步骤

兼容。

37.除非另有说明,当提及连接在一起的两个元件时,这表示除了导体之外没有任何中间元件的直接连接,并且当提及耦合在一起的两个元件时,这表示这两个元件可以被连接或者它们可以经由一个或多个其它元件被耦合。此外,这里认为术语“绝缘”和“导电”分别表示“电绝缘”和“导电”。

38.在以下描述中,当提及限定绝对位置的术语时,例如术语“前”,“后”,“顶”,“底”。除非另有说明,否则“左”,“右”等或相对位置(例如术语“上”,“下”,“上”,“下”等)或限定方向的术语(例如术语“水平”,“垂直”等)是指附图或在正常使用位置的显示屏的取向。

39.除非另有说明,表述“约”,“大约”,“基本上”和“以

…

量级”表示在10%以内,优选在5%以内。除非另外指明,否则诸如“第一”,“第二”等的序数数字仅用于将元件彼此区分开。特别地,这些形容词不将所描述的实施例限制为这些元素的特定顺序。

40.本技术旨在电磁波的发射,接收和/或传输的应用,特别是在从30ghz到300ghz(超高频带或ehf频带),优选地从140ghz到220ghz(g频带)延伸的频带中的电磁波,这种电磁波在下文中被称为ehf波。对于空间应用,感兴趣的频率范围可以更具体地从50ghz到260ghz。

41.图1、图2和图3分别是ehf波收发器器件100的实施例的部分简化的透明透视图、剖面顶视图和剖面侧视图。在图1中,以粗线示出了观察者从器件100的外部可见的线,以细线示出了观察者从器件100的外部不可见的线。

42.器件100包括:

43.封装200,其界定至少第一腔体202和第二腔体204,所述第一腔体202通过通道206与所述第二腔体204连通,所述第二腔体204在一端207处朝向封装200的外部出现(emerging);

44.多层有机衬底300,具有结合到其上的集成电路芯片302,多层有机衬底300和集成电路芯片302容纳在第一腔体202中,图2的横截面基本上位于多层有机衬底300的上表面的水平处;

45.ehf波导400至少部分由封装200的第二腔体204形成,并与封装200的外部相通;以及

46.电连接器500至少部分地容纳在封装200中。

47.封装200包括表面208,具有第二腔体204的端部207出现在其上。在图1和图2所示的实施例中,表面208基本上与多层有机衬底300的主表面正交。根据一个实施例,封装200在表面208上包括形成波导连接器的部分209,在图1和图2中示意性地示出。第二腔体204的端部207在连接器209的水平处出现在表面208上。表面208可以是平面的或显示出凸块210,第二腔体204的端部207显露在其上。在操作中,图中未示出的另一波导旨在在连接器209的水平处连接到封装200。为此,连接器209可以包括用于波导的螺钉和对准销的开口211。

48.封装200包括至少一个壳体212,用于容纳连接到多层有机衬底300的电连接器500。壳体212在封装200的至少一个表面214上开口。壳体212具有与封装200的表面214连通的第一腔体202。在图1和图2所示的实施例中,壳体212对于每个电连接器500是分开的。每个壳体212在一端出现在表面214上,并且在相对端出现在第一腔体202中。例如,在图1和图2所示的实施例中,六个电连接器500经由六个壳体212与多层有机衬底300接触。六个壳体212两个-两个地出现在封装200的三个不同的侧面214上。两个表面214与表面208正交,并

且一个表面214与表面208相对。作为一个变体,壳体212可以包括用于多个电连接器500的共用部分,对于每个电连接器500,该共用部分通过将该共用部分耦合到该第一腔体上的一个末端部分延续。

49.封装200可以包括结合到上部222的下部220。然后,多层有机衬底300可以位于下部220和上部222之间。在图1、图2和图3所示的实施例中,下部220的边缘224直接抵靠上部222的边缘226。然后,当下部220的边缘224直接抵靠上部222的边缘226时,第一腔体202可以对应于在下部220和上部222之间界定的空隙。除了将第一腔体202耦合到第二腔体204的通道206之外,下部220的边缘224可以沿着第一腔体202的整个周边与上部222的边缘226机械接触。作为变体,多层有机衬底300可以夹在下部220和上部222之间,下部220直接抵靠多层有机衬底300,上部222直接抵靠多层有机衬底300。然后,当下部220直接抵靠多层有机衬底300并且上部222直接抵靠多层有机衬底300时,第一腔体202可对应于存在于下部220与上部222之间的空隙。

50.根据一个实施例,第二腔体204包括由倾斜部分242延续的第一直线部分240,该倾斜部分242本身可能由第二直线部分244延续。通道206出现在第二腔体204的第一直线部分240中。在图1和图2所示的封装200的实施例中,第二直线部分244出现在存在于表面208上的凸起210上。

51.封装200至少部分地由导电材料制成,例如黄铜或铝。根据一个实施例,封装200完全由导电材料制成。封装200可以通过机械加工形成。作为变体,封装200可以通过3d打印形成,也称为增材打印。集成电路芯片302可以基于硅、砷化镓、磷化铟、硅-锗或氮化镓。

52.图3还示出了多层有机衬底300和集成电路芯片302的实施例的结构。图4是多层有机衬底300的另一实施例的部分简化截面图。图5和图6分别是多层有机衬底300的实施例的部分简化透视图和顶视图。

53.多层有机衬底300包括上表面304和下表面306。集成电路芯片302包括前表面308和后表面310。集成电路芯片302通过倒装芯片结合被结合到多层有机衬底300的上表面304。集成电路芯片302的前表面308位于多层有机电路300的上表面304的前面,并通过连接元件312(例如焊球或铝焊盘)结合到多层有机衬底300。集成电路芯片302和多层有机衬底300之间的结合被称为倒装芯片,因为与引线结合相反,多层有机衬底300的上表面304和接收连接焊料(或触点)的集成电路芯片302的前表面308必须在相同的方向上,即它们不相反,对于“倒装芯片”技术,多层有机衬底300的上表面304和集成电路芯片302的前表面308必须彼此面对(即,在相反的方向上)。因此,集成电路芯片302相对于通过引线结合将其结合到多层有机衬底300的配置有效地翻转。

54.对于图3和4所示的这些实施例中的每个实施例,多层有机衬底300包括:具有两个相对表面322a、322b的绝缘支撑件320,并且对于每个表面322a、322b,导电轨324a、324b或表面322a、322b上的导电层,覆盖导电轨324a、324b和导电轨324a、324b之间的支撑件320的涂层326a、326b,以及通过绝缘支撑件320将轨324a耦合到导电轨324b的导电通孔328。集成电路芯片302位于支撑件320的表面322a的侧面上。每个涂层326a、326b可以具有单层或多层结构。作为示例,每个涂层326a、326b包括两层330a、330b和332a、332b的堆叠,最靠近绝缘支撑件320的层330a、330b是绝缘层。多层有机衬底300还可以包括仅在图3中示出的导电通孔334a、334b,其完全穿过涂层326a、326b并连接到导电轨324a,324b的端部。在图1和图2

所示的封装200的实施例中,电连接器500可以与导电通孔334a之一接触,如图3所示。

55.在图4所示的实施例中,作为示例,多层有机衬底300在支撑件320的每个表面322a、322b上包括三个金属化层。更准确地说,图4所示的多层有机衬底300包括图3所示的多层有机衬底300的所有元件,并且在每个表面322a、322b的侧面上,在导电轨324a、324b和表面322a、322b之间还包括覆盖表面322a、322b的两个绝缘层336a、336b和338a、338b的堆叠,绝缘层336a,336b和表面222a,222b之间的导电轨340a、340b,在绝缘层336a,336b和绝缘层338a,338b之间的导电轨342a,342b,以及将导电轨324a,324b连接到导电轨340a、340b,导电轨340a、340b连接到导电轨342a、342b和/或导电轨324a、324b连接到导电轨342a,342b的导电通孔344a、344b

56.支撑件320是有机材料层,例如聚合物,特别是用纤维增强的环氧树脂,特别是玻璃纤维增强的双马来酰亚胺-三叠氮化物(bismaleimide-triazide)树脂。支撑件320的厚度可以从60μm至100μm变化,并且例如等于约80μm。每个绝缘层330a,330b,336a,336b,338a,338b可以是保护导电轨免受氧化的聚合物层。每个绝缘层336a,336b,338a,338b的最大厚度可以从20μm变化到60μm,并且例如等于大约48μm。每个绝缘层330a,330b的厚度可以从5μm到25μm变化,并且例如等于大约15μm。每个导电轨324a,324b,340a,340b,342a,342b可以由铜制成。每个导电轨324a,324b,340a,340b的厚度可以从10μm到25μm变化,并且例如等于大约18μm。每个导电轨342a,342b的厚度可以从5μm到15μm变化,并且例如等于大约8μm。每个导电通孔344a,344b可以由铜制成。涂层326a,326b的层332a,332b优选由例如石墨烯的导电材料制成。层332a,332b的厚度可以从0.05mm变化到0.3mm,并且例如等于大约0.12mm。

57.有利地,相对于具有结合到其上的集成电路芯片的载体由石英制成的情况,多层有机衬底300的制造成本降低。

58.涂层326a和可能的绝缘层336a和338a包括通孔346a,特别是在集成电路芯片302的位置,暴露导电轨324a,342a或340a。涂层326a和可能的绝缘层336a,338a可以包括至少另一个暴露导电轨324a,342a或340a的通孔348a,例如,以允许电连接器500连接到导电轨324a,342a或340a。在图5和图6中,多层有机衬底300被示为具有在涂层326a中的两个贯通开口348a和在涂层326a中的一个开口346a。

59.根据一个实施方式,多层有机衬底300包括主体部分350和至少一个突起352,主体部分350在俯视图中占据多层有机衬底300的总表面积的至少90%,突起352从主体部分350的边缘突出。在顶视图中,主要部分350可以具有正方形或矩形形状。在顶视图中,突起352可以具有矩形形状。当多层有机衬底300被放置在封装200中时,突起352包括在通道206中延伸的中间部分354和在第二腔体204中延伸的末端部分356。多层有机衬底300包括ehf波收发器天线358,其例如由端部356中的导电轨324a,340a或342a形成。天线358通过例如直线的导电轨360耦合到集成电路芯片302。根据一个实施例,涂层326a不存在于天线358和导电轨360上。

60.图7和图8分别是封装200的一部分的实施例的部分简化的剖视俯视图和剖视侧视图。图9和图10分别是图7和图8的放大图,在这些图中进一步示出了多层有机衬底300。图7至图10进一步示出了第一腔体202的更详细的实施例。

61.根据一个实施例,第一腔体202包括第一凹陷230,如图3所示,其中容纳有集成电

路芯片302。根据一个实施例,第一腔体202包括将第一凹陷230耦合到通道206的第二凹陷232。可以不存在第二凹陷232。

62.通道206,第一腔体202和第二腔体204的尺寸特别取决于要由第二腔体204传输的ehf波的波长。根据实施例,第一腔体202在顶视图中的尺寸基本上对应于多层有机衬底300的主要部分350在顶视图中的尺寸。根据实施例,第一腔体202在俯视图中具有正方形或矩形的形状,其每一侧长度可从5mm变化到25mm,例如,等于大约15mm。根据一个实施例,第一凹陷230在顶视图中的尺寸基本上对应于集成电路芯片302在顶视图中的尺寸。根据一个实施例,第一凹陷230在俯视图中具有正方形或矩形的形状,其每个边长可以从2mm到8mm变化。第一腔体202和第二腔体204之间的通道206的长度可以从0.2mm变化到0.6mm,并且例如对于从140ghz到220hz的频率范围等于大约0.4mm。通道206的高度可以从0.2mm变化到0.6mm,并且例如对于从140ghz到220hz的频率范围等于大约0.4mm。

63.根据一个实施例,第二腔体204的横截面积沿着第一直线部分240,倾斜部分242和第二直线部分244都是恒定的。第二腔体204可具有正方形或矩形横截面,其每一侧长度可从0.5mm变化到1.5mm,且例如对应于具有等于约0.8mm的小侧长度和等于约1.3mm的大侧长度的矩形横截面。在图9和图10中,示出了覆盖第一腔体202和通道206的壁的涂层246和覆盖第二腔体204的壁的涂层248。涂层246和/或涂层248可以由锡和金合金制成。涂层246可以沉积在第一腔体202和通道206的壁上,和/或涂层248可以沉积在第二腔体204的壁上,以限制氧化,改善表面状态和导电性。

64.根据实施例,在第一和第二凹陷230、232的外部,第一腔体202具有基本恒定的高度,该高度可以从0.5mm变化到1mm,并且例如对于从140ghz到220hz的频率范围等于大约0.6mm。第一凹陷230的深度可以从1mm变化到2mm,并且例如等于大约1.5mm。第一腔体202在第二凹陷232的水平处的总高度可以从0mm变化到0.3mm。根据倒装芯片结合将集成电路芯片302结合到多层有机衬底300的事实有利地使得能够相对于通过引线结合将集成电路芯片302结合到多层有机衬底300所需的深度减小第一凹陷230的深度。有利地提供空气膜,覆盖通道206中的突起352。覆盖通道206中的突起352的气膜的厚度可以从200μm至400μm变化,并且例如等于300μm。在第一腔体202中,空气膜可以存在于涂层226a和封装200的上部之间。

65.图11是在第一凹陷230外部的主要部分350中具有图4所示多层结构的多层有机衬底300的实施例的部分简化截面图。

66.图12是多层有机衬底300的实施例的部分简化截面图,该多层有机衬底300具有图4所示的多层结构,位于第一腔体202中第二凹陷232的水平处。不存在涂层326a。

67.图13是在通道206和第二腔体204中的凸起252中的多层有机衬底300的实施例的部分简化截面图,该凸起252具有图4所示的多层结构。不存在涂层326a、支撑件320、绝缘层336b、338b和涂层326b。

68.图14和图15分别是用于执行模拟的ehf波传输器件120的实施例的部分简化的剖视俯视图和剖视侧视图。图16是用于执行模拟的多层有机衬底300的实施例的透视图。图17是示出组装在图14和15的器件120的封装200中的图16的多层有机衬底300的透视图。

69.模拟旨在确定多层有机衬底300和波导400之间的ehf波传输特性。对于仿真,不存在集成电路芯片302。封装200具有对称结构并且包括形成两个ehf波导400的第一腔体202

和两个第二腔体204。

70.多层有机衬底300具有对称形状并且包括两个突起352,每个突起352包括ehf波收发器天线358,这两个天线358经由导电轨360彼此连接。如图17所示,每个天线358位于第二腔体204之一中,并且第二凹陷覆盖导电轨360。对于模拟,在一个波导400的末端提供电磁波,并且检测在另一个波导400的末端发射的电磁波。

71.图18示出了在波导400和图14的器件120的多层有机衬底300之间的链路的水平处,插入损耗il(以db为单位)根据频率freq的变化曲线。插入损耗与航天工业中的应用兼容。

72.已经描述了各种实施例和变型。本领域技术人员将理解,这些各种实施例和变型的某些特征可以组合,并且本领域技术人员将想到其它变型。最后,基于以上给出的功能指示,所描述的实施例和变体的实际实现在本领域技术人员的能力范围内。

73.电磁波发射/接收器件(100)可以概括为包括多层有机衬底(300),集成电路芯片(302),倒装组装在多层有机衬底上的芯片,包括第一腔体(202)的封装(200),第一腔体(202)包含多层有机衬底和集成电路芯片,并且通过通道(206)与形成电磁波的波导(400)的第二腔体(204)连通。

74.第一腔体(202)可以包括与集成电路芯片(302)相对的第一凹陷(230)。

75.第一腔体(202)可以包括将通道(206)耦合到第一凹陷(230)的第二凹陷(232)。

76.多层有机衬底(300)可以包括第一腔体(202)中的主要部分(350)和从主要部分延伸到通道(206)中并穿透进入第二腔体(204)中的突起(352)。

77.多层有机衬底(300)可以包括在第二腔体(204)中的突起(252)上的电磁波发射/接收天线(258)。

78.有机多层衬底(300)可以包括由有机材料制成的电绝缘支撑件(320)。

79.支撑件(320)可以包括第一和第二相对表面(322a,322b),在第一表面上延伸的导电轨(324a,340a,342a),以及覆盖导电轨的电绝缘层(326a,336a,338a)。

80.多层有机衬底(300)的突起(252)可以不包括第二腔体(204)中的支撑件(320)。

81.多层有机衬底(300)的突起(252)可以不包括通道(206)中的支撑件(320)。

82.多层有机衬底(300)可以进一步包括涂层(326a),该涂层包括覆盖电绝缘层(338a)的石墨烯层(332a)。

83.多层有机衬底(300)可以包括将天线(358)耦合到集成电路芯片(302)的导电线(360),其中涂层(326a)不覆盖第一腔体(202)中的导电线。

84.电磁波可以在从30ghz到260ghz的频带中。

85.实施例的目的是提供一种克服了现有器件的全部或部分缺点的超高频波发射/接收器件。

86.根据实施例的目的,降低了在器件的天线和波导之间传输超高频电磁波期间的损耗。

87.根据实施例的目的,降低了器件的制造成本。

88.实施例提供了一种电磁波发射/接收器件,其包括多层有机衬底,集成电路芯片,倒装组装在多层有机衬底上的芯片,包括第一腔体的封装,该第一腔体包含多层有机衬底和集成电路芯片,并且第一腔体通过通道与形成电磁波波导的第二腔体连通。

89.根据一个实施例,第一腔体包括与集成电路芯片相对的第一凹陷。

90.根据一个实施例,该第一腔体包括将该通道耦合到该第一凹陷上的第二凹陷。

91.根据实施例,多层有机衬底包括第一腔体中的主要部分和从主要部分延伸到通道中并且穿透进入第二腔体中的突起。

92.根据实施例,多层有机衬底包括用于在第二腔体中的突起上发射/接收电磁波的天线。

93.根据一个实施,多层有机衬底包括由有机材料制成的电绝缘支撑件。

94.根据一个实施例,支撑件包括第一相对表面和第二相对表面,在第一表面上延伸的导电轨,以及覆盖导电轨的电绝缘层。

95.根据一个实施方式,多层有机衬底的突起不包括第二腔体中的支撑件。

96.根据一个实施方式,多层有机衬底的突起不包括通道中的支撑件。

97.根据一个实施方式,多层有机衬底还包括包含覆盖电绝缘层的石墨烯层的涂层。

98.根据实施例,多层有机衬底包括将天线耦合到集成电路芯片的导电线,其中涂层不覆盖第一腔体中的导电线。

99.根据实施例,电磁波在从30ghz到260ghz的频带中。

100.本公开的一方面提供了一种方法,包括:形成在具有与第二表面相对的第一表面的封装中的第一腔体;形成在所述第一腔体中的相对于所述第二表面更靠近所述第一表面的第一多个导电层;形成在所述第一腔体中的第一绝缘层,所述第一绝缘层被所述第一多个导电层与所述第一表面间隔开;形成在所述第一腔体中的相对于所述第一表面更靠近所述第二表面的第二多个导电层;形成在所述封装中的第二腔体,所述第二腔体相对于所述第一表面更靠近所述第二表面;将集成电路芯片耦合在所述第一绝缘层上;将波导耦合到所述集成电路并且至少部分地在所述第二腔体中;以及形成从所述封装的一侧延伸的多个电连接器,所述波导从所述封装的与所述一侧不同的一侧延伸。

101.根据一个或多个实施例,方法包括从所述第一多个导电层、所述第一绝缘层以及所述第二多个导电层形成衬底。

102.根据一个或多个实施例,其中所述多个电连接器从所述封装延伸到外部环境中。

103.根据一个或多个实施例,其中所述第二腔体从所述衬底延伸到所述封装的边缘。

104.上述各种实施例可以组合以提供另外的实施例。如果需要,可以修改实施例的各方面以采用各种专利,申请和出版物的概念来提供另外的实施例。

105.根据上述详细描述,可以对实施例进行这些和其它改变。通常,在下面的权利要求中,所使用的术语不应该被解释为将权利要求限制到在说明书和权利要求中公开的特定实施例,而是应该被解释为包括所有可能的实施例以及这些权利要求被授权的等同物的全部范围。因此,权利要求不受本公开的限制。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。