技术特征:

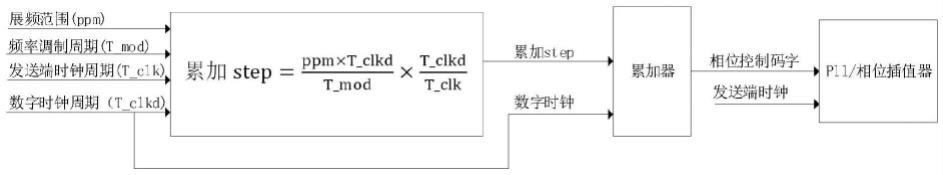

1.一种时钟展频电路,其特征在于,包括依次连接的数据计算单元、一阶积分器、累加器、译码器和插值器,其中:数据计算单元,用于产生每个展频调制周期需要的第一累加数据;一阶积分器,用于对所述数据计算单元产生的第一累加数据进行整形,得到第一整形数据,并将所述第一整形数据输出给累加器;累加器,用于在所述累加器和译码器工作的模拟时钟周期内对所述第一整形数据进行累加,得到第二累加数据,并将所述第二累加数据输出给译码器进行译码;译码器,用于在所述累加器和所述译码器工作的模拟时钟周期内对所述第二累加数据进行译码,得到译码结果,并将所述译码结果传输给插值器;插值器,用于根据所述译码器传来的所述译码结果对发送端时钟的相位进行插值。2.根据权利要求1所述的时钟展频电路,其特征在于,所述第一累加数据由以下公式得出:其中,n为所述第一累加数据,ppm为展频范围、t_clkd为一阶积分器工作的数字时钟频率、t_clka为累加器和译码器工作的模拟时钟频率、t_mod为展频调制频率、t_clk为发送端时钟频率。3.根据权利要求2所述的时钟展频电路,其特征在于,所述发送端时钟频率大于1ghz,所述累加器和译码器工作的模拟时钟频率与所述一阶积分器工作的数字时钟频率均为所述发送端时钟频率的n分频,n为整数。4.根据权利要求3所述的时钟展频电路,其特征在于,所述累加器和译码器工作的模拟时钟频率大于所述一阶积分器工作的数字时钟频率,所述累加器和译码器工作的模拟时钟频率为所述一阶积分器工作的数字时钟频率的整数倍。5.根据权利要求1所述的时钟展频电路,其特征在于,所述一阶积分器在所述一阶积分器工作的数字时钟周期内对所述第一累加数据进行积分整形。6.根据权利要求1所述的时钟展频电路,其特征在于,所述第一累加数据分为整数部分和小数部分,所述一阶积分器对所述第一累加数据的小数部分进行累加,得到所述第一整形数据。7.根据权利要求1所述的时钟展频电路,其特征在于,所述插值器在发送端时钟周期内根据所述译码器传来的所述译码结果对发送端时钟的相位进行插值。8.一种时钟展频方法,其特征在于,包括权利要求1-7任一所述的时钟展频电路,所述时钟展频方法包括:设置展频范围和展频调制频率;根据数据计算公式得到所述第一累加数据;根据所述累加器工作的数字时钟周期将所述第一累加数据的小数部分进行累加,得到第一整形数据;根据所述累加器和译码器工作的模拟时钟周期对所述第一整形数据进行累加,得到第二累加数据;根据所述累加器和所述译码器工作的模拟时钟周期对所述第二累加数据进行译码,得

到译码结果;根据所述译码器传来的所述译码结果对发送端时钟的相位进行插值。9.根据权利要求8所述的展频方法,其特征在于,所述数据计算公式为:其中,n为所述第一累加数据,ppm为展频范围、t_clkd为一阶积分器工作的数字时钟频率、t_clka为累加器和译码器工作的模拟时钟频率、t_mod为展频调制频率、t_clk为发送端时钟频率。10.根据权利要求9所述的展频方法,其特征在于,所述发送端时钟频率大于1ghz,所述累加器和译码器工作的模拟时钟频率与所述一阶积分器工作的数字时钟频率均为所述发送端时钟频率的n分频,n为整数,所述累加器和译码器工作的模拟时钟频率大于所述一阶积分器工作的数字时钟频率,所述累加器和译码器工作的模拟时钟频率为所述一阶积分器工作的数字时钟频率的整数倍。

技术总结

一种时钟展频电路及时钟展频方法,时钟展频电路包括依次连接的数据计算单元、一阶积分器、累加器、译码器和插值器,其中:数据计算单元用于产生第一累加数据;一阶积分器用于对第一累加数据进行整形,得到第一整形数据;累加器用于对第一整形数据进行累加,得到第二累加数据;译码器用于对第二累加数据进行译码,得到译码结果;插值器用于根据译码结果对发送端时钟的相位进行插值。本发明提供的时钟展频电路,通过将累加器和译码器的时钟与数据计算单元的时钟区分开,减少累加器所需位数,加快累加器和译码器的时钟频率,有效解决了现有高速数据发送过程中展频电路存在的内部时序难以收敛的问题。收敛的问题。收敛的问题。

技术研发人员:陈新剑 姚伟荣

受保护的技术使用者:深圳市紫光同创电子有限公司

技术研发日:2022.09.05

技术公布日:2022/12/19

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。