芯片损伤位置定位方法

1.技术领域

2.本发明涉及半导体器件制造失效分析领域,特别是指一种芯片损伤位置定位方法。

背景技术:

3.在芯片的制造工艺中,芯片的制造良率不可能达到100%。比如存储器芯片,存储器经过测试,总会有一些存储单元会出现失效的问题,对这些失效的问题需要进行分析,找出原因以及时改进工艺,提高良率。

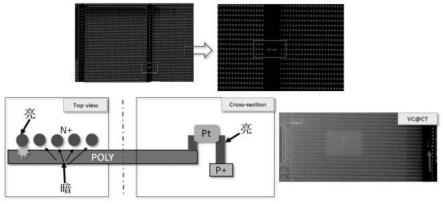

4.对于memory产品,bitmap tool是电学定位中最重要的工具之一 。bitmap工具是一种工程分析用数据显示工具,可将nvm内所有存储单元数据以格点形式直观显示,我们可以使用颜色对电学故障进行分类来定义数据“0”和“1”,如图1。图中有数据“0”错误的存储单元我们采用红色标识将其表示出来,数据“1”错误采用绿色标识,数据“0”和“1”均有错误采用黄色标识。这样形成一个存储单元阵列的bitmap,可以很直观地显示出那些存储单元由问题以及存在什么问题。

5.针对完整的“行”或“列”的后道金属层次失效,我们可以按照失效地址从样品的俯视视角从一端到另一端在显微镜或电镜下依次进行目视检查,直至找到失效位置,如图2。经过检查图2中是典型的整列失效,对应的是m1金属短路结果。

6.但对于某些产品前道结构的失效,当无法做到精确定位到某个比特时,我们无法透过层间膜看到完整的失效形貌。比如某产品bulk(全片)操作后,读取结果为行失效,无法通过vt margin测试筛选出写入深度最差的bit,即io整体较差,失效位置无法收敛,呈现一条平行于x轴的直线。

7.使用电压衬度像(vc:voltage contrast)的方式可以帮助解决上述问题。当电子束(离子束)扫描样品表面时,会与表面产生非弹性碰撞,并放射出一些低能(<50 ev)的二次电子。这些电子一般仅能离开表面30nm以内,利用侦测器前端外加几百伏特的电压将这些二次电子吸收并成像,就是电压衬度像。样品表面的电位会影响二次电子的产率,电位越高放射二次电子量越少,电位越低放射量越多,利用此电压衬度像可以判断连接线(包括金属、多晶、接触孔等)的短路与断路。

8.实际应用中,一般采用低压电子束或者高压离子束进行电压衬度实验,n 的source和 drain 均是暗的,此时若衬底aa有损伤(当存储器aa注入为n型时),通过电压衬度均为暗场,无法确认异常所在位置。如图3所示,是低压电子束和高压离子束的电压衬度像,在两种模式下,正常状态和异常状态下n 区的电压衬度像均显示为暗,这导致无法确认异常。

9.如图4所示的电压衬度对比,看到了字线多晶硅的vc异常,但无法定位到具体哪一个bit失效。传统方法是采用二分法,将整块io区域进行离子束镀pt保护,由整根多晶硅

poly的两端向中心fib(聚焦离子束)推断面,需要边推边确认,需要耗费大量人力资源,需使用机台时间数个小时甚至更长的时间。

10.

技术实现要素:

11.本发明所要解决的技术问题在于提供一种芯片损伤位置定位方法,找出失效的位置以分析其失效原因。

12.为解决上述问题,本发明所述的芯片损伤位置定位方法,包含:一种芯片损伤位置定位方法,其特征在于:针对失效的芯片样品,进行预检查,初步确定芯片样品的失效范围;对初步确定的失效范围内的重掺杂p型区与多晶硅之间进行短接,然后进行电压衬度。

13.进一步地,所述的预检查,包括进行光学目视检查,或者是使用剥离手段去除表层金属后进行的后道结构的显微或者电压衬度检查。

14.进一步地,所述的剥离手段包括研磨或者是聚焦离子束。

15.进一步地,所述的重掺杂区与多晶硅之间采用金属进行连接。

16.进一步地,采用聚焦离子束将重掺杂区与多晶硅之间采用金属铂进行连接。

17.本发明中将多晶硅与p 区进行电性连接,通过p 区的电压衬度结果来同步反应n 区的电压衬度,解决n 区电压衬度无法反馈缺陷结果的问题,能迅速定位失效的位置,找到失效的原因,及时调整工艺,提高良率。

18.附图说明

19.图1 是芯片的bitmap图,使用颜色对电学故障进行分类来定义数据“0”和“1”。

20.图2 是现有技术中在显微镜下依次进行目视检查直至找到失效位置的示意图。

21.图3 是低压和高压模式下的电压衬度对比。在电压衬度实验中,n 的source和 drain 均是暗的,此时若衬底aa有损伤(当存储器aa注入为n型时),电压衬度像均为暗场,无法确认异常所在位置。

22.图4 是电压衬度中,看到了字线多晶硅的vc异常,但无法定位到具体位置的实际操作图。

23.图5 是本发明将多晶硅与p 区进行电性连接之后的原理及实施例示意图。

24.图6 是本发明实施例最终找到有源区损伤位置后,对损伤位置x方向断面分析的显微照片。

25.图7 是本发明实施例最终找到有源区损伤位置后,对损伤位置y方向断面分析的显微照片。

26.具体实施方式

27.以下结合附图给出本发明的具体实施方式,对本发明中的技术方案进行清楚、完

整的描述,但本发明不限于以下的实施方式。显然,所描述的实施例是本发明的一部分实施例,而不是全部的实施例。根据下面说明和权利要求书,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比率,仅用于方便、明晰地辅助说明本发明实施例的目的。本发明能够以不同形式实施,而不应当解释为局限于这里提出的实施例。相反地,提供这些实施例将使公开彻底和完全,并且将本发明的范围完全地传递给本领域技术人员。在附图中,为了清楚,层和区的尺寸以及相对尺寸可能被夸大,自始至终相同附图标记表示相同的元件。应当明白,当元件或层被称为“在

…

上”、“与

…

相邻”、“连接到”或“耦合到”其它元件或层时,其可以直接地在其它元件或层上、与之相邻、连接或耦合到其它元件或层,或者可以存在居间的元件或层。相反,当元件被称为“直接在

…

上”、“与

…

直接相邻”、“直接连接到”或“直接耦合到”其它元件或层时,则不存在居间的元件或层。应当明白,尽管可使用术语第一、第二、第三等描述各种元件、部件、区、层和/或部分,这些元件、部件、区、层和/或部分不应当被这些术语限制。这些术语仅仅用来区分一个元件、部件、区、层或部分与另一个元件、部件、区、层或部分。因此,在不脱离本发明教导之下,下面讨论的第一元件、部件、区、层或部分可表示为第二元件、部件、区、层或部分。

28.本发明所述的存储器损伤位置定位方法,主要是为了快速找到芯片失效的位置,判断缺陷的类型以尽快解决工艺上的问题。

29.对于一失效的存储器芯片,如图5所示,首先使用传统的分析方法大致确定了失效位置。包括一些初步的电压衬度检查或者光学目视检查等手段,先确定缺陷的大致区域。

30.经背景技术部分的介绍可知,由于n 的区的电压衬度无论在何种状态下均显示为暗导致无法确定其是否失效,因此将n 区失效的部分与p 连接起来,让n 区的电压衬度与p 区的电压衬度同步起来,则可以借助p 的电压衬度来分析其是否失效,并能尽快找出缺陷位置。

31.图5中展示了本发明中将多晶硅与p 区进行连接的原理示意图以及实际案例图。原理图包括剖面图及俯视图。将p 区与多晶硅连接,则p 区的电压衬度效果通过多晶硅被传递到n 区,因此,当对n 区进行电压衬度的时候,此时多晶硅与n 区之间的状态被同步到p 区,可以通过p 区的电压衬度表现来反映出n 区的电压衬度表现。

32.当n 区与多晶硅之间有短路时,由于该多晶硅同时与p 区有连接,n 区的电压衬度会通过短路点连接到多晶硅,再通过多晶硅与p 的连接反映到p 区的电压衬度上,因此可以改变n 区无论是否正常电压衬度都为暗的情况,当n 区有短路点时其电压衬度为亮的状态,迅速找出p 区显示为亮的有缺陷的附近的n 区,找出缺陷。

33.对于将多晶硅与p 区进行连接的连接方式,本实施例中采用金属连接,将p 区与多晶硅连接起来,比如在半导体工艺中用得比较多的金属铂。可以采用聚焦离子束fib工艺在目标区域刻蚀形成沟槽,然后在沟槽内填充金属铂来完成多晶硅与p 区之间的连线。

34.也可以采用其他的金属来进行连接,比如铝等。或者是采用其他的方式来进行连接,包括采用飞线。总之,采用便利的手段及材料将p 区与多晶硅进行有效的电性连接即可。

35.由于多晶硅一般位于晶圆表面,而有源区p 在晶圆内部,可能还涉及到形成接触孔的工艺,也可以借助周围具有将p 引出的接触孔来进行金属连接。

36.本发明实施例中,如图5所示,通过此方法,可以快速找到n 有源区损伤的失效位

置。将多晶硅与p 区连接之后进行电压衬度,n 区显示为亮,迅速找到失效点,进行断面检查。如图6及图7所示,图6是找到有源区损伤位置后,对损伤位置进行fib切割形成的x方向断面分析的显微照片,而图7 是损伤位置进行fib切割形成的y方向断面分析的显微照片。通过对显微照片的分析,发现是sti沉积之后的湿法刻蚀导致的,如图中的圈注处所示,存在一些残余导致短路的问题。并且,本实验方法经过多次重复验证也证明确实可靠。

37.以上仅为本发明的优选实施例,并不用于限定本发明。对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。