1.本发明涉及一种新型噪声整形模数转换器电路,属于模数转换器领域。

背景技术:

2.在现实世界中,存在着各类不同的模拟信号;例如光、电、磁等。在对该类信号进行处理分析以及应用的时候,需要模数转换器(adc)将模拟信号转换成数字信号。adc作为重要接口电路,制约着整个信号处理过程中的性能。根据应用场景的不同,对adc的性能有不同的要求。数据采集仪器中的adc需满足中等速度或较低速度、中等精度;高速数据采集领域的adc需满足高速、中等精度;多媒体以及传感器等测量领域的模数传感器需满足低速、高精度等要求。

3.随着深亚微米cmos工艺的飞速发展,工艺的进步,使得晶体管能够在更高的频率工作。然而,更小的沟道长度以及更低的电源电压对于模拟电路的设计提出更大的挑战。在目前adc的设计中,研究人员不仅希望adc能够有更高的工作频率,同时希望高精度,功耗以及更简单的电路结构来达到更优的性能

4.在诸多adc架构中,虽然saradc架构具有低功耗的优势,然而因为比较器的噪声和电容阵列的失配使得其精度不高。因此,saradc的应用受到了很大的限制。sigma-deltaadc由于采用了噪声整形技术及过采样技术,使其自身具备高精度的优点。然而,随着工艺节点的推进,使得sigma-deltaadc中运放的设计变得越来越困难,同时具有较大的功耗。因此,以saradc为基础架构,融合sigma-deltaadc的噪声整形技术及过采样技术的新结构ns sar adc为高性能adc的研发带来了新的研发热点。

5.目前噪声整形saradc的工作基本原理是:其通过在adc的闭环反馈环路中施加一个具有高低频增益和低高频增益的方法器(通常为积分器),利用负反馈原理,将低频量化噪声整形到高频;结合过采样技术,可大幅降低adc的带内等效噪声,从而提高adc的精度。与sigma-deltaadc一样,saradc也是一种闭环adc,具有实施噪声整形的天然条件。

6.然而积分器的实现存在很多种方式,主要有三种:(1)基于ota的噪声整形saradc整形能力强,但电路设计难度大,静态功耗高,且工艺演进兼容性不好;(2)基于动态放大器的噪声整形saradc具有较强的整形能力和较低的静态功耗,但其随工艺、电源电压和温度(process,voltage and temperature,pvt)变化的稳定性不好;(3)无源噪声整形saradc结构简单、功耗低、pvt稳定性好,但因为存在电荷重分配导致的信号删减问题,所以噪声整形能力弱。本发明能够克服现有技术的不足,进一步改善和提高噪声整形adc电路的结构和性能。

技术实现要素:

7.本发明采用动态放大器和开关电容相结合的方式来实现噪声整形,具有静态功耗小,结构简单,pvt稳定性好,噪声整形能力强的优点。本发明将整体电路分为两部分,首先是第一部分是对saradc比较完后的残差电压进行采样和放大处理,将放大后的电压存储到

电容中;第二部分是将电容中已经放大过的残差电压进行电荷重分配与再次放大存储到具有延时功能的电容中,然后通过多个电容之间相连开关的同时导通,使得经过积分后的残差信号传输到下一级的电路中。

8.上述目的通过以下技术方案实现:

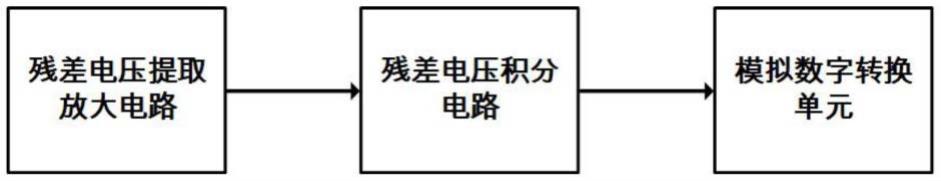

9.一种噪声整形电路结构,为介绍简洁采用单边等效电路来进行讲解转换操作,其组成包括:残差电压提取放大电路、残差电压积分电路、模拟数字转换单元三部分。残差电压提取放大电路通过残差电压积分电路与模拟数字转换单元连接,在整体结构中,残差电压提取放大电路连接cdac顶板,残差电压积分电路将残差电压进行积分处理,并输出到模拟数字转换电路完成整体电路转换工作。

10.所述的残差电压提取放大电路包含动态放大器g1和cmos开关s5。所述动态放大器g1的输入端与cmos开关s5相连,输出端与电容c1上极板相连;所述cmos开关s5一端与输入的模拟信号vres(n)相连,由фc控制,另一端与动态放大器g1的输入端相连。

11.所述的残差电压积分电路由开关s1、开关s2、开关s3、开关s4、开关s6、开关s7、动态比较器g2、电容c1、电容c2、电容c3、电容c4、电容c5。所述的开关s1一端与电容c4的上极板相连,另一端与共模信号相连,由фa控制。所述的开关s2一端与电容c3的上极板相连,另一端与电容c4的上极板相连,由фb控制。所述的开关s3一端与动态放大器的输出端相连,另一端与电容c3和电容c5的上极板相连,由фc控制。所述的开关s4,一端与电容c2的上极板相连,另一端与电容c5的上极板相连,由фd控制。所述的开关s6一端与动态放大器的输入端和电容c2的上极板相连,另一端与电容c1的上极板相连,由фd控制。所述的开关s7一端与电容c4的上极板相连,另一端与动态放大器g2的输入端相连,由фd控制。所述的动态放大器g2的输入端与电容c2的上极板相连,输出端与电容c5的上极板和电容c3的上极板相连。所述电容c1的上极板与动态放大器的g1的输出端相连,下极板与共模信号相连。所述电容c2的上极板与动态放大器g2的输入端相连,下极板与共模信号相连。所述电容c3的上极板与开关s3的一端相连,下极板与共模信号相连。所述电容c4的上极板与开关s1和开关s7的一端相连,下极板与共模电平相连。所述电容c5的上极板与开关s3的一端相连,下极板与共模信号相连。

12.所述的模拟数字转换单元包含比较器电路和数字逻辑电路。所述比较器电路是四端口输入比较器,其中第一个正向输入端与saradc的cdac上极板相连,其中第二个正向输入端与残差电压积分电路的输出相连,负向输入端与负端半边等效电路相连,比较器的输出端与数字逻辑电路的输入端相连,完成最终的转换。

13.本发明采用动态放大器和开关电容相结合的方式来实现噪声整形,通过采用动态放大器放大残差信号来抵抗电容与电容之间电荷重分配所带来的信号衰减问题,使得在低功耗的同时具有良好的噪声整形传递函数,并且传递函数的系数都与电容的比例相关,在结构简单的同时具有良好的pvt特性。

附图说明

14.图1是本发明的电路结构框图。

15.图2是本发明的电路原理结构框图。

具体实施方式

16.以下结合附图和实施例对本发明进行详细说明。

17.如图1-2所示,一种新型的噪声整形电路结构,所述的开关s1、开关s2、开关s3、开关s4、开关s5、开关s6、开关s7的相位之间应保持一定的关联。在第一相,所述复位开关s1闭合,开关s2、开关s3、开关s4、开关s5、开关s6、开关s7断开,使得电容c4的上极板电压复位到共模电压。在第二相,所述开关s2闭合,开关s1、开关s3、开关s4、开关s5、开关s6、开关s7断开,此时电容c3和电容c4进行电荷重分配。在第三相,开关s3、开关s5闭合,开关s1、开关s2、开关s4、开关s6、开关s7断开,动态放大器g1对电容c1的上极板进行充电,动态放大器g2对电容c3的上极板和c5的上极板进行充电。在第四相,开关s4、开关s6、开关s7闭合,开关s1、开关s2、开关s3、开关s5断开,此时电容c1、c2、c4和电容c5进行电荷重分配。

18.本发明的基本工作原理是,当开关s1、开关s2、开关s3、开关s4、开关s5、开关s6、开关s7处于第一相时,整体电路进行电容上电压的复位工作。电容c4上极板电压被开关复位到共模电平。当开关s1、开关s2、开关s3、开关s4、开关s5、开关s6、开关s7处于第二相时,开关s2闭合,电容c3和电容c4的上极板电荷进行电荷重分配,使得电容c3上极板存储的放大后的上一周期输出电压,被按比例分配到电容c4的上极板上,进行两个周期的信号电压延迟处理。当开关s1、开关s2、开关s3、开关s4、开关s5、开关s6、开关s7处于第三相时,开关s3、开关s5闭合,开关s1、开关s2、开关s4、开关s6、开关s7断开,此时动态放大器将saradc比较完后的cdac电容顶板的残差电压提取并且放大到电容c1的上极板上,动态放大器g2将上一周期存储在电容c2上的输出电压放大存储到电容c3的上极板和电容c5的上极板,电容c3的上极板电压进行一个周期的信号电压延迟存储,动态放大器使得提取的残差信号具有倍数,以抵抗后面与其他电容在进行电荷重分配时所带来的信号电压衰减问题。当开关s1、开关s2、开关s3、开关s4、开关s5、开关s6、开关s7处于第四相时,开关s4、开关s6、开关s7闭合,开关s1、开关s2、开关s3、开关s5断开,电容c4的上极板上此时存储着延迟两个周期的残差电压,电容c5的上极板上此时存储着延迟一个周期的残差电压,然后电容c1的上极板、电容c2的上极板、电容c4的上极板和电容c5的上极板相连,实现四个电容之间的电荷重分配,然后残差电压积分电路输出电压到模拟数字转换电路中的比较器输入端。由此实现对残差电压的噪声整形功能。

19.当然,上述说明并非是对本发明的限制,本发明也并不仅限于上述举例,本技术领域的技术人员在本发明的实质范围内所做出的变化、改型、添加或替换,也应属于本发明的保护范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。