技术特征:

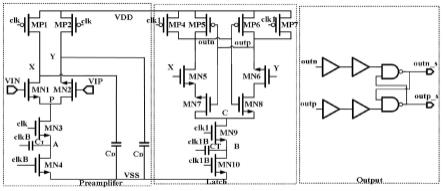

1.一种高速低功耗的前置锁存比较器,其特征在于,所述前置锁存比较器包括前置放大器、锁存器和输出缓冲器:所述前置放大器,用于对驱动负载的驱动信号进行放大;所述锁存器,用于加速信号比较的输出响应;所述输出缓冲器,用于将所述锁存器的输出信号转换成逻辑信号。2.根据权利要求1所述前置锁存比较器,其特征在于,所述前置放大器包括第一晶体管组、第二晶体管组和第三晶体管组;所述第一晶体管组和第二晶体管组的一个信号端均与电源信号端vdd电连接;所述第一晶体管组和第二晶体管组的另一个信号端均与所述第三晶体管组电连接。3.根据权利要求2所述前置锁存比较器,其特征在于,所述第一晶体管组包括pmos晶体管mp1和nmos晶体管mn1;所述pmos晶体管mp1的源极信号端与电源信号端vdd电连接;所述pmos晶体管mp1的栅极信号端与时钟信号clk的信号端电连接;所述pmos晶体管mp1的漏极信号端与所述nmos晶体管mn1的漏极信号端电连接;其中,所述pmos晶体管mp1的漏极信号端与所述nmos晶体管mn1的漏极信号端电连接的线路上设置有一个电容c

d

,所述电容c

d

的一端与所述线路连接,所述电容c

d

的另一端与公共接地端vss相连。4.根据权利要求2所述前置锁存比较器,其特征在于,所述第二晶体管组包括pmos晶体管mp2和nmos晶体管mn2;所述pmos晶体管mp2的源极信号端与电源信号端vdd电连接;所述pmos晶体管mp2的栅极信号端与时钟信号clk的信号端电连接;所述pmos晶体管mp2的漏极信号端与所述nmos晶体管mn2的源极信号端电连接;其中,所述pmos晶体管mp2的漏极信号端与所述nmos晶体管mn2的源极信号端电连接的线路上设置有一个电容c

d

,所述电容c

d

的一端与所述线路连接,所述电容c

d

的另一端与vss相连。5.根据权利要求2所述前置锁存比较器,其特征在于,所述第三晶体管组包括nmos晶体管mn4和nmos晶体管mn5;所述nmos晶体管mn4的漏极信号端分别与nmos晶体管mn1的源极信号端和nmos晶体管mn2的源极信号端相连;所述nmos晶体管mn4的源极信号端与所述nmos晶体管mn5的漏极信号端连接;所述nmos晶体管mn5的源极信号端与公共接地端vss相连;所述nmos晶体管mn4的栅极信号端与时钟信号clk的信号端连接;所述nmos晶体管mn5的栅极信号端与时钟信号clkb的信号端连接。6.根据权利要求5所述前置锁存比较器,其特征在于,所述nmos晶体管mn4的源极信号端与所述nmos晶体管mn5的漏极信号端电连接的线路上设有充电电容c

t

;所述充电电容c

t

的一端连接于所述nmos晶体管mn4的源极信号端与所述nmos晶体管mn5的漏极信号端连接的线路上;所述充电电容c

t

的另一端与时钟信号clkb的信号端连接。7.根据权利要求1所述前置锁存比较器,其特征在于,所述锁存器包括高速锁存器和电荷转向电路模块;所述高速锁存器与所述电荷转向电路模块连接。8.根据权利要求6所述前置锁存比较器,其特征在于,所述电荷转向电路模块包括nmos晶体管mn9和nmos晶体管mn10;所述nmos晶体管mn9的漏极信号端与所述高速锁存器的电位点c电连接;所述nmos晶体管mn9的源极信号端与所述nmos晶体管mn10的漏极信号端电连接;所述nmos晶体管mn10的源极信号端与公共接地端vss相连;所述nmos晶体管mn9的栅极

信号端与时钟信号clk的信号端电连接;所述nmos晶体管mn10的栅极信号端与时钟信号clk1b的信号端电连接。9.根据权利要求7所述前置锁存比较器,其特征在于,所述述nmos晶体管mn9的源极信号端与所述nmos晶体管mn10的漏极信号端电连接的线路上设有充电电容c

t

;所述充电电容c

t

的一端连接于所述nmos晶体管mn10的漏极信号端电连接的线路上;所述充电电容c

t

的另一端与时钟信号clk1b的信号端电连接,其中,所述时钟信号clk1b是时钟信号clkb的后延迟信号。10.根据权利要求1所述前置锁存比较器,其特征在于,所述输出缓冲器包括第一输出线路和第二输出线路;第一输出线路和第二输出线路均包括第一反相器、第二反相器和一个与与非门电路;所述第一反相器的信号输出端与所述第二反相器的信号输入端相连;所述第二反相器的信号输出端与所述与门电路的信号输入端相连;所述第一输出线路的信号输出端与所述第二输出线路的与与非门电路的一个信号输入端相连;所述第二输出线路的信号输出端与所述第一输出线路的与与非门电路的一个信号输入端相连。

技术总结

本发明提出了一种高速低功耗的前置锁存比较器。所述前置锁存比较器包括前置放大器、锁存器和输出缓冲器:所述前置放大器,用于对驱动负载的驱动信号进行放大;所述锁存器,用于加速信号比较的输出响应;所述输出缓冲器,用于将所述锁存器的输出信号转换成逻辑信号。用于将所述锁存器的输出信号转换成逻辑信号。用于将所述锁存器的输出信号转换成逻辑信号。

技术研发人员:何越峰 袁国顺 刘晓亮

受保护的技术使用者:无锡中科芯智微电子有限公司

技术研发日:2022.09.06

技术公布日:2022/11/29

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。