一种高隔离度t型模拟开关及其控制电路

技术领域

1.本发明涉及电子电路技术领域,具体但不限于涉及一种高隔离度t型模拟开关及其控制电路。

背景技术:

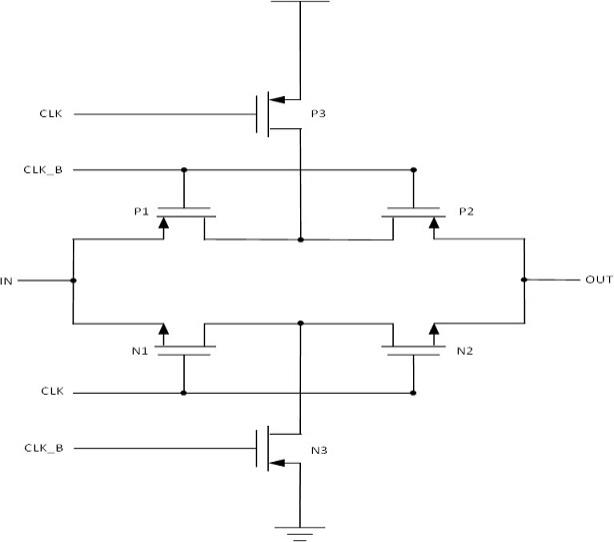

2.现有的高隔离度的t型模拟开关及其控制电路如图1、2所示,理想情况是mos管p1、p2的闭合或断开与mos管p3的断开或闭合是同时发生的,mos管n1、n2的闭合或断开与mos管n3的断开或闭合是同时发生的。即控制信号clk与clk_b是同时变化的。但由于控制信号clk、clk_b对应的负载是不同的,考虑到pvt(工艺process、电压voltage、温度temperature)的影响,控制信号clk与clk_b很可能出现不是同时变化的情况,即控制信号clk、clk_b的变化会有先后关系。

3.当在某一情况下,控制信号clk的变化早于控制信号clk_b的变化时, 控制信号 clk和clk_b的时序图如图3所示,mos管p1、p2的断开比mos管p3的闭合晚,此时t型模拟开关的pmos部分等效电路如图4所示,那么此时,电源与通道间会形成通路,造成漏电。而当mos管n1、n2的闭合早于mos管n3的断开,则此时t型模拟开关的nmos部分等效电路如图5所示,那么此时,通道与地间形成通路,通道向地漏电。同理,控制信号clk的变化晚于控制信号clk_b的变化时,也会造成电源向通道漏电以及通道向地漏电。

4.漏电不仅会增加电路的功耗,还可能导致芯片损伤。有鉴于此,需要提供一种新的结构或控制方法,以期解决上述至少部分问题。

技术实现要素:

5.针对现有技术中的一个或多个问题,本发明提出了一种高隔离度t型模拟开关及其控制电路,其中控制电路改变了t型模拟开关中部分mos管的控制信号,能够避免t型模拟开关切换过程中漏电的发生。

6.实现本发明目的的技术解决方案为:根据本发明的一个方面,一种高隔离度t型模拟开关的控制电路,包括若干级延时模块、若干组反相电路和一个或电路,其中:第一级延时模块的输入端耦接系统的控制信号,输出端耦接第二级延时模块的输入端和或电路的第一输入端,所述或电路的输出端输出第一控制信号,所述第一控制信号经过第一组反相电路后输出第二控制信号;第二级延时模块的输出端分别耦接第三级延时模块的输入端和第四级延时模块的输入端;第三级延时模块的输出端耦接第二组反相电路的输入端,所述第二组反相电路的输出端输出第三控制信号并耦接或电路的第二输入端;第四级延时模块的输出端输出第四控制信号。

7.进一步的,本发明的高隔离度t型模拟开关的控制电路,所述第一级延时模块、第二级延时模块、第三延时模块、第四级延时模块分别包括2n个反相器,所述2n个反相器依次

串联连接,n为正整数。

8.进一步的,本发明的高隔离度t型模拟开关的控制电路,所述第一组反相电路、第二组反相电路分别包括2m-1个反相器,所述2m-1个反相器依次串联连接,m为正整数。

9.进一步的,本发明的高隔离度t型模拟开关的控制电路,包括第三组反相电路和第四组反相电路,其中,第三控制信号经过第三组反相电路后输出第五控制信号,第四控制信号经过第四组反相电路后输出第六控制信号。

10.进一步的,本发明的高隔离度t型模拟开关的控制电路,所述第三组反相电路、第四组反相电路分别包括2p-1个反相器,所述2p-1个反相器依次串联连接,p为正整数。

11.根据本发明的另一个方面,一种高隔离度t型模拟开关,包括上述任一的控制电路以及第一pmos管、第二pmos管、第三pmos管、第一nmos管、第二nmos管和第三nmos管,其中:第一pmos管的源极、第一nmos管的源极共同作为输入端,第二pmos管的源极、第二nmos管的源极共同作为输出端;第一pmos管的漏极、第二pmos管的漏极、第三pmos管的漏极相连,第一pmos管的栅极与第二pmos管的栅极均接入控制电路的第三控制信号;第三pmos管的源极耦接电源电压,第三pmos管的栅极接入控制电路的第一控制信号;第一nmos管的漏极、第二nmos管的漏极、第三nmos管的漏极相连,第一nmos管的栅极与第二nmos管的栅极均接入控制电路的第四控制信号,第三nmos管的源极接地,第三nmos管的栅极接入控制电路的第二控制信号。

12.根据本发明的另一个方面,一种高隔离度t型模拟开关,包括上述任一的控制电路以及第一pmos管、第二pmos管、第三pmos管、第四pmos管、第五pmos管、第一nmos管、第二nmos管、第三nmos管、第四nmos管和第五nmos管,其中:第四pmos管的源极与漏极短接,第五pmos管的源极与漏极短接,第四nmos管的源极与漏极短接,第五nmos管的源极与漏极短接;第一pmos管的源极、第四pmos管的源极、第一nmos管的源极、第四nmos管的源极共同作为输入端,第二pmos管的源极、第五pmos管的源极、第二nmos管的源极、第五nmos管的源极共同作为输出端;第一pmos管的漏极、第二pmos管的漏极、第三pmos管的漏极相连;第一pmos管的栅极与第二pmos管的栅极均接入控制电路的第三控制信号,第四pmos管的栅极与第五pmos管的栅极均接入控制电路的第五控制信号;第三pmos管的源极耦接电源电压,第三pmos管的栅极接入控制电路的第一控制信号;第一nmos管的漏极、第二nmos管的漏极、第三nmos管的漏极相连;第一nmos管的栅极与第二nmos管的栅极均接入控制电路的第四控制信号,第四nmos管的栅极、第五nmos管的栅极均接入控制电路的第六控制信号;第三nmos管的源极接地,第三nmos管的栅极接入控制电路的第二控制信号。

13.本发明采用以上技术方案与现有技术相比,具有以下技术效果:1、本发明的高隔离度t型模拟开关的控制电路,通过反相器的延时作用,防止在开关切换过程中t型隔离开关中的mos管同时闭合的情况出现,避免出现电源与输出之间、或地与输出之间存在通路,避免对输出信号造成影响的情况。

14.2、本发明的高隔离度t型模拟开关的控制电路,避免了开关切换过程中电源向输入输出漏电或输入输出对地漏电,实现了减少动态功耗,同时减小芯片损伤的风险。

附图说明

15.附图用来提供对本发明的进一步理解,与说明描述一起用于解释本发明的实施例,并不构成对本发明的限制。

16.图1示出了现有技术的高隔离度t型模拟开关的示意图。

17.图2示出了现有技术的高隔离度t型模拟开关的控制电路示意图。

18.图3示出了现有技术的高隔离度t型模拟开关的控制信号clk变化早于控制信号clk_b变化的时序图。

19.图4示出了现有技术的高隔离度t型模拟开关的pmos部分等效电路示意图。

20.图5示出了现有技术的高隔离度t型模拟开关的nmos部分等效电路示意图。

21.图6示出了本发明一实施例的高隔离度t型模拟开关的电路示意图。

22.图7示出了本发明一实施例的高隔离度t型模拟开关的控制电路示意图。

23.图8示出了本发明一实施例的高隔离度t型模拟开关的控制电路的控制信号时序图。

24.图9示出了本发明另一实施例的高隔离度t型模拟开关的电路示意图。

25.图10示出了本发明另一实施例的高隔离度t型模拟开关的控制电路示意图。

26.图11示出了本发明另一实施例的高隔离度t型模拟开关的控制电路的控制信号时序图。

具体实施方式

27.为了进一步理解本发明,下面结合实施例对本发明优选实施方案进行描述,但是应当理解,这些描述只是为进一步说明本发明的特征和优点,而不是对本发明权利要求的限制。

28.该部分的描述只针对典型的实施例,本发明并不仅局限于实施例描述的范围。不同实施例的组合、不同实施例中的一些技术特征进行相互替换,相同或相近的现有技术手段与实施例中的一些技术特征进行相互替换也在本发明描述和保护的范围内。

29.实施例1一种高隔离度t型模拟开关的控制电路,如图7所示,包括若干级延时模块、若干组反相电路和一个或电路。其中:第一级延时模块的输入端耦接系统的控制信号cs,输出端耦接第二级延时模块的输入端和或电路or的第一输入端,所述或电路or的输出端输出第一控制信号clk1_b,所述第一控制信号经过第一组反相电路后输出第二控制信号clk1。优选的,第一级延时模块包括反相器inv1和inv2,所述反相器inv1和inv2串联连接。进一步优选的,第一组反相电路包括反相器inv10。

30.第二级延时模块的输出端分别耦接第三级延时模块的输入端和第四级延时模块的输入端。优选的,第二级延时模块包括反相器inv3和inv4,所述反相器inv3和inv4串联连接。

31.第三级延时模块的输出端耦接第二组反相电路的输入端,所述第二组反相电路的输出端输出第三控制信号clk_b并耦接或电路or的第二输入端。优选的,第三级延时模块包括反相器inv5和inv6,所述反相器inv5和inv6串联连接。进一步优选的,第二组反相电路包

括反相器inv7。

32.第四级延时模块的输出端输出第四控制信号clk。优选的,第四级延时模块包括反相器inv8和inv9,所述反相器inv8和inv9串联连接。

33.一种高隔离度t型模拟开关,如图6所示,包括上述控制电路以及第一pmos管p1、第二pmos管p2、第三pmos管p3、第一nmos管n1、第二nmos管n2和第三nmos管n3。其中:第一pmos管p1的源极、第一nmos管n1的源极共同作为输入端,第二pmos管p2的源极、第二nmos管n2的源极共同作为输出端;第一pmos管p1的漏极、第二pmos管p2的漏极、第三pmos管p3的漏极相连,第一pmos管p1的栅极与第二pmos管p2的栅极均接入控制电路的第三控制信号clk_b;第三pmos管p3的源极耦接电源电压,第三pmos管p3的栅极接入控制电路的第一控制信号clk1_b;第一nmos管n1的漏极、第二nmos管n2的漏极、第三nmos管n3的漏极相连,第一nmos管n1的栅极与第二nmos管n2的栅极均接入控制电路的第四控制信号clk,第三nmos管n3的源极接地,第三nmos管n3的栅极接入控制电路的第二控制信号clk1。

34.基于上述的高隔离度t型模拟开关的控制电路,可以使得:第一pmos管p1、第二pmos管p2的闭合晚于第三pmos管p3的断开,而第一pmos管p1、第二pmos管p2的断开早于第三pmos管p3的闭合;第一nmos管n1、第二nmos管n2的闭合晚于第三nmos管n3的断开,而第一nmos管n1、第二nmos管n2的断开早于第三nmos管n3的闭合。上述高隔离度t型模拟开关的控制电路输出的第一控制信号clk1_b、第二控制信号clk1、第三控制信号clk_b和第四控制信号clk的时序图如图8所示。

35.假设反相器inv1的输入的控制信号cs为1时,此通道的输入in与输出out连通,即第一pmos管p1、第二pmos管p2、第一nmos管n1、第二nmos管n2闭合,第三pmos管p3、第三nmos管n3断开;控制信号cs为0时,此通道断开,即第一pmos管p1、第二pmos管p2、第一nmos管n1、第二nmos管n2断开,第三pmos管p3、第三nmos管n3闭合。

36.当系统输入的控制信号cs由1变为0时,如图7-8所示,反相器inv2的输出a由1变为0,然后分成两支路分别向或电路or和反相器inv3传送。或电路or的一个输入b从1变为0,其输出会保持原来的1不变。只有当第三控制信号clk_b也变为0,或电路or的输出、即第一控制信号clk1_b才变为0。所以第四控制信号clk和第三控制信号clk_b的变化要早于第二控制信号clk1、第一控制信号clk1_b的变化。之后经过反相器inv10,第二控制信号clk1变为1。这样第一pmos管p1、第二pmos管p2的断开早于第三pmos管p3的闭合,第一nmos管n1、第二nmos管n2的断开早于第三nmos管n3的闭合。

37.当系统输入的控制信号cs由0变为1时,如图7-8所示,反相器inv2的输出a由0变为1,然后分成两支路分别向或电路or和反相器inv3传送。当或门or的一个输入b变为1时,其输出很快也会从原来的0变为1,而a的变化需要经过几个反向器的延时才会传到第四控制信号clk和第三控制信号clk_b,所以第二控制信号clk1、第一控制信号clk1_b的变化要早于第四控制信号clk和第三控制信号clk_b的变化。这样第一pmos管p1、第二pmos管p2的闭合晚于第三pmos管p3的断开,第一nmos管n1、第二nmos管n2的闭合晚于第三nmos管n3的断开。

38.综上,本方案的控制电路可以使得第一pmos管p1、第二pmos管p2的闭合晚于第三pmos管p3的断开,而第一pmos管p1、第二pmos管p2的断开早于第三pmos管p3的闭合;第一

nmos管n1、第二nmos管n2的闭合晚于第三nmos管n3的断开,而第一nmos管n1、第二nmos管n2的断开早于第三nmos管n3的闭合,从而避免了电路的切换过程中漏电的发生。

39.实施例2一种高隔离度t型模拟开关的控制电路,如图10所示,包括若干级延时模块、若干组反相电路和一个或电路。其中:第一级延时模块的输入端耦接系统的控制信号cs,输出端耦接第二级延时模块的输入端和或电路or的第一输入端,所述或电路or的输出端输出第一控制信号clk1_b,所述第一控制信号经过第一组反相电路后输出第二控制信号clk1。优选的,第一级延时模块包括反相器inv1和inv2,所述反相器inv1和inv2串联连接。进一步优选的,第一组反相电路包括反相器inv10。

40.第二级延时模块的输出端分别耦接第三级延时模块的输入端和第四级延时模块的输入端。优选的,第二级延时模块包括反相器inv3和inv4,所述反相器inv3和inv4串联连接。

41.第三级延时模块的输出端耦接第二组反相电路的输入端,所述第二组反相电路的输出端输出第三控制信号clk_b并耦接或电路or的第二输入端,第三控制信号clk_b经过第三组反相电路后输出第五控制信号clk2_b。优选的,第三级延时模块包括反相器inv5和inv6,所述反相器inv5和inv6串联连接。进一步优选的,第二组反相电路包括反相器inv7。进一步优选的,第三组反相电路包括反相器inv11。

42.第四级延时模块的输出端输出第四控制信号clk,第四控制信号clk经过第四组反相电路后输出第六控制信号clk2。优选的,第四级延时模块包括反相器inv8和inv9,所述反相器inv8和inv9串联连接。进一步优选的,第四组反相电路包括反相器inv12。

43.一种高隔离度t型模拟开关,如图9所示,包括上述控制电路以及第一pmos管p1、第二pmos管p2、第三pmos管p3、第四pmos管p4、第五pmos管p5、第一nmos管n1、第二nmos管n2、第三nmos管n3、第四nmos管n4和第五nmos管n5。其中:第四pmos管p4的源极与漏极短接,第五pmos管p5的源极与漏极短接,第四nmos管n4的源极与漏极短接,第五nmos管n5的源极与漏极短接;第一pmos管p1的源极、第四pmos管p4的源极、第一nmos管n1的源极、第四nmos管n4的源极共同作为输入端,第二pmos管p2的源极、第五pmos管p5的源极、第二nmos管n2的源极、第五nmos管n5的源极共同作为输出端。

44.第一pmos管p1的漏极、第二pmos管p2的漏极、第三pmos管p3的漏极相连;第一pmos管p1的栅极与第二pmos管p2的栅极均接入控制电路的第三控制信号clk_b,第四pmos管p4的栅极与第五pmos管p5的栅极均接入控制电路的第五控制信号clk2_b;第三pmos管p3的源极耦接电源电压,第三pmos管p3的栅极接入控制电路的第一控制信号clk1_b。

45.第一nmos管n1的漏极、第二nmos管n2的漏极、第三nmos管n3的漏极相连;第一nmos管n1的栅极与第二nmos管n2的栅极均接入控制电路的第四控制信号clk,第四nmos管n4的栅极、第五nmos管n5的栅极均接入控制电路的第六控制信号clk2;第三nmos管n3的源极接地,第三nmos管n3的栅极接入控制电路的第二控制信号clk1。

46.基于上述的高隔离度t型模拟开关的控制电路,可以使得高隔离度的模拟开关的电荷注入减小,其输出的第一控制信号clk1_b、第二控制信号clk1、第三控制信号clk_b、第四控制信号clk、第五控制信号clk2_b和第六控制信号clk2的时序图如图11所示。

47.其控制电路工作原理与实施案例1相同,这里不做累述。

48.这里本发明的描述和应用是说明性的,并非想将本发明的范围限制在上述实施例中。说明书中所涉及的效果或优点等相关描述可因具体条件参数的不确定或其它因素影响而可能在实际实验例中不能体现,效果或优点等相关描述不用于对发明范围进行限制。这里所披露的实施例的变形和改变是可能的,对于那些本领域的普通技术人员来说实施例的替换和等效的各种部件是公知的。本领域技术人员应该清楚的是,在不脱离本发明的精神或本质特征的情况下,本发明可以以其它形式、结构、布置、比例,以及用其它组件、材料和部件来实现。在不脱离本发明范围和精神的情况下,可以对这里所披露的实施例进行其它变形和改变。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。