用于dft结构的安全电路

技术领域

1.本公开涉及封装芯片设计,并且更具体地涉及用于封装芯片中dft结构的安全电路。

背景技术:

2.随着芯片的集成规模越来越大、设计越来越复杂,芯片的硬件电路安全性也越来越重要。可测试性设计(dft)理念将一些特殊结构在设计阶段植入芯片,以便设计完成后进行测试。目前大多数芯片由于采用dft设计理念而会用到联合测试工作组(jtag)协议,如美国电气和电子工程师协会(ieee)1149.1标准及其各版本中规定的那样。jtag协议可以访问并测试芯片内部寄存器,同时有时功能设计也会复用dft的jtag端口而访问芯片内的其他寄存器内容。因此,若不为芯片提供dft相关的安全电路,则后续测试或产品应用可能由于一些对jtag协议端口的不确定性复用而访问到芯片内部寄存器的数据,引起数据安全风险,尤其在不想让用户获得一些特别寄存器的内容的情况下。因此,dft相关的硬件电路安全也至关重要。

3.目前,现有芯片的安全电路设计主要是针对功能自身的安全电路设计,在芯片模块内额外加入大部分设计再结合软件操作,会增加许多额外的寄存器且占据芯片面积。而尚未有专门针对dft结构设计的安全电路,尤其是纯硬件电路设计。

技术实现要素:

4.为此,本公开针对上述现状提出一种专门针对芯片中dft端口、尤其是专门针对jtag协议端口设计的硬件安全电路。同时,本公开还提出了针对该硬件安全电路的控制方法,使用户能够打开、暂时锁定或完全锁死对dft端口的访问通道。

5.根据本公开的第一方面,本公开涉及一种用于dft端口的访问控制电路,所述访问控制电路包括控制信号生成模块和钳位模块,所述dft端口包括封装内管脚pad,其中,所述钳位模块串接在所述pad与所述pad相应的封装外管脚pin之间,所述钳位模块的一个输入连接到所述控制信号生成模块的输出,所述钳位模块的另一输入连接到所述pad和其相对应的pin中的一个,并且所述钳位模块的输出连接到所述pad和其相对应的pin中的需要对其进行钳位的另一个;所述访问控制电路响应于操作序列而启用、暂时禁用或永久禁用对所述pad的访问;并且所述控制信号生成模块包括一次性可编程otp器件。

6.根据本公开,通过在dft端口的pad与pin之间串接钳位模块并藉由控制信号生成模块来控制所述钳位模块,可以对到dft端口的pad的输入输出进行钳位,以达到控制对其的访问的目的。所述钳位模块可以是已知的可对其下游电路进行钳位的任何电路或其他模块。作为钳位模块的一个具体示例,逻辑与门具有两个输入和一个输出,只有当其两个输入均为1时其才能输出1,因此可以通过使与门的一个输入为0而将其输出钳位为0(此时,无论其另一输入信号为何其输出都为0),因此该与门即可构成一种钳位模块。此外,所谓对访问的控制,既可以是控制到其的输入,也可以是控制其输入。例如,如果pad连接到钳位模块的

另一输入而钳位模块的输出连接到相对应的pin,则可通过包括控制信号生成模块和钳位模块二者的访问控制电路来控制该pad的输出。相反,如果pin连接到钳位模块的另一输入而钳位模块的输出连接到相对应的pad,则可控制到该pad的输入。此外,根据本公开,通过在访问控制电路、尤其是其控制信号生成模块中包括otp器件,可以通过对otp器件进行编程来永久性地改变控制信号生成模块的输出,从而达到永久锁定/禁用dft端口中的pad的目的。

7.在一个实施例中,所述钳位模块是与门,该与门的一个输入连接到所述控制信号生成模块的输出,其另一输入连接到所述pad和其相对应的pin中的一个,并且其输出连接到所述pad和其相对应的pin中的需要对其进行钳位的另一个。因此,根据该实施例,以pin连接到与门的另一输入而与门的输出连接到相对应的pad为例,当控制信号生成模块的输出为1时,与门的输出仅受与之串接的dft端口的pin的输入信号的影响,也就是相关的pad可正常使用。相反,当控制信号生成模块的输出为0时,无论来自dft端口的pin的输入信号为何,与门的输出都为0,这样就可以锁定到dft端口的相关pad的访问,从而禁用相关的pad。对于与门的另一种连接方式也是如此。

8.在一个实施例中,所述钳位模块是数据选择器mux,该mux的s端连接到所述控制信号生成模块的输出,其i1端连接到所述pad和其相对应的pin中的一个,其输出连接到所述pad和其相对应的pin中的需要对其进行钳位的另一个,并且其i0端钳位为0。数据选择器mux是另一种已知的逻辑电路。根据该实施例,类似于上述与门的情况,当控制信号生成模块输出1时mux输出i1端信号,即正常传递与之串接的dft端口的pin的输入信号或pad的输出信号,这样相关的pad可正常使用。相反,当控制信号生成模块的输出为0时,由于mux的i0端钳位为0,因此同样类似于上述与门的情况,无论mux的i1端输入信号为何,mux的输出都为0,这样就可以锁定到dft端口的相关pad的访问,从而禁用相关的pad。

9.在一个实施例中,所述钳位模块是数据选择器mux,该mux的s端连接到所述控制信号生成模块的输出,其i1端连接到所述pad和其相对应的pin中的一个,其输出连接到所述pad和其相对应的pin中的需要对其进行钳位的另一个,并且其i0端连接到与其i1端所连接到的端口不同的任意其他端口。该实施例与前一实施例的不同之处在于,该mux的i0端连接到与其i1端所连接到的端口不同的任意其他端口,或者说随机连接到任意其他端口信号。此时,当控制信号生成模块的输出为0时,输送到pad或从pad输出到相应的pin的信号是该随机连接的端口信号(即其i0端的输入信号)而不是正确的信号(即其i1端的输入信号),即打乱了信号传递,制造错误的数据对应。在这种情况下,此时的dft端口也无法正常访问,从而禁用相关的pad。

10.在一个实施例中,所述dft端口是jtag协议端口,其至少包括测试时钟管脚tck pad、测试模式选择管脚tms pad、测试数据输入管脚tdi pad以及测试数据输出管脚tdo pad,每个所述钳位模块串接在所述tck pad、tms pad、tdi pad和tdo pad中的任何一个或多个的pad与其相应的pin之间。根据该实施例,通过控制控制信号生成模块的输出,可以锁定jtag协议端口的一组四个pad中的任何一个或多个,从而达到禁用jtag协议端口的目的。

11.在一个实施例中,所述控制信号生成模块包括第一子模块和第二子模块;所述otp器件位于第一子模块中并包括至少一个未经编程的位,并且所述otp器件的未经编程的位在未编程前输出0并在编程后输出1;第一子模块还包括至少一个串接的或门、以及第一非

门,串接的或门的数量与所述otp器件的未经编程的位数相等,所述otp器件的未经编程的每个位连接到每个或门的一个输入,第二子模块的输出连接到串接的第一个或门的另一输入,所述或门的输出串接到其他或门的另一输入或者连接到第一非门的输入,并且第一非门的输出连接到所述控制信号生成模块的输出;并且所述操作序列包括对所述otp器件的至少一个未经编程的位进行编程。根据该实施例,控制信号生成模块包括预留有未经编程的至少一个位的otp器件,并且预留的所述至少一个位的值通过或门和非门的组合直接传送到控制信号生成模块的输出。也就是说,在所述至少一个位保持未被编程的情况下,亦即其读出值保持为0,其不影响或门的输出,因此该otp器件和这些或门的存在不影响访问控制电路的控制。此时,通过控制控制信号生成模块的第二子模块使其输出1或0(此时,由于在控制信号生成模块的输出端存在非门,因此控制信号生成模块的输出为0或1),即可禁用或启用相应的pad。相反,一旦对保留的该至少一个位中的至少一个进行了编程,则被编程的位的输出将永久性地变为1。在这种情况下,由于存在所述至少一个或门和非门,因此控制信号生成模块的输出将永久地变为0,从而永久地禁用相关的pad。因此,通过组合一个otp器件和几个逻辑门,即可实现启用、暂时禁用或永久禁用相关的pad的目的。

12.在一个实施例中,所述otp器件是预留有未烧写的至少一个位的电熔丝efuse。根据该实施例,通过烧写efuse的预留的至少一个位即可对该efuse进行编程,从而实现该otp器件的功能。当然,也可设想除预留有未烧写位的efuse之外的任何其他otp器件,例如otp寄存器等,并相应地设置组合逻辑,只要能通过对其进行编程和/或设置以将控制信号生成模块的输出永久地钳位为特定值即可。优选地,所述efuse预留有未烧写的两个位。通过预留两个位的efuse可实现冗余备份,以防其中一个预留位未能烧写成功。

13.在一个实施例中,所述控制信号生成模块的第二子模块包括:第一1位寄存电路,其d端钳位为1,复位值为0,并且其输出连接到与门的第一输入;第二1位寄存电路,其复位值为0,并且其输出连接到第二非门的输入;第二非门,其输出连接到与门的第二输入;以及与门,其输出连接到串接的第一个或门的所述另一输入;并且其中,所述控制信号生成模块的输出响应于时钟信号和/或复位信号施加于第一1位寄存电路和/或第二1位寄存电路而改变。根据该实施例,只需两个寄存电路、一块efuse和几个组合逻辑即可实现整个控制信号生成模块甚至整个访问控制电路。优选地,所述寄存电路可以是锁存器、d触发器或寄存器或者可实现存储功能的其他电路或模块。

14.在一个实施例中,第一1位寄存电路的时钟信号复用所述封装的时钟信号或来自于所述封装外部,并且其复位信号复用所述封装的系统复位;第二1位寄存电路是dft侧控制寄存电路,其时钟信号复用所述dft端口的时钟信号,并且其复位信号复用所述dft端口的复位信号;并且所述efuse的时钟信号复用所述封装的时钟信号或来自于所述封装外部,并且其复位信号复用所述封装的系统复位。根据该实施例,复用现有信号即可操控访问控制电路中的各器件,而无需专门设置新的信号源。

15.在一个实施例中,第二1位寄存电路是1位dft侧可控寄存器,其在dft侧设计时集成到所述封装的ijtag网络中;并且第一1位寄存电路和/或所述otp器件是所述封装中的现有器件。在诸如ijtag网络之类的dft结构中本就存在可通过dft端口进行控制的寄存器,并且常规芯片都会存在一块或者几块efuse用来烧写芯片的信息或者做mbist修复。因此,根据该实施例,两个1位寄存电路和otp器件都是芯片中的现有电子器件,通过利用芯片中已

有的电子器件来实现本公开的访问控制电路,进一步简化其结构并减小占用面积。

16.根据本公开的第二方面,本公开涉及包括dft端口和如上所述的用于dft端口的访问控制电路的封装芯片。

17.根据本公开的第三方面,本公开涉及如上所述的访问控制电路的控制方法,包括:以第一操作序列操作所述访问控制电路,使得启用对所述pad的访问;和/或以第二操作序列操作所述访问控制电路,使得暂时禁用对所述pad的访问;和/或以第三操作序列操作所述访问控制电路,使得永久禁用对所述pad的访问。根据该实施例,通过以不同的操作序列操作访问控制电路,即可控制对pad的访问,从而启用、暂时禁用或永久禁用dft端口。

18.在一个实施例中,第一操作序列包括向所述第一1位寄存电路施加复位信号,并在所述复位信号未撤离的情况下使第二1位寄存电路输出1;第二操作序列包括向所述控制信号生成模块施加复位信号并然后撤离所述复位信号;并且第三操作序列包括向所述控制信号生成模块施加时钟信号和/或复位信号,并对所述otp器件进行编程。

19.因此,可以看到,根据如上所述的本公开的各方面及其各实施例,本公开针对上述现状而提出了一种简单实用的硬件电路结构,其复用已有芯片的信号,加入几个寄存器和组合逻辑,通过钳位芯片的pad来锁死到jtag端口的访问通道。而且通过几种简单的测试操作流程即可实现该结构的暂时/永久锁定和打开。利用本公开提出的基于硬件电路结构的安全电路,芯片制造商可以在芯片出厂之前决定是否对芯片的用于dft的jtag协议端口进行锁死使得用户不能应用jtag端口访问芯片内部寄存器,从而保护芯片的硬件安全。利用根据本公开的一个或多个优选实施例,可通过访问控制电路打开、暂时锁定或完全锁死jtag协议端口的tck、tms、tdi和tdo这组pad,消除了对jtag协议端口的不确定性复用而引起的数据安全风险。

20.要注意的是,在本公开的不同方面中描述的一个或多个特征可与在其他方面中描述的一个或多个特征相结合以形成本公开的实施例。因此,上面描述的实施例并非是穷举性的。

附图说明

21.通过阅读下面的详细描述并研究附图,其他特征、细节和优点将变得显而易见,其中:图1示意性地示出了封装芯片,其包括根据本公开的一个实施例的访问控制电路;图2示意性地示出了根据本公开的另一实施例的访问控制电路;图2-1示意性地示出了图2的访问控制电路的第一变型;图2-2示意性地示出了图2的访问控制电路的第二变型;图3是根据本公开的一个实施例的控制方法的第一流程图;图4是根据本公开的一个实施例的控制方法的第二流程图;以及图5是根据本公开的一个实施例的控制方法的第三流程图。

具体实施方式

22.接下来参考附图来描述本公开的具体实施例。在附图和接下来的描述中,出于必要性而包含了某些性质的元素。这些元素不仅可以用来更好地理解本公开,而且在必要时

也有助于限定本公开。

23.图1示意性地示出了封装芯片100,其包括根据本公开的一个实施例的访问控制电路。例如,封装芯片100可以是处理器、存储器、片上系统(soc)等任何目前已知的或将来开发的芯片。如已知的那样,芯片一般需进行封装以供使用,封装后的芯片包括封装内管脚,一般称为pad,和封装外管脚,一般称为pin,以用于实现芯片的内部和内部以及内部和外部的各种电连接。在封装后,除非进行拆片,否则从外部只能访问/连接到暴露于封装外的pin而无法直接访问/连接到封装内的pad。图1中示意性地示出了封装芯片100所包括的pad 103和pin 104。显然,封装芯片100可根据需要而包括任意数量的pin和pad。

24.如已知的那样,封装芯片100尤其可以包括芯片核101,例如芯片的核心功能电路模块。此外,封装芯片100还可以包括各种其他功能电路模块、端口、布线等等,如已知的那样,但是为了便于图示和理解,此处并未示出和具体描述。

25.另外,封装芯片100还可以包括dft端口102,即用于芯片诊断测试的端口,可在芯片封装后通过dft端口102对芯片的可用性和性能等进行测试。dft端口102可以是根据各种协议,例如ieee 1149.1标准及其各版本中规定的jtag协议、ieee 1687标准中规定的ijtag协议、以及能够用于芯片测试各种协议及其已有版本和未来开发的版本。dft端口102可以包括至少一个封装内管脚,如pad 103,以实现数据输入输出。pad 103可以连接到封装芯片100内的各种电路器件,也可以连接到封装芯片100的封装外管脚,例如,图1中图示了两个pad 103与pin 104的连接。一般来说,为了进行芯片测试,需要从芯片外向芯片内输入信号以及从芯片内向芯片外输出信号,这些都是通过各封装内管脚和封装外管脚之间的通信实现的。因此,dft端口102通常具有相对应的成对的封装内管脚和封装外管脚。在dft端口102是根据jtag协议实现的端口的情况下,dft端口102至少包括测试时钟管脚tck pad、测试模式选择管脚tms pad、测试数据输入管脚tdi pad、测试数据输出管脚tdo pad以及测试复位管脚trst pad,如jtag协议中规定的那样。

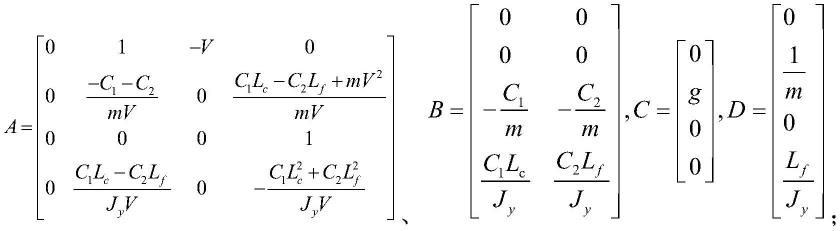

26.如上所述,在现有技术中,dft端口102除了用于芯片测试之外,还可能被复用以访问芯片内的其他寄存器内容,进而影响芯片的数据安全。此外,通过dft端口102对芯片进行的测试可能是在芯片出厂前由芯片制造商进行的,也可能是在芯片出厂后由第三方进行的。而制造商可能不希望任何第三方在芯片出厂后通过dft端口102访问芯片内的数据。因此,需要针对封装芯片中的dft端口的安全电路,从而使得能够控制对dft端口的访问。

27.为此,根据本公开,封装芯片100还可以包括访问控制电路105,以控制对dft端口102的访问。访问控制电路105包括控制信号生成模块106和钳位模块107。

28.钳位模块107可以是已知的可对其下游电路进行钳位的任何模块,包括软件模块、硬件模块、软件和硬件的结合,等等。例如,钳位模块可以是逻辑与门、数据选择器mux、逻辑非门、有源钳位电路、或者通过软件编程进行值配置以实现钳位的结构等等。为了控制对dft端口102的访问,需要将控制信号生成模块106的输出连接到钳位模块107的一个输入,并且将钳位模块107的输出连接到要对其进行钳位的pin或pad。至于钳位模块107的其他一个或多个输入,可以由本领域技术人员根据电路的具体布置进行连接。图1示出了关于钳位模块107的连接方式的两个简单示例,以虚线示出了信号的输入输出。在钳位模块107的上侧,可以看到其输出连接到dft端口102的pad 103,并且其另一输入连接到与pad 103相对应的pin 104,这样的钳位模块连接方式可以对到该pad 103的输入进行钳位。因此,以与门

为例,只有在来自pin 104的输入信号和来自控制信号生成模块106的输入信号均为1的情况下,钳位模块107的输出才为1。当来自控制信号生成模块106的输入信号为0时,无论来自pin 104的输入信号为何,钳位模块107的输出都为0,也就是说,在这种情况下,钳位模块107阻断了来自pin 104的输入信号,使之无法到达pad 103,从而禁用了该封装内管脚。因此,通过控制控制信号生成模块106的输出,藉由钳位模块107,即可控制到pad 103的输入,从而控制其访问。作为另一示例,在钳位模块107的下侧示出了另一种连接方式,即控制pad 的输出。在这种情况下,pad连接到钳位模块107的另一输入,并且钳位模块107的输出连接到与该pad相对应的pin,按照如上所述的同样的原理,可以控制该pad的输出,使得无论该pad原本输出了什么,只要钳位模块107(例如,与门)钳位为0,就无法经由与该pad相关联的pin从封装芯片100外部读出任何有效数据。

29.进一步地,控制信号生成模块106还可以包括otp器件108。otp(one time programmable)器件即一次性可编程器件,即仅可进行一次编程,在程序写入(例如烧写)其中后,将不可再次更改和清除。因此,一般而言,otp器件在被编程前和编程后具有不同的输出,且编程后的输出不可再更改,具有永久性。因此,通过在控制信号生成模块106中包括otp器件108,可藉由对otp器件108编程而永久地改变控制信号生成模块106的输出。

30.根据本公开,由于控制信号生成模块106的输出为0即可通过钳位模块107将到pad 103的输入钳位为0,如上所述,因此,可以如下控制访问控制电路105:

‑ꢀ

在不对otp器件108进行编程的情况下,将控制信号生成模块106的输出控制为1,于是访问控制电路105的输出信号不会影响pin 104与pad 103的通信,pad 103可正常访问;

‑ꢀ

在不对otp器件108进行编程的情况下,将控制信号生成模块106的输出控制为0,于是到pad 103的输入被钳位模块107钳位为0,锁定了pad 103;以及

‑ꢀ

对otp器件108进行编程,使得控制信号生成模块106的输出永久为0,于是到pad 103的输入被钳位模块107永久性地钳位为0,彻底禁用了pad 103。

31.因此,根据本公开,通过为dft端口102设置包括控制信号生成模块106和钳位模块107的访问控制电路105,并且通过在访问控制电路105、尤其是控制信号生成模块106中包括otp器件108,可以通过控制访问控制电路105而打开、暂时锁定或永久锁定对封装内管脚(例如,pad 103)的访问,从而启用、暂时禁用或永久禁用dft端口102。

32.根据本公开,通过包括控制信号生成模块106和钳位模块107的访问控制电路105进行访问控制的封装内管脚可以是dft端口102的封装内管脚中的一个、几个或全部。本领域技术人员可以根据dft端口102所实施的协议的具体规定、电路的具体设计或实际需求来选择要按照本公开进行控制的封装内管脚。例如,在dft端口102是根据jtag协议实现的端口的情况下,可以按照本公开对tck pad、tms pad、tdi pad和tdo pad进行控制,而不管trst pad,也可以控制全部上述五个封装内管脚,或者甚至可以仅控制例如tdi pad,只要能够通过对特定封装内管脚的控制而锁定该端口即可。

33.此外,根据本公开,控制信号生成模块106的除otp器件108外的其余部分和钳位模块107可以根据电路的具体设计或实际需求来设置。也就是说,控制信号生成模块106的除otp器件108外的其余部分可以是黑盒模块,只要可以通过控制控制信号生成模块106而输出两个不同的电平即可,钳位模块107也是同理。因此,访问控制电路105可以具有软件模

块、是纯硬件电路、或者是软件与硬件的结合。并且访问控制电路105的输入可以是来自封装芯片100内或来自封装芯片100外,可以是预置输入或用户输入等等。本领域技术人员可以基于本公开的构思结合实际情况而任意地设计该访问控制电路而不会脱离本公开的范围。

34.接下来参考图2来描述本公开的一个特别优选的实施例。

35.图2示意性地示出了根据本公开的另一实施例的访问控制电路。为了突出重点,图2中仅详细示出了包括在访问控制电路中的控制信号生成模块200和钳位模块210的电路图,而省略了封装芯片的部分其他构造,例如图1中示出的芯片核、dft端口、封装外管脚等。

36.在本实施例中,dft端口是根据jtag协议实现的端口,其至少包括tck pad、tms pad、tdi pad、tdo pad和trst pad,如上所述。此外,在本实施例中,钳位模块210是一组4个与门,每个与门串接在控制信号生成模块200的输出与tck pad、tms pad、tdi pad和tdo pad中的每一个之间。具体来说,tck pad、tms pad和tdi pad是信号输入管脚,并且tdo pad是信号输出管脚。因此,对于图2中右侧的包括在钳位模块210中的从上到下的四个与门:

‑ꢀ

第一个与门用于对tck信号进行钳位,其一个输入连接到控制信号生成模块200的输出,其另一输入连接到tck pin(未示出,仅以信号tck示意性地表示),并且其输出连接到tck pad(未示出,仅以信号tck_to_core示意性地表示),再通过pad输送到芯片内部,其中tck pin是封装芯片从外部接收tck信号所使用的封装外管脚;

‑ꢀ

第二个与门用于对tms信号进行钳位,其一个输入连接到控制信号生成模块200的输出,其另一输入连接到tms pin(未示出,仅以信号tms示意性地表示),并且其输出连接到tms pad(未示出,仅以信号tms_to_core示意性地表示),再通过pad输送到芯片内部,其中tms pin是封装芯片从外部接收tms信号所使用的封装外管脚;

‑ꢀ

第三个与门用于对tdi信号进行钳位,其一个输入连接到控制信号生成模块200的输出,其另一输入连接到tdi pin(未示出,仅以信号tdi示意性地表示),并且其输出连接到tdi pad(未示出,仅以信号tdi_to_core示意性地表示),其中tdi pin是封装芯片从外部接收tdi信号所使用的封装外管脚;以及

‑ꢀ

第四个与门用于对tdo信号进行钳位,其一个输入连接到控制信号生成模块200的输出,其另一输入连接到tdo pad(未示出,仅以信号tdo示意性地表示),并且其输出连接到tdo pin(未示出,仅以信号tdo_from_core示意性地表示),其中tdo pin是向封装芯片外部传送tdo信号所使用的封装外管脚。

37.因此,根据本实施例,可以通过操控包括控制信号生成模块200和钳位模块210的访问控制电路来同时启用或禁用jtag端口的tck pad、tms pad、tdi pad和tdo pad,从而启用或禁用jtag端口。

38.进一步地,在本实施例中,控制信号生成模块200采用纯硬件电路的方式来实现,并且包括:

‑ꢀ

1位功能寄存器201,其d端输入钳位为1(图中示为tie1),其时钟信号直接来自于芯片外部或者复用芯片的时钟信号(未示出),其复位信号复用芯片的系统复位sys_rst,复位值为0,并且其输出连接到与门204的一个输入;

‑ꢀ

1位dft侧可控寄存器202,寄存器202是dft可读可写寄存器,是ijtag网络中的某个预留寄存器,可在设计时集成到芯片的ijtag网络中。寄存器202的时钟信号复用jtag

的测试时钟信号tck,其复位信号复用jtag的测试复位信号trst,复位值为0,并且其输出连接到非门203;

‑ꢀ

非门203,其输入连接到寄存器202的输出,并且其输出连接到与门204的另一输入;

‑ꢀ

与门204,其一个输入连接到寄存器201的输出,其另一输入连接到非门203的输出,并且其输出连接到或门206的一个输入;

‑ꢀ

efuse 205,其为图1中描述的otp器件108的一个具体实施方式。常规芯片都会存在一块或者几块efuse用来烧写芯片的信息或者做mbist 修复,因此efuse 205可以是芯片中已有的efuse。efuse 205需要预留有未烧写的至少一个位,即读出值为0。在本实施例中,预留了两个未烧写的位。efuse 205的时钟信号直接来自于芯片外部或者复用芯片的时钟信号(未示出),其复位信号复用芯片的系统复位sys_rst,该复位信号用于触发efuse 205的读操作;

‑ꢀ

或门206,其一个输入连接到与门204的输出,其另一输入连接到efuse 205的被预留未烧写的两个位之一,并且其输出连接到或门207;

‑ꢀ

或门207,其一个输入连接到或门206的输出,其另一输入连接到efuse 205的被预留未烧写的两个位中的另一个,并且其输出连接到非门208;以及

‑ꢀ

非门208,其输入连接到或门207的输出,并且其输出连接到控制信号生成模块200的输出。

39.在该控制信号生成模块200中,efuse 205、或门206、或门207和非门208在功能上构成了控制信号生成模块200的第一子模块,其作用主要是通过对efuse的编程(烧写)操作来控制控制信号生成模块200的输出,从而永久地改变其输出。而1位功能寄存器201、1位dft侧可控寄存器202、非门203和与门204在功能上构成了控制信号生成模块200的第二子模块,其作用主要是通过施加在两个寄存器上的时钟信号和/或复位信号来控制控制信号生成模块200的输出,从而暂时性地改变其输出。

40.因此,通过控制两个寄存器201和202的输入,即时钟信号输入和复位信号输入,并且通过烧写efuse 205的被预留的两个位,即可以结构简单的纯硬件电路实现jtag端口的访问控制。此外,根据该实施例,所利用的复位和时钟信号都是直接复用芯片原本已有的信号,即芯片时钟信号、tck、sys_rst和trst,而且其中的寄存器和efuse也都尽可能地利用现有框架中可用的原始器件,例如ijtag中现有的寄存器等,从而在尽可能不占用芯片的额外面积的情况下实现访问控制。

41.图2-1示出了图2的访问控制电路的第一变型。在该变型中,控制信号生成模块200与图2中所示的相同,因此不再进行描述,而钳位模块210-1采用的不是一组与门,而是一组四个数据选择器mux。如图所示,该组mux的总体连接方式与图2中的与门类似:每个mux的输出端连接到要被钳位的pad或pin(前三个为pad,最后一个为pin),其i1端(即选择信号为1时被选为输出的输入端)连接到与之相关联的pin或pad(前三个为pin,最后一个为pad),其s端(即数据选择控制端)连接到控制信号生成模块200的输出,并且该组mux的i0端(即选择信号为0时被选为输出的输入端)均钳位为0(图中示为tie0)。根据该实施例,类似于图2的情况,当控制信号生成模块200输出1时,mux输出i1端信号,即正常传递与之串接的pin或pad的信号,这样相关的pad可正常使用。相反,当控制信号生成模块的输出为0时,无论mux

的i1端输入信号为何,mux的输出都被钳位为0,从而禁用相关的pad。该禁用可以是暂时性的,也可以通过烧写控制信号生成模块200中的efuse 205而是永久性的。

42.图2-2 示出了图2的访问控制电路的第二变型。该变型总体上与图2-1中示出并在上一段中描述的第一变型相同,唯一的差异在于,该组mux的i0端随机连接到其他端口信号。所述其他端口信号可以是其他jtag协议端口信号。例如,图2-2中示出,第一个mux的i0端连接到了tdi信号(以彩色斜体示出),第二个mux的i0端连接到了tck信号,第三个mux的i0端连接到了tms信号,并且第四个mux的i0端连接到了trst信号。当然,图2-2中示出的仅是一种示例情况,所述其他端口信号可以是任何其他信号,只要其能扰乱被钳位的pad的输入输出,使之不能正常使用即可。根据本实施例,当控制信号生成模块200输出1时,mux输出i1端信号,即正确的jtag输入信号,这样相关的pad可正常使用。而当控制信号生成模块200输出0时,mux输出i0端信号,即不是正确的对应的jtag信号,这样就打乱了jtag协议对应的端口,制造错误的数据对应,从而使该jtag端口无法正确访问。

43.接下来描述根据本公开的访问控制电路的控制方法,以使用户能够启用、暂时禁用或完全禁用对dft端口的访问,该描述是参考图2的访问控制电路和图3至图5的流程图进行的。

44.图3示出了对访问控制电路进行操作以启用jtag端口的操作流程的示例,其包括第一操作序列300。

45.如图3所示,首先,在芯片测试或者应用时,例如在对芯片上电时,一直施加sys_rst复位信号(301),以将寄存器201的输出钳位为0,此时与门204输出值为0,同时efuse 205由于尚未烧写,因此输出值也为0,那么最终到非门208的输出为1。于是控制信号生成模块200的输出为1,连接在控制信号生成模块200与jtag端口之间的钳位模块的输出仅受其另一输入信号的影响,也就是此时没有对jtag端口进行钳位。此时通过将寄存器202写为1并撤离sys_rst(302),与门204由于寄存器202的输出值为1而输出0,于是效果和sys_rst处于一直复位的状态一致,都会使控制信号生成模块200的输出值为1从而启用jtag端口。在控制信号生成模块200中,由于寄存器202是1位dft侧可控寄存器,可受dft端口控制,因此将寄存器202写为1可以是通过ieee 1687协议写入寄存器202使其q端输出1,可直接通过在操作302之前已通过操作301而启用的dft端口来进行。也就是说,在系统复位sys_rst一直处于复位态时,在jtag端口处于有效的该时间段内利用有效的jtag端口将dft侧可控寄存器202配置为1,这样在撤离系统复位后就可以保证在芯片正常工作情况下仍能访问jtag端口。

46.图4示出了对访问控制电路进行操作以暂时禁用jtag端口的操作流程的示例,其包括第二操作序列400。

47.如图4所示,首先,在芯片测试或者应用时,例如在对芯片上电时,先做复位操作(401),即向控制信号生成模块200施加sys_rst和trst,以消除电路中寄存器201、202和efuse 205的不定态。然后撤离复位(402),此时寄存器201的输出值为0,并且寄存器202的输出值为0。由于寄存器201的时钟信号直接来自于芯片外部或者复用芯片的时钟信号,那么在撤离复位后经过几个周期后,寄存器201的输出值将跳为1。此时,与门204的输出值为1。由于efuse在未进行烧写前预留的两个位均为0,因此这两个位在时钟信号的作用下读出数据为0。此时根据efuse 205的输出以及与门204的输出,可以确定非门208的输出为0,于

是控制信号生成模块200的输出为0,并且藉由连接在控制信号生成模块200与jtag端口之间的钳位模块,jtag端口的各个pad均会被钳位为0。那么此时就无法通过jtag端口访问芯片内部数据,从而锁住芯片的dft端口。但是此时电路并非是彻底锁死,而是暂时性锁定。

48.图5示出了对访问控制电路进行操作以永久禁用jtag端口的操作流程的示例,其包括第三操作序列500。

49.如图5所示,假如希望锁死或者说永久锁定该芯片的jtag端口,此时只需要烧写(502)efuse 205预留的两个位中的一位即可。根据图2所示的访问控制电路的组合逻辑,只要efuse 205的某一位烧写为1,则非门208的输出必为0,于是jtag端口必会被钳位为0且无法再更改。efuse 205预留两个位是为了防止预留的位未能烧写成功而做的冗余备份。当然,在烧写efuse 205之前,首先需要通过上电、对efuse 205施加时钟信号(clk)和/或复位信号(sys_rst)等方式来触发efuse 205读操作(501),如本领域技术人员已知的那样。

50.上面的描述是参考图2的访问控制电路和图3至图5的流程图进行的,然而,根据本公开的控制方法不限于此。例如,可以结合访问控制电路中的控制信号生成模块和钳位模块的具体实施方式来设计其具体操作,只要使其按需输出0或1即可。

51.通过上面三种操作流程,可以让芯片的dft端口处于用户期望的状态。因此,假如芯片制造商不希望在芯片出厂后第三方通过复用dft端口访问芯片内部而威胁到芯片内数据安全,则可以根据本公开通过对芯片内预留的otp器件进行编程来在完成dft测试后、在芯片出厂前实现dft端口的永久锁死,避免了第三方藉由dft端口进行的任何恶意攻击或反向工程。在这种情况下,因为该硬件电路是做在芯片内部的,且一般芯片制造通过光刻完成电路实现,那么在通过根据本公开的访问控制电路实现了永久锁死之后,就无法通过拆除封装或者其他手段来恢复jtag端口的访问,完全保证了芯片的数据安全。假如芯片处于回片测试验证状态,则只需将dft端口通过上述访问控制电路而开启即可。本公开不限于以上仅作为示例描述和展示的实施例,而是涵盖了本领域技术人员在所寻求的保护上下文中可设想到的所有变型。此外,本公开不限于仅针对dft端口而实施,可以通过移植本公开的构思来实现其他类似端口的访问控制,例如功能逻辑外部访问端口、芯片功能逻辑调试(debug)端口等。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。