1.本发明涉及通信技术领域,尤其涉及一种无线互连装置及系统。

背景技术:

2.随着集成电路工艺的进步,处理器的性能大幅提升,与此相对应的内存性能提升速度相对较慢,造成了当前内存的存取速度严重滞后于处理器的计算速度,从而导致高性能处理器难以发挥出应有的功效,这对日益增长的高性能计算(high performance computing,hpc)造成了极大的制约,该现象也被称为内存墙现象(memory wall)。

3.现有技术中,传统处理器和内存通常采用pcb(printed circuit board)互连方式和hbm方式(high bandwidth memory)连接,其中:

4.(1)、pcb互连方式使得信号走线长度较长、走线密度难以提升、信号传输速率和信号带宽很难进一步提升,严重制约了高性能处理器的计算性能;

5.(2)、hbm技术是利用2.5d、3d等高级封装将处理器和存储器集成在同一封装内,如图1所示,二者之间采用硅转接板进行互连,相较于pcb方式,其信号走线长度更短、走线密度更高、可以提供更高的信号传输速率和更大的信号带宽。但在hbm方式中,处理器和存储器仍为水平放置,二者之间走线距离仍然较长,而且,处理器和存储器与基板之间通过微凸点、混合键合、键合打线实现互连时,存在互连密度较低及互连可靠性问题,即当互连数量相对少时,通过冗余编码等技术可以提高互连连接成品率,但当互连数量达到数万个以上时,互连连接成品率将大幅下降,故信号传输速率和信号带宽提高仍受限。

技术实现要素:

6.本发明提供一种无线互连装置及系统,用以解决现有技术中因走线长度过长以及互连密度较低导致的信号传输速率和信号带宽提升受限的缺陷,增大无线互连密度,实现信号高速传输且增大信号带宽,进一步提升连接可靠性。

7.本发明提供一种无线互连装置,包括:第一模块、第二模块、mcm基板、至少一个电容和球栅阵列,其中:

8.所述球栅阵列设于所述mcm基板下方;

9.所述第一模块设于所述mcm基板上;

10.所述第二模块设于所述第一模块上,且所述第二模块和所述第一模块的电源和地以键合方式连接,其中,所述键合方式包括微凸点方式、混合键合方式和键合打线方式的一种;

11.所述至少一个电容设于所述第二模块和所述第一模块之间,用于实现所述第一模块和所述第二模块的数字信号无线互连。

12.根据本发明提供的无线互连装置,所述第二模块和所述第一模块上均设有pad焊盘,所述第二模块和所述第一模块的电源和地基于所述pad焊盘以键合打线方式连接时,所述第二模块和所述第一模块之间基于daf膜粘接或基于硅硅键合方式将晶圆键合在一起,

所述第一模块的电源和地与所述mcm基板以键合打线方式连接。

13.根据本发明提供的无线互连装置,所述第二模块和所述第一模块之间设有金属键合垫,所述第二模块的电源和地与所述第一模块基于所述金属键合垫以混合键合方式连接,所述第一模块的电源和地与所述mcm基板以键合打线方式连接。

14.根据本发明提供的无线互连装置,所述第一模块和所述第二模块内均设有第二硅通孔,所述第二硅通孔与所述金属键合垫处于同一竖直轴线上,且用于支撑所述金属键合垫。

15.根据本发明提供的无线互连装置,所述第二模块和所述第一模块之间设有微凸点,所述第二模块的电源和地与所述第一模块基于所述微凸点以微凸点方式连接,所述第一模块的电源和地与所述mcm基板以键合打线方式连接。

16.根据本发明提供的无线互连装置,所述第一模块下设有凸点,所述第一模块的电源和地与所述mcm基板还基于所述凸点连接,所述第二模块的电源和地与所述mcm基板以键合打线方式连接。

17.根据本发明提供的无线互连装置,所述第一模块下设有凸点,所述第一模块的电源和地与所述mcm基板基于所述凸点连接,所述第一模块与所述第二模块的电源和地基于所述金属键合垫以混合键合方式连接。

18.根据本发明提供的无线互连装置,所述第一模块下设有凸点,所述第一模块的电源和地与所述mcm基板基于所述凸点连接,所述第一模块与所述第二模块的电源和地基于所述微凸点连接。

19.根据本发明提供的无线互连装置,所述第一模块包括电路层和衬底层,在所述第一模块的电源和地与所述mcm基板基于所述凸点连接的情况下,所述第一模块内设有至少两个第一硅通孔,其中,所述第一硅通孔用于连接所述电路层和所述衬底层的所述电容。

20.本发明还提供一种无线互连系统,包括:

21.如上述任一项所述的无线互连装置。

22.本发明提供的一种无线互连装置及系统,将第二模块设置于第一模块上方,且通过电容无线互连提高第一模块和第二模块之间的互连数量,通过大幅度提升互连密度实现高速高密度数字信号传输,进一步提高信号传输可靠性和互连连接成品率;此外,还通过键合打线方式实现电源、地等低速低密度信号传输,进一步提升无线互连装置的可靠性。

附图说明

23.为了更清楚地说明本发明或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作一简单地介绍,显而易见地,下面描述中的附图是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

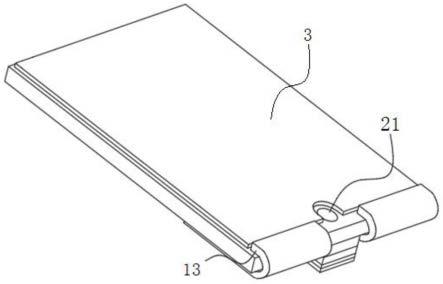

24.图1是现有技术中的无线互连装置的结构示意图;

25.图2是本发明提供的无线互连装置的结构示意图之一;

26.图3是本发明提供的无线互连装置的结构示意图之二;

27.图4是本发明提供的无线互连装置的结构示意图之三;

28.图5是本发明提供的无线互连装置的结构示意图之四;

29.图6是本发明提供的无线互连装置的结构示意图之五;

30.图7是本发明提供的无线互连装置的结构示意图之六;

31.图8是本发明提供的无线互连装置的结构示意图之七;

32.图9是本发明提供的无线互连装置的结构示意图之八。

具体实施方式

33.为使本发明的目的、技术方案和优点更加清楚,下面将结合本发明中的附图,对本发明中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

34.针对现有技术的问题,本发明提供了一种无线互连装置,图2是本发明提供的无线互连装置的结构示意图之一,如图2所示,该无线互连装置包括:第一模块1、第二模块2、mcm基板8、至少一个电容3和球栅阵列7,其中:

35.所述球栅阵列7设于所述mcm基板8下方;

36.所述第一模块1设于所述mcm基板8上;

37.所述第二模块2设于所述第一模块1上,且所述第二模块2和所述第一模块1的电源和地以键合方式连接,其中,所述键合方式包括微凸点方式、混合键合方式和键合打线方式的一种;

38.所述至少一个电容3设于所述第二模块2和所述第一模块1之间,用于实现所述第一模块1和所述第二模块2的数字信号无线互连。

39.具体地,将第二模块2与第一模块1由水平放置改为垂直堆叠放置,且第二模块2和第一模块1之间采用电容3进行无线互连,将水平走线方式改为垂直相对方式,大幅度缩短走线长度,进一步增加互连数量和互连密度,且通过电容3实现信号的可靠高速传输,进而提高信号传输速率和信号带宽。此外,第二模块2和第一模块1均与mcm(multi-chip module,多芯片组件)基板以键合打线方式连接,实现电源和地等低密度信号传输,提高连接可靠性和互连成品率,且减小处理器体积,进一步实现小型化。

40.可选地,第一模块与第二模块的结构组成可以为处理器与存储器、处理器与接口、存储器和存储器中的任意一种,即第一模块可以为处理器或存储器,在第一模块为处理器的情况下,第二模块可以为存储器或接口,在第一模块为存储器的情况下,第二模块可以为存储器。

41.可选地,上述接口可以为高速并行互连接口。

42.可选地,上述电容3的一个金属极板可以采用第一模块1的顶层金属层进行制作,减小电容3的面积。

43.可选地,上述电容3可以为差分式电容3,进一步提高数据无线传输的噪声抑制能力。

44.可选地,所述第二模块2和所述第一模块1上均设有pad焊盘,所述第二模块2和所述第一模块1的电源和地基于所述pad焊盘以键合打线方式连接时,所述第二模块2和所述第一模块1之间基于daf膜12粘接或基于硅硅键合方式将晶圆键合在一起,所述第一模块1的电源和地与所述mcm基板以键合打线方式连接。

45.具体地,本发明实施例中,在第二模块2和第一模块1均与mcm基板8以键合打线方式连接的情况下,第二模块2和第一模块1之间可以通过daf膜12(die attach film,晶片黏结薄膜)进行粘接,还可以通过硅硅键合方式将晶圆键合在一起,以便进行信号传输。其中,daf膜12用于实现第二模块2和第一模块1的堆叠封装;硅硅键合是通过两个表面平整洁净的硅片在一定条件下可以通过表面的化学键互相连接起来,硅硅键合连接灵活且对半导体工艺具有兼容性。

46.可选地,如图2所示,本发明实施例提供了一种无线互连装置,以第一模块1为处理器,第二模块2为存储器为例,对该无线互连装置进行详细描述。处理器以正装方式设置于mcm基板8上,即处理器的电路层4在上,衬底层6在下;处理器的电源和地通过键合打线方式与mcm基板8连接,即,处理器的电源和地的pad焊盘13通过键合线14与mcm基板8连接,存储器和处理器之间通过硅硅键合方式将晶圆键合在一起;存储器的电源和地通过键合打线方式与mcm基板8连接,即,存储器的电源和地的pad焊盘13通过键合线14与mcm基板8连接,实现低速低密度信号传输,球栅阵列7bga(ball grid array)设于mcm基板8下方;处理器和存储器的内部分别设置一个金属极板,两个相对的金属极板形成电容3,实现信号高速高密度无线传输。

47.可选地,图3是本发明提供的无线互连装置的结构示意图之二,如图3所示,本发明实施例提供了一种无线互连装置,以第一模块1为处理器,第二模块2为存储器为例,对该无线互连装置进行详细描述。处理器以正装方式设置于mcm基板8上,即处理器的电路层4在上,衬底层6在下;处理器的电源和地通过键合打线方式与mcm基板8连接,即,处理器的电源和地的pad焊盘13通过键合线14与mcm基板8连接,存储器和处理器之间通过daf膜12方式进行粘接;存储器的电源和地通过键合打线方式与mcm基板8连接,即,存储器的电源和地的pad焊盘13通过键合线14与mcm基板8连接,实现低速低密度信号传输,球栅阵列7bga设于mcm基板8下方;处理器和存储器的内部分别设置一个金属极板,两个相对的金属极板形成电容3,实现信号高速高密度无线传输。

48.可选地,所述第二模块2和所述第一模块1之间设有金属键合垫11,所述第二模块2的电源和地与所述第一模块1基于所述金属键合垫11以混合键合方式连接,所述第一模块1的电源和地与所述mcm基板8以键合打线方式连接。

49.具体地,图4是本发明提供的无线互连装置的结构示意图之三,如图4所示,本发明实施例还提供一种无线互连装置,以第一模块1为处理器,第二模块2为存储器为例,对该无线互连装置进行详细描述。处理器以正装方式设置于mcm基板8上,即处理器的电路层4在上,衬底层6在下;处理器的电源和地通过键合打线方式与mcm基板8连接,即,处理器的电源和地的pad焊盘13通过键合线14与mcm基板8连接,存储器和处理器之间的电源和地通过金属键合垫11以混合键合方式进行连接,实现低速低密度信号传输,处理器和存储器内的第二硅通孔tsv对金属键合垫11起到支撑作用,球栅阵列7bga设于mcm基板8下方;处理器和存储器的内部分别设置一个金属极板,两个相对的金属极板形成电容3,实现信号高速高密度无线传输。

50.可选地,所述第一模块1和所述第二模块2内均设有第二硅通孔,所述第二硅通孔与所述金属键合垫11处于同一竖直轴线上,且用于支撑所述金属键合垫11。

51.可选地,所述第二模块2和所述第一模块1之间设有微凸点10,所述第二模块2的电

源和地与所述第一模块1基于所述微凸点10连接,所述第一模块1的电源和地与所述mcm基板8以键合打线方式连接。

52.具体地,图5是本发明提供的无线互连装置的结构示意图之四,如图5所示,本发明实施例还提供一种无线互连装置,以第一模块1为处理器,第二模块2为存储器为例,对该无线互连装置进行详细描述。处理器以正装方式设置于mcm基板8上,即处理器的电路层4在上,衬底层6在下;处理器的电源和地通过键合打线方式与mcm基板8连接,即,处理器的电源和地的pad焊盘13通过键合线14与mcm基板8连接,存储器和处理器之间的电源和地通过两侧的微凸点10进行连接,实现低速低密度信号传输,球栅阵列7bga设于mcm基板8下方;处理器和存储器的内部分别设置一个金属极板,两个相对的金属极板形成电容3,实现信号高速高密度无线传输。

53.可选地,所述第一模块1下设有凸点9,所述第一模块1的电源和地与所述mcm基板8还基于所述凸点9连接,所述第二模块2的电源和地与所述mcm基板8以键合打线方式连接。

54.具体地,图6是本发明提供的无线互连装置的结构示意图之五,如图6所示,本发明实施例还提供一种无线互连装置,以第一模块1为处理器,第二模块2为存储器为例,对该无线互连装置进行详细描述。处理器以倒装方式设置于mcm基板8上,即处理器的衬底层6在上,电路层4在下;处理器的电源和地通过处理器下方的凸点9与mcm基板8连接,即,处理器的电源和地通过凸点9与mcm基板8连接,存储器和处理器之间通过硅硅键合方式将晶圆键合在一起,存储器的电源和地的pad焊盘13通过键合线14与mcm基板8连接,实现低速低密度信号传输,处理器的电路层4和衬底层6的电容3通过第一硅通孔5(through silicon via,tsv)连接,球栅阵列7bga设于mcm基板8下方;处理器和存储器的内部分别设置一个金属极板,两个相对的金属极板形成电容3,实现信号高速高密度无线传输。

55.可选地,图7是本发明提供的无线互连装置的结构示意图之六,如图7所示,本发明实施例还提供一种无线互连装置,以第一模块1为处理器,第二模块2为存储器为例,对该无线互连装置进行详细描述。处理器以倒装方式设置于mcm基板8上,即处理器的衬底层6在上,电路层4在下;处理器的电源和地通过处理器下方的凸点9与mcm基板8连接,即,处理器的电源和地通过凸点9与mcm基板8连接,存储器和处理器之间通过daf膜12进行粘接,存储器的电源和地的pad焊盘13通过键合线14与mcm基板8连接,实现低速低密度信号传输,处理器的电路层4和衬底层6的电容3通过第一硅通孔5连接,球栅阵列7bga设于mcm基板8下方;处理器和存储器的内部分别设置一个金属极板,两个相对的金属极板形成电容3,实现信号高速高密度无线传输。

56.可选地,所述第一模块1下设有凸点9,所述第一模块1的电源和地与所述mcm基板8基于所述凸点9连接,所述第一模块1与所述第二模块2的电源和地基于所述金属键合垫11以混合键合方式连接。

57.可选地,图8是本发明提供的无线互连装置的结构示意图之七,如图8所示,本发明实施例还提供一种无线互连装置,以第一模块1为处理器,第二模块2为存储器为例,对该无线互连装置进行详细描述。处理器以倒装方式设置于mcm基板8上,即处理器的衬底层6在上,电路层4在下;处理器的电源和地通过处理器下方的凸点9与mcm基板8连接,即,处理器的电源和地通过凸点9与mcm基板8连接,存储器和处理器之间的电源和地通过金属键合垫11以混合键合方式进行连接,实现低速低密度信号传输,处理器的电路层4和衬底层6的电

容3通过第一硅通孔5连接,球栅阵列7bga设于mcm基板8下方;处理器和存储器的内部分别设置一个金属极板,两个相对的金属极板形成电容3,实现信号高速高密度无线传输。

58.可选地,所述第一模块1下设有凸点9,所述第一模块1的电源和地与所述mcm基板8基于所述凸点9连接,所述第一模块1与所述第二模块2的电源和地基于所述微凸点10连接。

59.可选地,图9是本发明提供的无线互连装置的结构示意图之八,如图9所示,本发明实施例还提供了一种无线互连装置,以第一模块1为处理器,第二模块2为存储器为例,对该无线互连装置进行详细描述。处理器以倒装方式设置于mcm基板8上,即处理器的衬底层6在上,电路层4在下;处理器的电源和地通过处理器下方的凸点9与mcm基板8连接,即,处理器的电源和地通过凸点9与mcm基板8连接,存储器的电源和地通过两侧的微凸点10进行连接,实现低速低密度信号传输,处理器的电路层4和衬底层6的电容3通过第一硅通孔5连接,球栅阵列7bga设于mcm基板8下方;处理器和存储器的内部分别设置一个金属极板,两个相对的金属极板形成电容3,实现信号高速高密度无线传输。

60.实际中,所述第一模块1包括电路层4和衬底层6,在所述第一模块1的电源和地与所述mcm基板基于所述凸点连接的情况下,所述第一模块1内设有至少两个第一硅通孔5,其中,所述第一硅通孔5用于连接所述电路层4和所述衬底层6中的所述电容3。

61.示例地,以第一模块1为处理器,第二模块2为存储器为例,处理器包括电路层4和衬底层6,为进一步实现信号传输,电路层4以编码电路为例,电路层4对信号进行编码,并通过第一硅通孔5传输至衬底层6中的电容3,由电容3传输至存储器,进行解码及后续处理。

62.本发明提供的一种无线互连装置,将第二模块2设置于第一模块1上方,且通过电容3无线互连提高第一模块1和第二模块2之间的互连数量,通过大幅度提升互连密度实现高速高密度数字信号传输,进一步提高信号传输可靠性和互连连接成品率;此外,还通过键合打线方式实现电源、地等低速低密度信号传输,进一步提升无线互连装置的可靠性。

63.此外,本发明还提供一种无线互连系统,包括:

64.如上述任一项所述的无线互连装置。

65.本发明提供的一种无线互连系统,通过无线互连装置,大幅度提高信号传输速率和信号传输带宽。

66.最后应说明的是:以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。