技术特征:

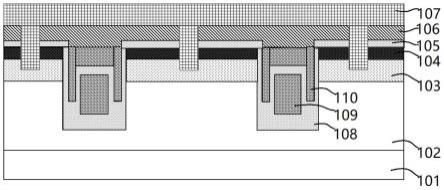

1.一种低导通电阻分离栅mosfet芯片,其特征在于,包括:衬底层,该衬底层采用浓掺杂的第一导电类型;外延层,该外延层位于衬底层表面,并采用轻掺杂的第一导电类型;阱区层,该阱区层形成于外延层中,并采用第二导电类型离子注入形成;源区层,该源区层形成外延层中,并位于阱区层外侧,源区采用第一导电类型离子注入形成;氧化层,该氧化层形成于外延层外壁,并位于源区外壁;层间绝缘介质层,该层间绝缘介质层形成于氧化层外壁;源极电极,该源极电极形成层间绝缘介质层外壁,并填充于源极接触孔中,源极接触孔贯穿层间绝缘介质层、第四氧化层及源区后延伸至阱区内;漏极电极,该漏极电极形成于衬底层外壁;隔离氧化层,该隔离氧化层填充于第一沟槽中,第一沟槽贯穿氧化层、源区层及阱区层后伸入外延层中;分离栅多晶硅,该分离栅多晶硅位于隔离氧化层中,其外壁与第一沟槽内壁之间留有距离;栅极多晶硅,该栅极多晶硅位于隔离氧化层中,并位于分离栅多晶硅上方,其边缘向下方弯折,并罩覆于分离栅多晶硅外部,使使分离栅多晶硅与栅极多晶硅之间的隔离氧化层形成倒扣碗型结构;栅极电极,该栅极电极从位于栅极多晶硅区域的栅极接触孔中引出。2.根据权利要求1所述的一种低导通电阻分离栅mosfet芯片的制造方法,其特征在于,包括:(1)选用浓掺杂第一导电类型衬底和轻掺杂第一导电类型外延材质的硅片作为材料片;(2)在外延表面依次淀积第一氧化层、第一氮化层及第二氧化层,在晶圆表面形成ono结构的硬掩模保护层;(3)通过光刻及刻蚀过程形成第一沟槽,第一沟槽贯穿第二氧化层、第一氮化层及第一氧化层后伸入外延中;(4)去除第二氧化层;(5)在第一沟槽底部和侧壁,以及第一氮化层表面淀积第三氧化层,作为分离栅的隔离氧化层;(6)在具有第三氧化层的第一沟槽内沉积多晶硅,作为分离栅多晶硅,并对其进行回刻及填充操作,以精确控制分离栅多晶硅的厚度;(7)在具有第三氧化层及分离栅多晶硅的第一沟槽内通过化学气相淀积方式淀积氧化层,使之与第三氧化层合拢,将第一沟槽的开口处闭合;(8)在第一沟槽内的第三氧化层中通过光刻及刻蚀过程形成第二沟槽,第二沟槽的底部低于非分离栅多晶硅顶部的高度,并高于分离栅多晶硅底部的高度;(9)在第二沟槽内淀积多晶硅,作为栅极多晶硅,其顶部高度略高于外延顶部的高度;(10)通过化学机械抛光工艺将第三氧化层、第一氮化层、第一氧化层全部去除,并使外延表面平坦化;

(11)在外延表面淀积第四氧化层,作为后续沟槽刻蚀的硬掩模保护层;(12)通过光刻及刻蚀过程形成第三沟槽,第三沟槽贯穿第四氧化层后伸入第一沟槽内的氧化层中,其侧壁与栅极多晶硅内壁重合,其底部与分离栅多晶硅之间留有距离,使分离栅多晶硅与栅极多晶硅之间形成倒扣碗型结构的隔离氧化层;(13)在第三沟槽内沉积多晶硅,使其与第二沟槽中的多晶硅顶部接合,共同构成倒扣碗型结构的栅极多晶硅;(14)在第一导电类型的外延中注入第二导电类型的阱区,在第二导电类型的阱区注入第一导电类型的源区;(15)在晶圆表面加工层间绝缘介质层;(16)在源区刻蚀源极接触孔,源极接触孔贯穿层间绝缘介质层、第四氧化层及源区后延伸至阱区内;(17)在绝缘介质层上加工源极金属,源极金属延伸至源极接触孔内,作为源极电极,在栅极多晶硅区域开栅极接触孔,作为栅极电极引出,对晶圆进行背面减薄及金属化,作为漏极电极。

技术总结

本发明提出一种低导通电阻分离栅MOSFET芯片及其制造方法,该MOSFET芯片的栅极多晶硅罩覆于分离栅多晶硅外部,使使分离栅多晶硅与栅极多晶硅之间的隔离氧化层形成倒扣碗型结构,该MOSFET芯片为了克服常规分离栅MOSFET结构中的缺陷,通过增加一次多晶硅淀积操作,改进了栅极多晶硅的形貌,使源极和栅极击穿发生时,击穿电场更加均匀,而且这种结构让分离栅多晶硅和栅极多晶硅的隔离氧化层从平面型变成了倒扣的碗型,降低了MOSFET的导通电阻,提升了分离栅MOSFET器件的稳定性,兼顾了MOSFET产品应用中高击穿电压需求和低导通电阻的需求,而且因为改善了导通电场的形貌,改善了通流区域,提高了分离栅MOSFET产品的可靠性,改善了漏电流,降低了密勒电容,提升了开关速度。提升了开关速度。提升了开关速度。

技术研发人员:吴昊 陆亚斌 王成

受保护的技术使用者:深圳傲威半导体有限公司

技术研发日:2022.07.28

技术公布日:2022/11/11

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。