3d封装结构及其制作方法

技术领域

1.本发明涉及半导体封装技术领域,具体地涉及一种3d封装结构及其制作方法。

背景技术:

2.3d晶圆级封装(下文以3d封装指代)指在不改变封装体尺寸的前提下,在同一个封装体内于垂直方向叠放两个以上芯片的封装技术,它起源于快闪存储器(nor/nand)及sdram的叠层封装。主要特点包括:多功能、高效能、大容量高密度、单位体积上的功能及应用成倍提升以及低成本等。

3.3d封装改善了芯片的许多性能,例如尺寸、重量、速度、产量及耗能等,但当前3d封装存在很多需要改进的结构和工艺。

技术实现要素:

4.本发明实施例的目的是提供一种3d封装结构,该3d封装结构可以改进现有3d封装的结构和工艺。

5.为了实现上述目的,本发明实施例提供一种3d封装结构,所述3d封装结构包括第一组芯片、第二组芯片、中介层结构以及外接点,其中,所述中介层结构包括线路板和侧壁支撑结构,所述线路板具有相对的第一表面和第二表面,且该第一表面和第二表面上均有连接点,所述连接点根据所述线路板内的连接线布置,所述侧壁支撑结构位于所述第一表面,所述第一组芯片通过所述连接点连接所述第一表面,所述第二组芯片通过所述连接点连接所述第二表面,所述外接点通过所述侧壁支撑结构内的连接线连接,所述第一组芯片的内部芯片之间、所述第二组芯片的内部芯片之间以及所述第一组芯片和所述第二组芯片之间根据所述中介层结构内的连接线进行通信。

6.可选的,所述侧壁支撑结构内的连接线为铜柱,所述侧壁支撑结构的高度和位置根据所述第一组芯片的高度和大小而被确定。

7.可选的,所述连接点为焊锡球,所述第一表面的连接点的熔点高于所述第二表面的连接点的熔点。

8.可选的,所述3d封装结构还包括基板,所述基板包括相对的第一基板表面和第二基板表面,所述基板的内部有连接线,所述外接点连接所述第一基板表面,所述第二基板表面根据所述基板的内部连接线布置连接点。

9.本发明实施例还提供一种3d封装结构的制作方法,所述3d封装结构的中介层结构包括线路板和侧壁支撑结构,所述线路板具有相对的第一表面和第二表面,且该第一表面和第二表面上均有连接点,所述连接点根据所述线路板内的连接线布置,所述侧壁支撑结构位于所述第一表面,所述3d封装结构的制作方法包括:将第一组芯片通过所述连接点连接在所述第一表面;将第二组芯片通过所述连接点连接在所述第二表面;以及通过所述侧壁支撑结构的连接线连接外接点,所述第一组芯片的内部芯片之间、所述第二组芯片的内部芯片之间以及所述第一组芯片和所述第二组芯片之间根据所述中介层结构内的连接线

进行通信。

10.可选的,所述将第一组芯片通过所述连接点连接在所述第一表面包括:在所述线路板的内部和所述第一表面布置连接线;通过无铅无卤锡膏焊球或铜柱加焊锡帽工艺,将所述第一组芯片通过所述连接点连接在所述第一表面;在所述第一组芯片和所述第一表面之间进行底部填充。

11.可选的,在所述将第二组芯片通过所述连接点连接在所述第二表面之前,所述3d封装结构的制作方法还包括:根据所述第一组芯片的高度和大小,制作所述侧壁支撑结构。

12.可选的,所述将第二组芯片通过所述连接点连接在所述第二表面包括:通过无铅合金焊球或无铅混合焊球工艺,将第二组芯片通过所述连接点连接在所述第二表面;在所述第二组芯片和所述第二表面之间进行底部填充或上模胶。

13.可选的,所述外接点为焊球,通过无铅锡膏焊球工艺,并通过所述侧壁支撑结构的连接线连接外接点。

14.可选的,所述3d封装结构还包括基板,所述基板包括相对的第一基板表面和第二基板表面,所述基板的内部有连接线,所述3d封装结构的制作方法还包括:通过所述外接点连接所述第一基板表面,所述第二基板表面根据所述基板的内部连接线布置连接点。

15.通过上述技术方案,本发明实施例的3d封装结构中,中介层结构(其线路板)具有双面连接点,使得第一组芯片和第二组芯片可以垂直连接,通过最短的距离传输信号,可以减少信号延迟和失真,从而提高带宽;多个芯片没有直接堆叠,散热不会互相干扰;中介层结构(其侧壁支撑结构)可以不限制第一组芯片的高度。

16.本发明实施例的其它特征和优点将在随后的具体实施方式部分予以详细说明。

附图说明

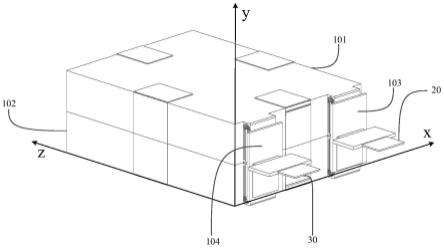

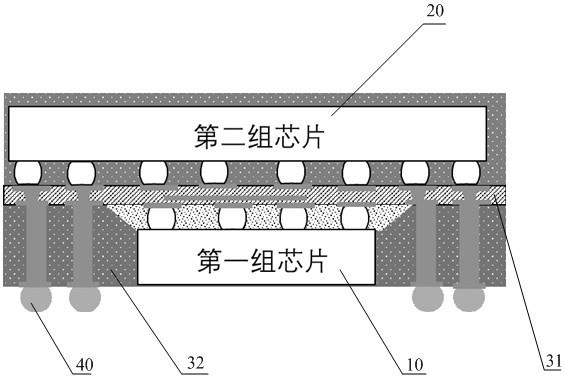

17.附图是用来提供对本发明实施例的进一步理解,并且构成说明书的一部分,与下面的具体实施方式一起用于解释本发明实施例,但并不构成对本发明实施例的限制。在附图中:图1是本发明实施例提供的3d封装结构的切面结构示意图;图2是本发明实施例提供的3d封装结构的俯视示意图;图3是示例3d封装结构的切面结构示意图;图4是示例3d封装结构的俯视示意图;图5是带基板的3d封装结构的示例切面结构示意图;图6是本发明实施例提供的3d封装结构的制作方法流程示意图;图7a-7b是示例制作第一组芯片的部分步骤示意图;图8a-8f是示例制作第二组芯片的部分步骤示意图;图9是示例制作外接点的步骤示意图。

18.附图标记说明10-第一组芯片;20-第二组芯片;40-外接点;31-线路板;32-侧壁支撑结构。

具体实施方式

19.以下结合附图对本发明实施例的具体实施方式进行详细说明。应当理解的是,此处所描述的具体实施方式仅用于说明和解释本发明实施例,并不用于限制本发明实施例。

20.图1是本发明实施例提供的3d封装结构的切面结构示意图;图2是本发明实施例提供的3d封装结构的俯视示意图。请参考图1,所述3d封装结构包括第一组芯片10、第二组芯片20、中介层结构以及外接点40。

21.其中,所述中介层结构包括线路板31和侧壁支撑结构32,所述线路板31具有相对的第一表面和第二表面,且该第一表面和第二表面上均有连接点,所述连接点根据所述线路板31内的连接线布置,所述侧壁支撑结构32位于所述第一表面。所述第一组芯片10通过所述连接点连接所述第一表面,所述第二组芯片20通过所述连接点连接所述第二表面,所述外接点40通过所述侧壁支撑结构32内的连接线连接。

22.当前3d封装存在很多需要改进的结构和工艺。例如,现有3d封装技术主要通过两个芯片相邻,边边连接,这种边边连接的布线很大程度上受到线宽和线距的限制,需要增加布线层数来增加布线的密度,需要比较长的导线连接。导线长度的增加,降低了传输带宽。本发明实施例通过芯片之间垂直方向的面互联,以减少芯片之间的距离,提高带宽,这种方式也不需要太多的布线。这种面面的互联也可以通过两个面来散热,散热效率高。

23.所述第一组芯片10可以包括一个或多个芯片,所述第二组芯片20也可以包括一个或多个芯片,所述第一组芯片10的内部芯片之间、所述第二组芯片20的内部芯片之间以及所述第一组芯片10和所述第二组芯片20之间根据所述中介层结构内的连接线进行通信。

24.中介层结构是芯片封装中,多芯片模块或电路板传递电信号的管道,中介层可以提供应力缓冲、信号再分布、供电等功能,也可以用于该封装结构与其他电路的连接,。中介层可以由硅、无机材料或有机材料制成,例如,硅中介层,充当多颗裸片和电路板之间的桥梁。

25.本发明实施例优选的所述侧壁支撑结构32内的连接线为铜柱,所述侧壁支撑结构32的高度和位置可以根据所述第一组芯片10的高度和大小而被确定。

26.以示例说明,在制作侧壁支撑结构32内的铜柱时,铜柱之间具有预设的间隔,防止外接点40之间的焊锡在融化过程中造成的短路。中介层结构的侧壁支撑结构32可以在第一表面上形成空腔结构,第一组芯片10被布置于该空腔结构内,与第一表面连接。本发明实施例通过中介层结构的侧壁支撑结构32来控制芯片高度,可以不限制第一组芯片10的高度。

27.本发明实施例优选的所述连接点为焊锡球,所述第一表面的连接点的熔点高于所述第二表面的连接点的熔点。

28.以示例说明,第一组芯片10、第二组芯片20可以使用高熔点的焊锡或铜柱加焊锡帽(copper pillar with solder cap ,c2)的100%金属化合物(inter-metallic compound ,imc),连接到线路板31的两表面。若连接点为焊锡球时,若在制作该3d封装结构的过程中,先制作连接第一组芯片10,再制作连接第二组芯片20,则第一表面的连接点的熔点高于所述第二表面的连接点的熔点,以防制作第二组芯片20时,影响第一组芯片10的连接;但若先制作连接第二组芯片20,再制作连接第一组芯片10,则第二表面的连接点的熔点高于所述第一表面的连接点的熔点,以防制作第一组芯片10时,影响第二组芯片20的连接。

29.图3、图4示出了第一组芯片10包括一个芯片(die1),第二组芯片20包括4个芯片的

堆叠。芯片2(die2)、芯片3(die3)、芯片4(die4)、芯片5(die4)可以通过较短的距离直接和芯片1连接,芯片1例如是cpu或gpu,芯片2、芯片3、芯片4、芯片5例如是存储芯片、外设南北桥的芯片、机器学习的人工智能芯片、电源管理的芯片、通讯的芯片等。

30.本发明实施例的3d封装结构中,中介层结构(其线路板31)具有双面连接点,使得第一组芯片10和第二组芯片20可以垂直连接,通过最短的距离传输信号,可以减少信号延迟和失真,从而提高带宽;多个芯片没有直接堆叠,散热不会互相干扰;中介层结构(其侧壁支撑结构32)可以不限制第一组芯片10的高度。

31.本发明实施例优选的所述3d封装结构还包括基板,所述基板包括相对的第一基板表面和第二基板表面,所述基板的内部有连接线,所述外接点连接所述第一基板表面,所述第二基板表面根据所述基板的内部连接线布置连接点。

32.请参考图5,以示例说明,基板(substrate)也可以为双面连接,第一基板表面连接图1所示3d封装结构的外接点,第二基板表面布置连接点,用于连接其他电路板结构。

33.图6是本发明实施例提供的3d封装结构的制作方法流程示意图,请参考图1和6,所述3d封装结构的中介层结构包括线路板31和侧壁支撑结构32,所述线路板31具有相对的第一表面和第二表面,且该第一表面和第二表面上均有连接点,所述连接点根据所述线路板31内的连接线布置,所述侧壁支撑结构32位于所述第一表面,所述3d封装结构的制作方法可以包括以下步骤:步骤s110:将第一组芯片10通过所述连接点连接在所述第一表面。

34.优选的,步骤s110可以包括:在所述线路板的内部和所述第一表面布置连接线;通过无铅无卤锡膏焊球或铜柱加焊锡帽工艺,将所述第一组芯片通过所述连接点连接在所述第一表面;在所述第一组芯片和所述第一表面之间进行底部填充。

35.请参考图7a,以先制作第一组芯片10为例,在所述线路板31的内部和所述第一表面布置连接线,若线路板31的第一表面不够平整,可以将所述线路板31通过所述第二表面固定在第一载板(例如,载板1)上。在第一表面,可以根据线路板31的内部连接线布置连接点,例如焊锡球。接着,通过高熔点(其温度可以根据中介层结构的材料进行选择,例如,可以为220℃-250℃)无铅无卤锡膏snsb焊球或铜柱加焊锡帽c2工艺,将所述第一组芯片10通过所述连接点连接在所述第一表面,连接点例如为焊锡球。请参考图7b,在所述第一组芯片10和所述第一表面之间进行底部填充。

36.本发明实施例优选的所述侧壁支撑结构32内的连接线(即,第一表面布置的连接线)为铜柱,所述侧壁支撑结构32的高度和位置可以根据所述第一组芯片10的高度和大小而被确定。

37.以示例说明,在制作侧壁支撑结构32内的铜柱时,铜柱之间具有预设的间隔,防止外接点40之间的焊锡在融化过程中造成的短路。中介层结构的侧壁支撑结构32可以在第一表面上形成空腔结构,第一组芯片10被布置于该空腔结构内,与第一表面连接。本发明实施例通过中介层结构的侧壁支撑结构32(即,铜柱的高度根据第一组芯片10的高度设置)来控制芯片高度,可以不限制第一组芯片10的高度。

38.步骤s120:将第二组芯片通过所述连接点连接在所述第二表面。

39.优选的,在步骤s120之前,所述3d封装结构的制作方法还包括:根据所述第一组芯片10的高度和大小,制作所述侧壁支撑结构32。

40.请参考图8a-8c,承接上述示例,根据所述第一组芯片10的高度和大小,制作所述侧壁支撑结构32,可以不限制第一组芯片10的高度。换载板,与上文类似地,若线路板31的第二表面不够平整,可以固定第二载板(例如,载板2),并去掉第一载板(例如,载板1)。在第二表面,可以根据线路板31的内部连接线布置连接点,例如焊锡球。

41.优选的,步骤s120包括:通过无铅合金焊球或无铅混合焊球工艺,将第二组芯片20通过所述连接点连接在所述第二表面;在所述第二组芯片20和所述第二表面之间进行底部填充或上模胶。

42.请参考图8d-8f,承接上述示例,通过无铅合金(snag)焊球或无铅混合(sac)焊球工艺,将第二组芯片20通过所述连接点连接在所述第二表面,连接点例如为焊锡球。在所述第二组芯片20和所述第二表面之间进行底部填充或上模胶。若固定过第二载板(例如,载板2),则去掉所述第二载板(例如,载板2)。其中,所述第一表面的连接点的熔点高于所述第二表面的连接点的熔点,以防制作第二组芯片20时,影响第一组芯片10的连接。

43.需要说明,本发明实施例的步骤s110和步骤s120可以更换先后顺序,即可以先制作连接第二组芯片20,再制作连接第一组芯片10,则第二表面的连接点的熔点高于所述第一表面的连接点的熔点,以防制作第一组芯片10时,影响第二组芯片20的连接。

44.步骤s130:通过所述侧壁支撑结构的连接线连接外接点。

45.所述第一组芯片10可以包括一个或多个芯片,所述第二组芯片30也可以包括一个或多个芯片,所述第一组芯片10的内部芯片之间、所述第二组芯片20的内部芯片之间以及所述第一组芯片10和所述第二组芯片20之间根据所述中介层结构内的连接线进行通信。

46.本发明实施例优选的所述外接点为焊球,通过无铅锡膏焊球工艺,并通过所述侧壁支撑结构32的连接线连接外接点40。

47.请参考图9,承接上述示例,通过低熔点(其温度可以根据中介层结构的材料和外接连接点的材料进行选择,例如,可以为160℃-220℃)无铅锡膏snbi焊球工艺,并通过所述侧壁支撑结构32的连接线连接焊球,侧壁支撑结构32的连接线例如为铜柱。

48.优选的,所述3d封装结构还包括基板,所述基板包括相对的第一基板表面和第二基板表面,所述基板的内部有连接线,所述3d封装结构的制作方法还包括:通过所述外接点40连接所述第一基板表面,所述第二基板表面根据所述基板的内部连接线布置连接点。

49.请参考图5,承接上述示例,基板(substrate)也可以为双面连接,第一基板表面连接外接点,第二基板表面布置连接点,该连接点例如为焊锡球。

50.据此,通过步骤s110-s130制作的3d封装结构中,中介层结构(其线路板31)具有双面连接点,使得第一组芯片10和第二组芯片20可以垂直连接,通过最短的距离传输信号,可以减少信号延迟和失真,从而提高带宽;多个芯片没有直接堆叠,散热不会互相干扰;中介层结构(其侧壁支撑结构32)可以不限制第一组芯片10的高度。

51.还需要说明的是,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、商品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、商品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括要素的过程、方法、商品或者设备中还存在另外的相同要素。

52.以上仅为本技术的实施例而已,并不用于限制本技术。对于本领域技术人员来说,

本技术可以有各种更改和变化。凡在本技术的精神和原理之内所作的任何修改、等同替换、改进等,均应包含在本技术的权利要求范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。