制造双孔装置的方法

1.背景

2.领域

3.本公开内容的多个实施方式涉及与固态纳米孔传感器一起使用的流通池和制造这种流通池的方法。

4.所涉及技术的描述

5.固态纳米孔传感器已经成为一种低成本、易于运输且快速处理的生物聚合物(如,dna或rna)定序技术。生物聚合物链的固态纳米孔定序通常包括使生物聚合物链通过一个或多个纳米级尺寸的开口(如,纳米孔)而移位,每个开口的直径约100nm。在单孔传感器中,纳米孔穿过分隔两个导电流体贮存器的膜片层而设置。将待定序的生物聚合物链(如,具有带负电荷特点的dna或rna链)引入两个导电流体贮存器的一个,并接着通过在两个导电流体贮存器间提供电位而使待定序的生物聚合物链通过纳米孔。随着生物聚合物链穿过纳米孔时,生物聚合物链的不同的单体单元(如,dna或rna链的蛋白质碱基)占据了不同百分比的纳米孔,因而改变了通过纳米孔中的离子电流流动。所得的电流信号模式可用于确定生物聚合物链中的单体单元的序列,诸如dna或rna链中的蛋白质的序列。通常,单孔传感器缺乏一种机制,该机制减慢了生物聚合物链通过纳米孔的移位速率,同时仍在两个贮存器之间提供足够的电位,以优化所得电流信号模式中的信噪比。

6.有益地,双孔传感器提供了一种通过在双孔传感器的两个纳米孔中共同捕获生物聚合物链的方式来控制生物聚合物链的移位速率的机制。典型的双孔传感器具有被壁并排分隔开的两个流体贮存器、公共流体腔室和将公共流体腔室与每个流体贮存器分隔开的膜片,膜片层具有穿过膜片层设置的两个纳米孔。待定序的生物聚合物链通过第二纳米孔从第一流体贮存器行进到公共腔室,并从公共腔室行进到第二流体贮存器。可期望地,两个纳米孔彼此足够靠近地配置以允许生物聚合物链的共同捕获。当生物聚合物链被两个纳米孔共同捕获时,竞争电位将施加在每个纳米孔上,以产生“拔河运动(tug-of-war)”,其中生物聚合物链的相对端部被沿相反的行进方向拉动。有利地,可调节在竞争电位之间的差异,以控制生物聚合物链穿过纳米孔的移位速率,因而控制电信号电流的信号图案或由此产生的图案的分辨率。

7.用于双孔传感器的已知制造方法一般规模较小,且因此与将双孔传感器推向公开市场所需的大批量制造、质量、可重复性和成本要求不兼容。此外,已知的制造方法一般将两个纳米孔之间的最小间距限制为约500nm,这因此限制了由两个纳米孔形成的双孔传感器对相对较短的生物聚合物链进行定序的能力。

8.因此,存在有改进的双孔传感器和双孔传感器形成方法的需求。

技术实现要素:

9.本公开内容的多个实施方式提供了固态、垂直对准的双孔传感器,该双孔传感器可用于生物分子定序,诸如dna、rna和/或其他生物聚合物,以及用于制造这些双孔传感器的方法。

10.在一个或多个实施方式中,提供了一种形成双孔传感器的方法,该方法包括以下步骤:形成膜堆叠物,其中膜堆叠物含有第一硅层、设置在第一硅层上的第一膜片层、设置在第一膜片层上的第二硅层和设置在第二硅层上的第二膜片层,和接着蚀刻膜堆叠物以产生在第一硅层中的第一贮存器、在第一膜片层中的第一纳米孔、在第二硅层中的第二贮存器、在第二膜片层中的第二纳米孔和信道,并且与第一贮存器和第二贮存器和第一纳米孔和第二纳米孔流体连通。方法还包括以下步骤:在第二膜片层和第一贮存器的内表面和第二贮存器的内表面和第一纳米孔的内表面和第二纳米孔的内表面上沉积保护性氧化物层,在设置在第二膜片层上的保护性氧化物层上沉积介电层并覆盖第二纳米孔,和形成金属接触件,金属接触件延伸穿过介电层、保护性氧化物层和第二膜片层,并且至少部分地延伸到第二硅层中。方法进一步包括以下步骤:蚀刻介电层的至少一部分,以在第二纳米孔上方形成阱,蚀刻第一硅层的至少一部分以露出沉积在第一贮存器的内表面上的保护性氧化物层的至少一部分,和蚀刻沉积在第一贮存器的内表面和第二贮存器的内表面和第一纳米孔的内表面和第二纳米孔的内表面上的保护性氧化物层。

11.在其他多个实施方式中,提供了一种形成双孔传感器的方法,该方法包括以下步骤:形成膜堆叠物,其中膜堆叠物含有第一硅层、设置在第一硅层上的第一膜片层、设置在第一膜片层上的第二硅层、设置在第二硅层上的第二膜片层、在第一硅层中的第一贮存器、在第一膜片层中的第一纳米孔、在第二硅层中的第二贮存器、在第二膜片层中的第二纳米孔和信道,并且与第一贮存器和第二贮存器和第一纳米孔和第二纳米孔流体连通。方法还包括以下步骤:在第二膜片层和第一贮存器的内表面和第二贮存器的内表面和第一纳米孔的内表面和第二纳米孔的内表面上沉积保护性氧化物层,在设置在第二膜片层上的保护性氧化物层上沉积介电层并覆盖第二纳米孔,形成金属接触件,金属接触件延伸穿过介电层、保护性氧化物层和第二膜片层,并且至少部分地延伸到第二硅层中。方法进一步包括以下步骤:蚀刻介电层的至少一部分以在第二纳米孔上方形成阱,蚀刻第一硅层的至少一部分以露出沉积在第一贮存器的内表面上的保护性氧化物层的至少一部分,蚀刻沉积在第一贮存器的内表面和第二贮存器的内表面和第一纳米孔的内表面和第二纳米孔的内表面上的保护性氧化物层,和至少在第一纳米孔的内表面和第二纳米孔的内表面上沉积间隔层。

12.在一些实施方式中,提供了一种双孔传感器,且双孔传感器含有膜堆叠物,膜堆叠物含有第一硅层、设置在第一硅层上的第一膜片层、设置在第一膜片层上的第二硅层、设置在第二硅层上的第二膜片层、在第一硅层中的第一贮存器、在第一膜片层中的第一纳米孔、在第二硅层中的第二贮存器、在第二膜片层中的第二纳米孔和信道,并且与第一贮存器和第二贮存器和第一纳米孔和第二纳米孔流体连通,其中第一纳米孔和第二纳米孔的每一个具有约1nm至约50nm的直径。双孔传感器还含有:阱,形成在设置在第二膜片层上方的介电层中,和金属接触件,延伸穿过介电层、第二膜片层并延伸到第二硅层中。

13.附图的简要说明

14.为了可详细地理解本公开内容的上述特征的方式,可通过参考多个实施方式来获得以上简要概述的本公开内容的更详细描述,其中一些实施方式显示在附图中。然而,应当注意,附图仅显示了本公开内容的多个典型实施方式,且因此不应被认为是对本公开内容范围的限制,因为本公开内容可允许其他多个等效的实施方式。

15.图1a-图1d图描绘了根据本文描述和讨论的一个或多个实施方式的在形成膜堆叠

物的不同阶段期间的工件的示意性截面图。

16.图2描绘了根据本文描述和讨论的一个或多个实施方式的含有膜堆叠物的工件的示意性截面图,膜堆叠物具有通过处理而形成的信道。

17.图3描绘了根据本文描述和讨论的一个或多个实施方式的含有膜堆叠物的工件的示意性截面图,膜堆叠物具有通过另一种处理而形成的信道。

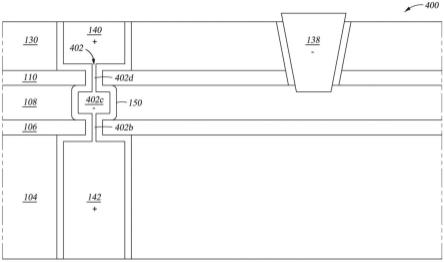

18.图4a描绘了根据本文描述和讨论的一个或多个实施方式的含有膜堆叠物的工件的示意性截面图,膜堆叠物具有通过另一种处理而形成的信道。

19.图4b描绘了根据本文描述和讨论的一个或多个实施方式的图4a中所描绘的工件的示意性顶视图。

20.图5描绘了根据本文描述和讨论的一个或多个实施方式的图4a中所描绘的工件在暴露于沉积处理之后的示意性截面图。

21.图6显示了根据本文描述和讨论的一个或多个实施方式的图5中所描绘的工件在暴露于另一种沉积处理之后的示意性截面图。

22.图7描绘了根据本文描述和讨论的一个或多个实施方式的图6中所描绘的工件在暴露于蚀刻处理之后的示意性截面图。

23.图8描绘了根据本文描述和讨论的一个或多个实施方式的图7中所描绘的工件在暴露于金属沉积处理之后的示意性截面图。

24.图9描绘了根据本文描述和讨论的一个或多个实施方式的图8中所描绘的工件在暴露于另一种蚀刻处理之后的示意性截面图。

25.图10a描绘了根据本文描述和讨论的一个或多个实施方式的图9中所描绘的工件在暴露于另一种蚀刻处理之后的示意性截面图。

26.图10b描绘了根据本文描述和讨论的一个或多个实施方式的在图10a中所描绘的工件的示意性顶视图。

27.图11描绘了根据本文描述和讨论的一个或多个实施方式的图10a中所描绘的工件在暴露于另一种蚀刻处理之后的示意性截面图。

28.图12a描绘了根据本文描述和讨论的一个或多个实施方式的在图11a中所描绘的工件在暴露于另一种蚀刻处理之后的示意性截面图。

29.图12b描绘了根据本文描述和讨论的一个或多个实施方式的图12a中所描绘的工件的示意性顶视图。

30.图13描绘了根据本文描述和讨论的一个或多个实施方式的图12a中所描绘的工件在暴露于沉积处理之后的示意性截面图。

31.图14a描绘了根据本文描述和讨论的一个或多个实施方式的图13中所描绘的工件在暴露于另一种蚀刻处理之后的示意性截面图。

32.图14b描绘了根据本文描述和讨论的一个或多个实施方式的图14a中所描绘的工件的示意性顶视图。

33.图15描绘了根据本文描述和讨论的一个或多个实施方式的双孔传感器的示意性截面图。

34.为了促进理解,在可能的情况下使用了相同的附图标记来表示各图式所共有的相同元素。可预期,一个或多个实施方式的元素和特征结构可有益地并入其他多个实施方式

中。

具体实施方式

35.本公开内容的多个实施方式提供了可用于生物聚合物定序的固态双孔传感器和固态双孔传感器的制造方法。一般,本文描述和讨论的双孔传感器通过电子制造技术形成,电子制造技术包括用于沉积、平板印刷和蚀刻的多种处理的组合。双孔传感器包括至少两个流体贮存器,该至少两个流体贮存器是一个设置在另一个上方,使得流体贮存器彼此垂直对准。

36.图1a-图1d描绘了根据一个或多个实施方式的在形成膜堆叠物112的不同阶段期间的工件100的示意性截面图。膜堆叠物112是形成如本文描述和讨论的双孔传感器的起始结构。如图1d所示,膜堆叠物112含有彼此叠置的两个或更多个硅层104、108和两个或更多个膜片层106、110。在一个或多个实施方式中,第一硅层104是基板或晶片(图1a),第一膜片层106沉积、生长或以其他方式设置在第一硅层104上(图1b),第二硅层108沉积、生长或以其他方式设置在第一膜片层106上(图1c),且第二膜片层110沉积、生长或以其他方式设置在第二硅层108上(图1d)。

37.硅层104、108的每一个可独立地是或包括一种或多种含硅材料。通常,硅层104、108的每一个可独立地是或包括非晶硅(α-si)或非晶硅的掺杂剂变体(dopant variations)。硅层104、108的每一个可独立地通过一种或多种沉积或涂布处理(诸如一种或气相沉积处理、一种或旋涂或其他技术)沉积或以其他方式形成。示例性的气相沉积处理可以是或包括化学气相沉积(cvd)或等离子体增强cvd(pe-cvd)。在一个或多个实例中,第一硅层104可具有与第二硅层108相同的厚度或更大的厚度。

38.在一个或多个实施方式中,硅层104可以是或包括基板,基板可以是可用于形成本文描述和讨论的双孔传感器的任何类型的基板。示例性基板可以是或包括半导体装置制造中通常使用的那些基板,诸如n型或p型掺杂的单晶硅晶片,或未掺杂的单晶硅形成的基板(如,本征(intrinsic)单晶硅晶片)。在一些实施方式中,硅层104是在硅层104上形成具有未掺杂单晶硅的外延层的掺杂或未掺杂的硅基板或晶片。在其他多个实施方式中,硅层104的特征在于硅、电绝缘材料(诸如蓝宝石或氧化硅)和硅的层状堆叠物,通常被称为绝缘体上硅(soi)基板或soi晶片。当用作硅层104时,与由掺杂的硅基板形成的传感器相比,未掺杂的硅基板、未掺杂的硅外延层和soi基板有利地减小了由未掺杂的硅基板、未掺杂的硅外延层和soi基板形成的双孔传感器中的不期望的寄生电容。

39.第一硅层104可具有约200μm、约250μm、约300μm、约400μm,或约500μm至约600μm、约650μm、约700μm、约750μm、约775μm、约800μm、约850μm、约900μm、约1,000μm、约1200μm、约1350μm、约1500μm、约1650μm、约1800μm或更大的厚度。例如,第一硅层104可具有约200μm至约1,800μm、约200μm至约1,650μm、约200μm至约1,500μm、约200μm至约1,000μm、约200μm至约850μm、约200μm至约800μm、约200μm至约750μm、约200μm至约700μm、约200μm至约600μm、约200μm至约500μm、约200μm至约350μm、约500μm至约1,800μm、约500μm至约1,650μm、约500μm至约1,500μm、约500μm至约1,000μm、约500μm至约850μm、约500μm至约800μm、约500μm至约775μm、约500μm至约750μm、约500μm至约700μm、约500μm至约600μm、约750μm至约1,800μm、约750μm至约1,650μm、约750μm至约1,500μm、约750μm至约1,000μm、约750μm至约850μm、

约750μm至约800μm,或约750μm至约775μm的厚度。在一个或多个实例中,第一硅层104是含硅晶片或含硅基板,并且具有约700μm至约900μm、约725μm至约825μm,或约750μm至约800μm,诸如约775μm的厚度。

40.第二硅层108可具有约10nm、约20nm、约30nm、约40nm,或约50nm至约60nm、约70nm、约80nm、约90nm、约100nm、约110nm、约120nm、约150nm或约200nm的厚度。例如、第二硅层108可具有约10nm至约200nm、约20nm至约200nm、约20nm至约150nm、约20nm至约120nm、约20nm至约100nm、约20nm至约80nm、约20nm至约50nm、约40nm至约200nm、约40nm至约150nm、约40nm至约120nm、约40nm至约100nm、约40nm至约80nm、约40nm至约50nm、约60nm至约200nm、约60nm至约150nm、约60nm至约120nm、约60nm至约100nm,或约60nm至约80nm的厚度。

41.膜片层106、110的每一个可独立地是或包括一种或多种氮化硅材料。通常,膜片层106、110的每一个可独立地是或包括氮化硅(si3n4或sin)或氮化硅的掺杂剂变体。膜片层106、110的每一个可独立地通过一种或多种气相沉积处理而沉积或以其他方式形成。示例性气相沉积处理可以是或包括cvd、pe-cvd、脉冲cvd、原子层沉积(ald)、等离子体增强ald(pe-ald)、物理气相沉积(pvd)、其他溅射技术或上述处理的任意组合。在一个或多个实例中,第一膜片层106和第二膜片层110具有彼此相同的厚度或基本相同的厚度。

42.第一膜片层106和第二膜片层110的每一个可独立地具有约0.1nm、约0.2nm、约0.3nm、约0.4nm、约0.5nm、约0.6nm、约0.7nm、约0.8nm、约0.9nm、约1nm、约1.1nm、约1.2nm、约1.3nm、约1.4nm、约1.5nm、约1.6nm、约1.8nm、约2nm、约2.5nm、约3nm、约5nm、约7nm、约9nm、约10nm、约15nm、约20nm、约25nm、约30nm、约35nm、约40nm或更大的厚度。例如,第一膜片层106和第二膜片层110的每一个可独立地具有约0.1nm至约40nm、约0.1nm至约30nm、约0.1nm至约20nm、约0.1nm至约10nm、约0.1nm至约8nm、约0.1nm至约6nm、约0.1nm至约5nm、约0.1nm至约3nm、约0.1nm至约2nm、约0.1nm至约1.5约0.1nm至约1.2nm、约0.1nm至约1nm、约0.1nm至约0.8nm、约0.1nm至约0.6nm、约0.1nm至约0.5nm、约0.1nm至约0.3nm、约0.5nm至约40nm、约0.5nm至约30nm、约0.5nm至约20nm、约0.5nm至约10nm、约0.5nm至约8nm、约0.5nm至约6nm、约0.5nm至约5nm、约0.5nm至约3nm、约0.5nm至约2nm、约0.5nm至约1.5nm、约0.5nm至约1.2nm、约0.5nm至约1nm、约0.5nm至约0.8nm、约0.5nm至约0.6nm、约0.8nm至约40nm、约0.8nm至约30nm、约0.8nm至约20nm、约0.8nm至约10nm、约0.8nm至约8nm、约0.8nm至约6nm、约0.8nm至nm约5nm、约0.8nm至约3nm、约0.8nm至约2nm、约0.8nm至约1.5nm、约0.8nm至约1.2nm,或约0.8nm至约1nm的厚度。

43.图2描绘了根据本文描述和讨论的一个或多个实施方式的工件200的示意性截面图,工件200含有膜堆叠物112,膜堆叠物112中形成有信道202。工件200可由图1d中的工件100形成。将膜堆叠物112暴露于平板印刷处理,接着进行蚀刻处理,以产生信道202,信道202延伸穿过第二膜片层110、第二硅层108、第一膜片层106,并进入第一硅层104中。在一些实例中,蚀刻处理是反应离子蚀刻(rie)处理。

44.信道202可具有锥形的几何形状,使得穿过第二膜片层110的信道202的直径大于穿过第一膜片层106的信道202的直径。第一膜片层106中形成的孔的直径和第二膜片层110中形成的孔的直径的每一个通过控制锥形的角度和/或信道202的长度来独立确定。这些孔的直径可以是约1nm、约2nm,或约5nm至约10nm、约20nm、约30nm、约35nm、约40nm,或约50nm。这些孔的直径可在下文进一步描述和讨论的后续处理阶段中减小。

45.图3描绘了根据本文描述和讨论的一个或多个实施方式的含有膜堆叠物112的工件300的示意性截面图,膜片堆叠物112中形成有信道302。工件300可从图1b中的工件100开始以两个或更多个阶段形成或以其他方式生产。例如,信道302可通过平板印刷-蚀刻-平板印刷-蚀刻(lele)处理形成。从工件100开始(如图1b所描绘),将第一膜片层106和第一硅层104暴露于平板印刷处理中,接着进行蚀刻处理以产生信道302的下部。此后,将第二硅层108沉积在第一膜片层106上,并将第二膜片层110沉积在第二硅层108上。随后,将第二膜片层110和第二硅层108暴露于平板印刷处理,接着进行蚀刻处理以产生信道302的上部(如图3所描绘)。信道302延伸穿过第二膜片层110、第二硅层108、第一膜片层106,并进入第一硅层104中。

46.信道302可具有直壁(straight-walled)的几何形状,使得穿过第二膜片层110的信道302与穿过第一膜片层106的信道302具有相同的直径。在第一膜片层106中形成的孔的直径和形成在第二膜片层110中的孔的直径的每一个通过每个蚀刻处理独立地确定。这些孔的直径可以是约1nm、约2nm,或约5nm至约10nm、约20nm、约30nm、约35nm、约40nm,或约50nm。这些孔的直径可在下文进一步描述和讨论的后续处理阶段中减小。

47.根据本文描述和讨论的一个或多个实施方式,图4a描绘了含有膜堆叠物112的工件100的示意性截面图,膜堆叠物112中形成有信道402,且图4b描绘了图4a中所描绘的工件100的示意性顶视图。信道402从第二膜片层110上的开口401延伸,穿过第二膜片层110、第二硅层108、第一膜片层106,并进入第一硅层104中。蚀刻膜堆叠物112以产生第一硅层104中的第一贮存器402a、第一膜片层106中的第一纳米孔402b、第二硅层108中的第二贮存器402c和第二膜片层110中的第二纳米孔402d。信道402含有第一贮存器402a和第二贮存器402c和第一纳米孔402b和第二纳米孔402d,因此,信道402与第一贮存器402a和第二贮存器402c和第一纳米孔402b和第二纳米孔402d流体连通。

48.如图1d所描绘的,将工件100暴露于蚀刻处理(诸如等离子体蚀刻处理),以产生包括第一贮存器402a和第二贮存器402c和第一纳米孔402b和第二纳米孔402d的信道402。在一个或多个实施方式中,可通过使用基于等离子体的干法蚀刻处理来移除材料以形成信道402。例如,第二膜片层110、第二硅层108、第一膜片层106和第一硅层104可顺序地暴露于含有一种或多种蚀刻剂的活化的自由基物种(诸如一种或多种含卤素的气体的径向物种(radial species))的等离子体。示例性蚀刻剂可以是或包括氟、氟化氢、氯、氯化氢或它们的任何组合的一种或多种。可用于将材料移除至信道402的示例性系统是可从加州圣塔克拉拉市的应用材料公司取得的etch系统以及其他制造商的合适系统。

49.在一个或多个实施方式中,第一贮存器402a和第二贮存器402c可具有彼此相同的直径d1,并且第一纳米孔402b和第二纳米孔402d可具有彼此相同的直径d2。在未显示的其他多个实施方式中,第一贮存器402a和第二贮存器402c可彼此独立地具有不同的直径,并且第一纳米孔402b和第二纳米孔402d可彼此独立地具有不同的直径。第一纳米孔402b和第二纳米孔402d的直径可在下文进一步描述和讨论的后续处理阶段中减小。

50.第一贮存器402a和第二贮存器402c的每一个可独立地具有约200nm、约300nm、约400nm,或约450nm至约500nm、约550nm、约600nm、约700nm、约800nm,或约1000nm的直径d1。例如,第一贮存器402a和第二贮存器402c的每一个可独立地具有约200nm至约800nm、约

200nm至约600nm、约200nm至约500nm、约200nm至约400nm、约400nm至约800nm、约400nm至约600nm、约400nm至约500nm、约450nm至约500nm、约500nm至约800nm、约500nm至约600nm、或约500nm至约550nm的直径d1。

51.第一纳米孔402b和第二纳米孔402d的每一个可独立地具有约1nm、约2nm,或约5nm至约10nm、约20nm、约30nm、约35nm、约40nm、约50nm、约60nm,或约80nm的直径d2。例如,第一纳米孔402b和第二纳米孔402d的每一个可独立地具有约1nm至约80nm、约1nm至约60nm、约1nm至约50nm、约1nm至约40nm、约1nm至约35nm、约1nm至约30nm、约1nm至约25nm、约1nm至约20nm、约1nm至约10nm、约10nm至约80nm、约10nm至约60nm、约10nm至约50nm、约10nm至约40nm、约10nm至约35nm、约10nm至约30nm、约10nm至约25nm、约10nm至约20nm、约10nm至约15nm、约20nm至约80nm、约20nm至约60nm、约20nm至约50nm、约20nm至约40nm、约20nm至约35nm、约20nm至约30nm,或约20nm至约25nm的直径d2。

52.图5描绘了工件100的示意性截面图,工件100含有被沉积或以其他方式形成在第二膜片层110的上表面以及信道402的内表面(诸如第一贮存器402a的内表面和第二贮存器402c的内表面和第一纳米孔402b的内表面和第二纳米孔402d的内表面)上的保护性氧化物层120。保护性氧化物层120是用于由信道402形成的内壁的保护性涂层。保护性氧化物层120可以是或包括一种或多种介电材料(诸如氧化硅)、一种或多种金属氧化物、一种或多种金属硅酸盐、它们的掺杂剂或它们的任何组合。例如,保护性氧化物层120可以是或包括氧化硅、氧化铝、氧化钇、氧化铪、氧化锆、氧化钛、氧化钽、硅酸铝、硅酸钇、硅酸铪、硅酸锆、硅酸钛、硅酸钽,或它们的任何组合。

53.在一些实施方式中,图4a中所描绘的工件100暴露于一种或多种沉积处理(诸如气相沉积处理),以形成或以其他方式沉积保护性氧化物层120。用于形成或以其他方式沉积保护性氧化物层120的示例性气相沉积处理可以是或包括ald、pe-ald、cvd、pe-cvd、脉冲cvd或它们的任意组合。在一个或多个实例中,通过ald处理或pe-ald处理而沉积保护性氧化物层120。保护性氧化物层120具有约0.5nm、约1nm、约2nm、约3nm、约4nm,或约5nm至约8nm、约10nm、约12nm、约15nm、约20nm、约25nm、约30nm、约35nm、约40nm、约50nm,或约60nm的厚度。例如,保护性氧化物层120具有约1nm至约60nm、约1nm至约50nm、约1nm至约40nm、约1nm至约35nm、约1nm至约30nm、约1nm至约25nm、约1nm至约20nm、约1nm至约15nm、约1nm至约12nm、约1nm至约10nm、约1nm至约8nm、约1nm至约5nm、约1nm至约3nm、约5nm至约60nm、约5nm至约50nm、约5nm至约40nm、约5nm至约35nm、约5nm至约30nm、约5nm至约25nm、约5nm至约20nm、约5nm至约15nm、约5nm至约12nm、约5nm至约10nm、约5nm约8nm、约10nm至约60nm、约10nm至约50nm、约10nm至约40nm、约10nm至约35nm、约10nm至约30nm、约10nm至约25nm、约10nm至约20nm、约10nm至约15nm,或约10nm至约12nm的厚度。

54.图6描绘了根据本文描述和讨论的一个或多个实施方式的工件100的示意性截面图,工件100含有设置在保护性氧化物层120上并覆盖第二纳米孔402d的介电层130。介电层130可包括旋涂介电材料,或者可通过气相沉积处理沉积或以其他方式形成。

55.在一个或多个实施方式中,介电层130可以是、含有和/或由正硅酸四乙酯(teos)氧化物、一种或多种硅烷氧化物、一种或多种聚酰亚胺、一种或多种其他介电材料,或它们的任何组合所制成。在一个或多个实例中,介电层130可以是或包括一种或多种光可界定(photo-definable)材料,诸如聚酰亚胺。例如,光可界定的材料可由光敏的聚合物前驱物

制成或包括光敏的聚合物前驱物,例如光敏的聚酰亚胺前驱物或苯并环丁烯(bcb)。在一个或多个随后的处理中,期望的图案直接暴露在其上。

56.介电层130的厚度是约0.5μm、约1μm、约1.5μm,或约2μm至约2.5μm、约3μm、约4μm,或约5μm。例如,介电层130的厚度是约0.5μm至约5μm、约0.5μm至约4μm、约0.5μm至约3μm、约0.5μm至约2μm、约0.5μm至约1μm、约1μm至约5μm、约1μm至约4μm、约1μm至约3μm、约1μm至约2μm、约1.5μm至约5μm、约1.5μm至约4μm、约1.5μm至约3μm,或约1.5μm至约2μm。

57.图7描绘了根据本文描述和讨论的一个或多个实施方式的具有接触孔136的工件100的示意性截面图。接触孔136从第二硅层108内延伸并且完全延伸穿过第二膜片层110、保护性氧化物层120和介电层130。例如,接触孔136可被蚀刻或以其他方式穿过介电层130、保护性氧化物层120、第二膜片层110和至少部分地进入第二硅层108中。在一些实施方式中,接触孔136使用平板印刷-蚀刻处理顺序而被蚀刻穿过介电层130的固化的聚合物以及第二硅层108的其他材料并完全穿过第二膜片层110、保护性氧化物层120。在一个或多个实施方式中,接触孔136通过反应离子蚀刻(rie)形成。接触孔136的直径可以是约1μm、约10μm、约50μm,或约100μm至约250μm、约500μm、约800μm,或约1000μm。

58.图8描绘了根据本文描述和讨论的一个或多个实施方式的图7中所描绘的工件100在暴露于一种或多种金属沉积处理之后的示意性截面图。工件100具有金属接触件138,金属接触件138含有设置在接触孔136内并且遍及(across)介电层130的上表面的至少一部分的一种或多种导电材料。金属接触件138延伸穿过介电层130、保护层氧化物层120和第二膜片层110,和至少部分地进入第二硅层108中。在一个或多个方面中,金属接触件138平行于或基本平行于信道402延伸,如图8所示。

59.设置在接触孔136中形成金属接触件138的一种或多种导电材料可以是或包括铜、铝、钨、钛、铬、钴、它们的合金或它们的任何组合。可通过包括电镀或电沉积、无电沉积、cvd、pe-cvd、pvd或它们的任何组合的一种或多种沉积处理来沉积、镀覆(plate)或以其他方式形成金属接触件138。

60.图9描绘了根据本文描述和讨论的一个或多个实施方式的图8中所描绘的工件100在暴露于一种或多种蚀刻处理之后的示意性截面图。设置在介电层130的上表面上的金属接触件138是在金属接触件沉积处理之后剩余的导电材料的残留层。含有金属接触件138的导电材料的这个残留层可被蚀刻、抛光和/或以其他方式移除到介电层130。在一些实例中,含有金属接触件138的导电材料的残留层被暴露于湿法蚀刻处理、化学机械处理(cmp)、电cmp(e-cmp)或它们的任意组合。

61.根据本文描述和讨论的一个或多个实施方式,图10a描绘了图9中所描绘的工件100在暴露于另一种蚀刻处理之后的示意性截面图,且图10b描绘了在图10a中所描绘的工件100的示意性顶视图。介电层130的至少一部分被蚀刻或以其他方式移除,以形成在第二纳米孔402d处设置于信道402上方的阱140,如图10a所描绘。在一些实例中,利用干法蚀刻处理蚀刻介电层130的一部分以形成阱140。例如,通过用rie处理或其他等离子体蚀刻处理移除介电层130的一部分来形成阱140。

62.阱140的直径可以是约0.5μm、约1μm、约5μm、约10μm,或约15μm至约20μm、约30μm、约50μm、约80μm,或约100μm。例如,阱140的直径可以是约0.5μm至约100μm、约0.5μm至约90μm、约0.5μm至约80μm、约0.5μm至约65μm、约0.5μm至约50μm、约0.5μm至约30μm、约0.5μm至约

20μm、约0.5μm至约10μm、约0.5μm至约5μm、约0.5μm至约1μm、约10μm至约100μm、约10μm至约90μm、约10μm至约80μm、约10μm至约65μm、约10μm至约50μm、约10μm至约30μm、约10μm至约20μm,或约10μm至约15μm的深度。

63.阱140可具有约200nm、约300nm、约400nm,或约450nm至约500nm、约550nm、约600nm、约700nm、约800nm、约1,000、约2,000nm、约3,000nm或约5,000nm的深度。例如、阱140可具有约200nm至约5,000nm、约200nm至约2,000nm、约200nm至约1,000nm、约200nm至约800nm、约200nm至约600nm、约200nm至约500nm、约200nm至约400nm、约400nm至约5,000nm、约400nm至约2,000nm、约400nm至约1,000nm、约400nm至约800nm、约400nm至约600nm、约400nm至约500nm、约450nm至约500nm、约500nm至约800nm、约500nm至约600nm,或约500nm至约550nm的深度。

64.图11描绘了根据本文描述和讨论的一个或多个实施方式的图10a中所描绘的工件100在暴露于另一种蚀刻处理之后的示意性截面图。蚀刻或以其他方式移除第一硅层104的至少一部分以形成阱142,并露出沉积在第一贮存器402a的内表面上的保护性氧化物层120的至少一部分。在一个或多个实例中,如图11所描绘,通过湿法蚀刻处理蚀刻掉第一硅层104的一部分,以露出保护性氧化物层120的一部分。

65.在湿法蚀刻处理中使用的合适的湿法蚀刻剂的示例是水溶液,可以是或包括氢氧化四甲基铵(tmah)、氢氧化铵(nh4oh)、肼(n2h4)、乙二胺和邻苯二酚(epd)、氢氧化钠(naoh)、氢氧化钾(koh)、氢氧化锂(lioh)或它们的任意组合的一种或多种。在一个或多个实例中,通过在约70℃至约90℃的温度下将工件100暴露于氢氧化水溶液(约30wt%至约35wt%的koh)约10小时至约14小时来移除第一硅层104的一部分。

66.根据本文描述和讨论的一个或多个实施方式,图12a描绘了图11a中所描绘的工件100在暴露于另一种蚀刻处理之后的示意性截面图,并且图12b描绘了图12a中所描绘的工件100的示意性顶视图。如图12a和图12b所描绘,实质上所有的保护性氧化物层120中的全部可被蚀刻或以其他方式移除,以及且设置在阱140中的介电层130的下部可被蚀刻或以其他方式移除。具体地,可通过一个或多个蚀刻处理来蚀刻或以其他方式移除最初沉积在第一贮存器402a和第二贮存器402c的内表面上并且最初沉积在第一纳米孔402b和第二纳米孔402d的内表面上的保护性氧化物层120。

67.在一个或多个实例中,通过一种或多种湿法蚀刻处理来蚀刻设置在阱140中的保护性氧化物层120和介电层130的下部。湿法蚀刻处理包括将保护性氧化物层120和介电层130的下部暴露于一种或多种蚀刻溶液。蚀刻溶液可以是或包括稀释的氢氟酸(dhf)水溶液和/或缓冲的hf水溶液,诸如hf和氟化铵(nh4f)的水溶液。将工件100暴露于蚀刻溶液少于10分钟,诸如约1分钟至约8分钟。

68.第一纳米孔402b和第二纳米孔402d的每一个可独立地具有约0.5nm、约1nm、约1.25nm、约1.5nm、约1.75nm,或约2nm至约2.25nm、约2.5nm、约2.75nm、约3nm、约4nm、约5nm、约6nm、约8nm、约10nm、约15nm、约20nm、约30nm、约40nm,或约50nm的直径d3。例如,第一纳米孔402b和第二纳米孔402d的每一个可独立地具有约0.5nm至约50nm、约0.5nm至约30nm、约0.5nm至约20nm、约0.5nm至约15nm、约0.5nm至约10nm、约0.5nm至约8nm、约0.5nm至约5nm、约0.5nm至约4nm、约0.5nm至约3nm、约0.5nm至约2.5nm、0.5nm至约2.25nm、约0.5nm至约2nm、约0.5nm至约1.75nm、约0.5nm至约1.5nm、约0.5nm至约1.25nm、约0.5nm至约1nm、约

0.5nm至约0.75nm、约1nm至约50nm、约1nm至约40nm、约1nm至约30nm、约1nm至约20nm、约1nm至约15nm、约1nm至约10nm、约1nm至约8nm、约1nm至约5nm、约1nm至约4nm、约1nm至约3nm、约1nm至约2.5nm、约1nm至约2.25nm、约1nm至约2nm、约1nm至约1.75nm、约1nm至约1.5nm、约1nm至约1.25nm、约1.5nm至约50nm、约1.5nm至约30nm、约1.5nm至约20nm、约1.5nm至约10nm、约1.5nm至约8nm、约1.5nm至约5nm、约1.5nm至约4nm、约1.5nm至约3nm、约1.5nm至约2.5nm、约1.5nm至约2.25nm、约1.5nm至约2nm,或约1.5nm至约1.75nm的直径d3。

69.在一个或多个实例中,第一膜片层106和第二膜片层110可独立地具有约0.1nm至约40nm的厚度,并且第一纳米孔402b和第二纳米孔402d可独立地具有约0.5纳米至约50纳米的直径d3。在其他多个实例中,第一膜片层106和第二膜片层110可独立地具有约0.5nm至约20nm的厚度,并且第一纳米孔402b和第二纳米孔402d可独立地具有约1nm至约3.5nm的直径d3。在一些实例中,第一膜片层106和第二膜片层110可独立地具有约0.7nm至约10nm的厚度,并且第一纳米孔402b和第二纳米孔402d可独立地具有约1.5nm至约2.5nm的直径d3。在其他多个实例中,第一膜片层106和第二膜片层110可独立地具有约0.8nm至约1.2nm的厚度,并且第一纳米孔402b和第二纳米孔402d可独立地具有约1.75nm至约2.25nm的直径d3。

70.在一个或多个实施方式中,图12a和图12b所描绘的工件100是如本文描述和讨论的垂直对准的双孔传感器,并且可在dna、rna、生物聚合物和/或其他生物分子的定序期间使用。在第一纳米孔402b或第二纳米孔402d的任何一个不具有期望的直径d3的情况下,可沉积额外的材料以进一步减小第一纳米孔402b或第二纳米孔402d的直径,以便具有期望的直径d3。为了具有期望的直径d3,调整第一纳米孔402b或第二纳米孔402d的直径的其他细节在下文进一步描述和讨论,并在图13、图14a和图14b中描绘。

71.图13描绘了根据本文描述和讨论的一个或多个实施方式的图12a中所描绘的工件100在暴露于沉积处理之后的示意性截面图。在蚀刻或以其他方式移除沉积在第一贮存器402a和第二贮存器402c的内表面和第一纳米孔402b和第二纳米孔402d的内表面上的保护性氧化物层120之后,方法还可包括至少在第一纳米孔402b和第二纳米孔402d的内表面上沉积间隔层150,以减小第一纳米孔402b与第二纳米孔402d之间的直径。

72.例如,将工件100暴露于一个或多个气相沉积处理,以在工件150的大部分(若不是全部)暴露的表面上沉积间隔层150。间隔层150设置在第一硅层104、第一膜片层106、第二硅层108、第二膜片层110、保护性氧化物层120、介电层130和金属接触件138的暴露表面上。间隔层150设置在第一纳米孔402b和第二纳米孔402d的内表面(如,第一膜片层106和第二膜片层110的内表面)和第二贮存器402c的内表面(如,第二硅层108的内表面)。间隔层150可在第一纳米孔402b和/或第二纳米孔402d处或附近部分地或完全覆盖或以其他方式阻挡信道402。信道402在图13中显示为在第一纳米孔402b附近被完全覆盖。在其他多个实例中,间隔层150被保形地或实质上保形地沉积在下方的表面上,使得信道402在阱140、142之间保持完全开放。

73.间隔层150包括一种或多种材料,诸如氧化硅、氮化硅、氮氧化硅、它们的掺杂剂变体或它们的任意组合。间隔层150可通过任何气相沉积处理来沉积,诸如ald处理、pe-ald处理、cvd处理、pe-cvd处理、脉冲cvd处理或它们的任意组合。在一个或多个实例中,间隔层150可通过ald处理或pe-ald处理而沉积。

74.间隔层150可沉积为用于调节第一纳米孔402b或第二纳米孔402d的直径所需的任

何厚度,以便具有期望的直径d3。这样,间隔层150可具有约0.1nm、约0.2nm、约0.3nm、约0.4nm、约0.5nm、约0.6nm、约0.7nm、约0.8nm、约0.9nm、约1nm、约1.1nm、约1.2nm、约1.3nm、约1.4nm、约1.5nm、约1.6nm、约1.8nm、约2nm、约2.5nm、约3nm、约5nm、约7nm、约9nm、约10nm、约15nm、约20nm或更大的厚度。例如,间隔层150可具有约0.1nm至约20nm、约0.1nm至约15nm、约0.1nm至约10nm、约0.1nm至约8nm、约0.1nm至约6nm、约0.1nm至约5nm、约0.1nm至约3nm、约0.1nm至约2nm、约0.1nm至约1.5nm、约0.1nm至约1.2nm、约0.1nm至约1nm、约0.1nm至约0.8nm、约0.1nm至约0.6nm、约0.1nm至约0.5nm、约0.1nm至约0.3nm、约0.5nm至约20nm、约0.5nm至约15nm、约0.5nm至约10nm、约0.5nm至约8nm、约0.5nm至约6nm、约0.5nm至约5nm、约0.5nm至约3nm、约0.5nm至约2nm、约0.5-nm约1.5nm、约0.5nm至约1.2nm、约0.5nm至约1nm、约0.5nm至约0.8nm、约0.5nm至约0.6nm、约0.8nm至约20nm、约0.8nm至约15nm、约0.8nm至约10nm、约0.8nm至约8nm、约0.8nm至约6nm、约0.8nm至约5nm、约0.8nm至约3nm、约0.8nm至约2nm、约0.8nm至约1.5nm、约0.8nm至约1.2nm,或约0.8nm至约1nm的厚度。

75.根据本文描述和讨论的一个或多个实施方式,图14a描绘了图13中所描绘的工件100在暴露于一种或多种蚀刻处理以移除间隔层150的一部分之后的示意性截面图,并且图14b描绘了工件100的示意性顶视图。

76.方法包括从介电层130的上表面和侧表面和金属接触件138的上表面蚀刻间隔层150的至少一部分。方法还包括蚀刻间隔层的至少一部分,以产生延伸穿过第一纳米孔402b和第二纳米孔402d的信道402的期望直径。这样,第一纳米孔402b和第二纳米孔402d具有期望的直径d3。方法进一步包括从第一膜片106的下表面、第二膜片110的上表面或两个表面蚀刻间隔层150的至少一部分。若信道402由于间隔层150而被覆盖或具有阻挡,则蚀刻处理移除足够的间隔层150以减轻或完全移除阻挡并释放信道402。

77.通过从第一膜片106的下表面和/或第二膜片110的上表面蚀刻或以其他方式移除间隔层150的至少一部分,有效地使整个膜片厚度变薄。例如,整个下部膜片可包括第一膜片106和设置在第一膜片106的下表面上的间隔层150。通过在蚀刻处理期间使第一膜片106的下表面上的间隔层150变薄,将整个下部膜片的厚度减小到期望的厚度。类似地,整个上部膜片可包括第二膜片110和设置在第二膜片110的上表面上的间隔层150。通过在蚀刻处理期间使第二膜片110的上表面上的间隔层150变薄,将整个上部膜片的厚度减小到期望的厚度。

78.在一个或多个实例中,通过一种或多种湿法蚀刻处理来蚀刻间隔层150。湿法蚀刻处理包括将间隔层150暴露于一种或多种蚀刻溶液中。蚀刻溶液可以是或包括稀释的氢氟酸(dhf)水溶液和/或缓冲的hf水溶液,诸如hf和氟化铵(nh4f)的水溶液。

79.图15描绘了根据本文描述和讨论的一个或多个实施方式的双孔传感器400的示意性截面图。双孔传感器400经由用作阳极的金属接触件138在第二贮存器402c处中间接地。中间接地通过第二贮存器402c形成两个电路-经由第二纳米孔402d和阱140的上部电路和经由第一纳米孔402b和阱142的下部电路。每个阱140、142独立地用作阴极。

80.有益地,本文描述和讨论的方法允许大批量制造,以及垂直对准的双孔传感器的质量、可重复性和制造成本的改进。此外,与传统的水平双孔系统相比,本文描述和讨论的垂直对准的双孔传感器提供dna、rna和/或其他生物聚合物的生物分子定序的更好的控制。

81.本公开内容的多个实施方式进一步涉及以下段落1-24的任一个或多个:

82.1.一种形成双孔传感器的方法,包含以下步骤:形成膜堆叠物,其中膜堆叠物包含:第一硅层、设置在第一硅层上的第一膜片层、设置在第一膜片层上的第二硅层和设置在第二硅层上的第二膜片层;蚀刻膜堆叠物以产生:在第一硅层中的第一贮存器、在第一膜片层中的第一纳米孔、在第二硅层中的第二贮存器、在第二膜片层中的第二纳米孔和信道并且与第一贮存器和第二贮存器和第一纳米孔和第二纳米孔流体连通;在第二膜片层和第一贮存器的内表面和第二贮存器的内表面和第一纳米孔的内表面和第二纳米孔的内表面上沉积保护性氧化物层;在设置在第二膜片层上的保护性氧化物层上沉积介电层并覆盖第二纳米孔;形成金属接触件,金属接触件延伸穿过介电层、保护性氧化物层和第二膜片层,并且至少部分地延伸到第二硅层中;蚀刻介电层的至少一部分,以在第二纳米孔上方形成阱;蚀刻第一硅层的至少一部分以露出沉积在第一贮存器的内表面上的保护性氧化物层的至少一部分;和蚀刻沉积在第一贮存器的内表面和第二贮存器的内表面和第一纳米孔的内表面和第二纳米孔的内表面上的保护性氧化物层。

83.2.根据段落1所述的方法,其中保护性氧化物层包含氧化硅、金属氧化物、金属硅酸盐或它们的任意组合。

84.3.根据段落1或2所述的方法,其中通过原子层沉积来沉积保护性氧化物层。

85.4.根据段落1-3任一段落所述的方法,其中第一纳米孔和第二纳米孔的每一个独立地具有约0.5nm至约50nm的直径。

86.5.根据段落1-4任一段落所述的方法,其中第一纳米孔和第二纳米孔的每一个独立地具有约1nm至约5nm的直径。

87.6.根据段落1-5任一段落所述的方法,其中介电层包含正硅酸四乙酯氧化物、硅烷氧化物、聚酰亚胺或它们的任意组合。

88.7.根据段落1-6任一段落所述的方法,其中介电层是约1μm至约5μm。

89.8.根据段落1-7任一段落所述的方法,其中介电层是约1.5μm至约3μm。

90.9.根据段落1-8任一段落所述的方法,其中形成金属接触件的步骤进一步包含以下步骤:蚀刻穿过介电层、保护性氧化物层和第二膜片层并且部分地进入第二硅层的接触孔;和将导电材料沉积到接触孔中。

91.10.根据段落9所述的方法,其中形成金属接触件的步骤进一步包含以下步骤:从介电层蚀刻导电材料的任何残留层。

92.11.根据段落1-10任一段落所述的方法,其中金属接触件平行于或实质上平行于信道延伸。

93.12.根据段落1-11任一段落所述的方法,其中利用干法蚀刻处理来蚀刻介电层的一部分以在第二纳米孔上方形成阱,且其中利用湿法蚀刻处理来蚀刻第一硅层的一部分,以露出沉积在第一贮存器的内表面上的保护性氧化物层的一部分。

94.13.根据段落1-12任一段落所述的方法,其中通过湿法蚀刻处理来蚀刻保护性氧化物层。

95.14.根据段落1-13任一段落所述的方法,其中在蚀刻沉积在第一贮存器的内表面和第二贮存器的内表面和第一纳米孔的内表面和第二纳米孔的内表面上的保护性氧化物层之后,进一步包含以下步骤:至少在第一纳米孔和第二纳米孔的内表面上沉积间隔层。

96.15.根据段落14所述的方法,其中间隔层包含氧化硅、氮化硅、氧氮化硅或它们的

任意组合。

97.16.根据段落14所述的方法,其中间隔层通过原子层沉积来沉积。

98.17.根据段落14所述的方法,进一步包含以下步骤:蚀刻间隔层的至少一部分,以产生延伸穿过第一纳米孔和第二纳米孔的信道的期望直径。

99.18.根据段落14所述的方法,进一步包含以下步骤:从第一膜片的下表面或第二膜片的上表面蚀刻间隔层的至少一部分。

100.19.一种形成双孔传感器的方法,包含以下步骤:形成膜堆叠物,其中膜堆叠物包含:第一硅层、设置在第一硅层上的第一膜片层、设置在第一膜片层上的第二硅层、设置在第二硅层上的第二膜片层、在第一硅层中的第一贮存器、在第一膜片层中的第一纳米孔、在第二硅层中的第二贮存器、在第二膜片层中的第二纳米孔和信道并且与第一贮存器和第二贮存器和第一纳米孔和第二纳米孔流体连通;在第二膜片层和第一贮存器的内表面和第二贮存器的内表面和第一纳米孔的内表面和第二纳米孔的内表面上沉积保护性氧化物层;在设置在第二膜片层上的保护性氧化物层上沉积介电层并覆盖第二纳米孔;形成金属接触件,金属接触件延伸穿过介电层、保护性氧化物层和第二膜片层,并且至少部分地延伸到第二硅层中;蚀刻介电层的至少一部分以在第二纳米孔上方形成阱;蚀刻第一硅层的至少一部分以露出沉积在第一贮存器的内表面上的保护性氧化物层的至少一部分;蚀刻沉积在第一贮存器的内表面和第二贮存器的内表面和第一纳米孔的内表面和第二纳米孔的内表面上的保护性氧化物层;和至少在第一纳米孔的内表面和第二纳米孔的内表面上沉积间隔层。

101.20.根据段落19所述的方法,其中间隔层包括氧化硅、氮化硅、氮氧化硅或它们的任意组合,并且其中间隔层通过原子层沉积来沉积。

102.21.根据段落19或20所述的方法,进一步包含以下步骤:从第一膜片的下表面或第二膜片的上表面蚀刻间隔层的至少一部分。

103.22.根据段落19-21任一段落所述的方法,其中第一纳米孔和第二纳米孔的每一个独立地具有约1nm至约50nm的直径。

104.23.一种根据段落1-22任一段落的方法制备的双孔传感器。

105.24.一种双孔传感器,包含:膜堆叠物,其中膜堆叠物包含:第一硅层、设置在第一硅层上的第一膜片层、设置在第一膜片层上的第二硅层、设置在第二硅层上的第二膜片层、在第一硅层中的第一贮存器、在第一膜片层中的第一纳米孔、在第二硅层中的第二贮存器、在第二膜片层中的第二纳米孔和信道并且与第一贮存器和第二贮存器和第一纳米孔和第二纳米孔流体连通,其中第一纳米孔和第二纳米孔的每一个具有约1nm至约50nm的直径;阱,形成在设置在第二膜片层上方的介电层中;和金属接触件,延伸穿过介电层、第二膜片层并延伸到第二硅层中。

106.尽管前述内容针对本公开内容的多个实施方式,但是在不背离本公开内容的基本范围情况下,可设计多个其他和进一步的实施方式,并且多个实施方式的范围由以下的申请专利范围决定。本文描述的所有文件均通过引用的方式并入本文,包括不与此份文本矛盾的的任何优先权文件和/或测试程序。从前面的一般描述和多个特定实施方式中显而易见的是,尽管已经显示和描述了本公开内容的形式,但是可在不背离本公开内容的精神和范围的情况下作出各种修改。因此,无意于限制本公开内容。同样地,出于美国法律的目的,

术语“包含(comprising)”被认为与术语“包括(including)”同义。同样地,每当在组合物、元素或元素的群组的前面加上过渡短语“包含”时,应理解为具有过渡短语“实质上由

…

组成”、“由

…

组成”、“选自由以下的群组所组成”或“是”在组合物、一种或多种元素的叙述之前的相同组成物或元素的群组,且反之亦然。

107.已经使用一组数值上限和一组数值下限描述了某些实施方式和特征结构。应当理解,除非另外指出,否则涵盖包括任何两个值的组合(如,任何较低的值与任何较高的值的组合、任何两个较低的值的组合和/或任何两个较高的值的组合)的范围。某些下限、上限和范围出现在下文的一项或多项权利要求中。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。