adc-dac组合的片上自测试系统及方法

技术领域

1.本技术涉及电子电路领域,特别是涉及模数转换器技术领域。

背景技术:

2.数模转换器(dac

‑ꢀ

digital-to-analog converter)与模数转换器(adc

‑ꢀ

analog-to-digital converter)是应用在众多领域的芯片的关键部分,如手机基带处理芯片,数字电视处理芯片,雷达及通信芯片等,如何在芯片量产测试中高质量,低成本的测试adc与dac是业界一直不断研究的课题。

3.数模转换器(dac-digital-to-analog converter)是将数字编码(通常为2进制)转换为模拟信号(例如电流,电压等),由于半导体技术的迅猛发展,集成于soc(system-on-a-chip)芯片内部的dac的分辨率与采样速率在持续提升。目前世界上最先进的高精度dac的分辨率可达24bits,采样率为192ksps;而最先进的高速dac的分辨率可达14位,采样速率可达12gsps。数模转换器制造出来后,需要对其进行功能与性能测试,判断是好片还是坏片。在保证测试精度基础上的测试成本是其整个数模转换芯片成本的重要组成部分。通常,数模转换器会在昂贵的混合信号自动测试机台上进行测试(mixed-signal automated test equipment),如图1所示。

4.模数转换器(adc-analog-to-digital converte)将模拟信号转换为数字信号,是应用在众多领域的芯片的关键部分。随着cmos技术的发展,adc已越来越先进,目前世界最先进的高精度adc的分辨率可达32bits,采样率为4ksps;而最先进的高速adc的采样速率可达10.4gsps,分辨率可达12bits。adc制造出来后,需要对其进行测试,判断是好片还是坏片。测试的成本是其整个生产成本的重要组成部分。通常,adc会在昂贵的混合信号自动测试机台上进行测试(mixed-signal automated test equipment),如图2所示。

5.这种传统的dac/adc混合信号自动测试机台进行测试的方式存在如下缺点:第一,测试成本昂贵。由于模数转换器(adc)/数模转换器(dac)自身性能不断提升,与之对应的混合信号自动化测试设备(ate)的性能指标也要不断提升,每隔一段时间就需要更新换代,给测试厂带来固定投资的压力,这边成本也转嫁到芯片的测试成本中,导致整个芯片成本的提升。

6.第二,测试精度受限。由于模数转换器(adc)/数模转换器(dac)自身性能不断提升,与之配合的测试电路板上的走线阻抗匹配设计,通孔信号完整性设计,低噪声电源完整性设计等都是很大的挑战,越来越难以满足,而且对应的测试电路板成本也非常高昂。

7.对于在片上同时集成模数转换器(adc)与数模转换器(dac)的芯片,主流量产测试方案如图3所示。随着技术的进步,被测模数转换器(adc)/数模转换器(dac)组合的性能指标越来越高,而成本控制的同意要求也越来越大。

8.因此如何降低模数转换器(adc)与数模转换器(dac)的测试成本,提高模数转换器(adc)与数模转换器(dac)的测试精度已成为本领域技术人员亟待解决的技术难题。

技术实现要素:

9.鉴于以上所述现有技术的缺点,本技术提供了adc-dac组合的片上自测试系统及方法,用于解决现有技术中模数转换器和数模转换器测试成本高,测试精度低的技术问题。

10.为实现上述目的及其他相关目的,本技术提供一种adc-dac组合的片上自测试系统,配置于包含模数转换器和数模转换器的片上系统芯片中,所述adc-dac组合的片上自测试系统包括:测试控制器,斜坡信号发生器,数字向量生成器,比较器,计数器,码存储器以及测试控制模块;在对所述模数转换器进行测试时,所述测试控制器控制所述斜坡信号发生器发出斜坡信号,所述测试控制模块控制所述斜坡信号进入所述模数转换器,所述模数转换器将所述斜坡信号转换为数字信号,并由所述测试控制模块控制所述数字信号输入到所述码存储器进行存储,所述测试控制器对所述码存储器中存储的数值序列进行计算分析;在对所述数模转换器进行测试时,所述测试控制器控制所述数字向量生成器生成数字向量,所述测试控制模块控制所述数字向量进入所述数模转换器,所述数模转换器将所述数字向量转换为模拟信号,并由所述测试控制模块控制所述模拟信号输入到所述比较器的负端,同时所述测试控制器控制所述斜坡信号发生器发出斜坡信号,所述测试控制模块控制所述斜坡信号输入到所述比较器的正端;所述测试控制器根据所述比较器的比较结果控制所述数字向量生成器生成的数字向量递增,所述计数器根据所述比较器的比较结果将时钟计数输入到所述码存储器进行存储,直至所述数模转换器的输入码值范围被遍历,所述测试控制器对所述码存储器中存储的数值序列进行计算分析。

11.于本技术一实施例中,所述adc-dac组合的片上自测试系统还包括:低通滤波器,与所述斜坡信号发生器相连,用于过滤所述斜坡信号。

12.于本技术一实施例中,所述测试控制模块包括:第一选择开关,控制所述斜坡信号发生器输出的斜坡信号进入所述模数转换器或进入所述比较器;第二选择开关,与所述模数转换器的输出端相连,控制所述模数转换器的输出信号进入所述码存储器;第三选择开关,与所述数模转换器的输出端相连,控制所述数模转换器的输出信号进入所述比较器;第一多路复用器,与所述第一选择开关和所述模数转换器相连,控制是否选通所述斜坡信号进入所述模数转换器;第二多路复用器,与所述数字向量生成器和所述数模转换器相连,控制是否选通所述数字向量进入所述数模转换器;第三多路复用器,与所述第二选择开关和所述计数器相连,控制所述模数转换器的输出信号进入所述码存储器或所述计数器的时钟计数进入所述码存储器。

13.于本技术一实施例中,在对所述模数转换器进行测试时:所述第一选择开关控制所述斜坡信号发生器输出的斜坡信号进入所述第一多路复用器,所述第一多路复用器控制选通所述斜坡信号进入所述模数转换器,所述第二选择开关控制所述模数转换器的输出信号进入所述第三多路复用器,所述第三多路复用器控制选通所述模数转换器的输出信号进入所述码存储器;所述第二多路复用器选通所述数模转换器的片外工作输入信号进入所述数模转换器,所述第三选择开关控制所述数模转换器的信号输出到片上系统芯片外部。

14.于本技术一实施例中,在对所述数模转换器进行测试时:所述第一选择开关控制所述斜坡信号发生器输出的斜坡信号进入所述比较器,所述第二多路复用器选通所述数字向量生成器输出的数字向量进入所述数模转换器,所述第三选择开关控制所述数模转换器的输出信号进入所述比较器,所述第三多路复用器控制选通所述计数器的时钟计数进入所

述码存储器;所述第一多路复用器选通所述模数转换器的片外工作输入信号进入所述模数转换器,所述第二选择开关控制所述模数转换器的信号输出到片上系统芯片外部。

15.于本技术一实施例中,在对所述模数转换器进行测试时,所述码存储器中存储的数字信号的序列码长度为所述模数转换器位数精度的8倍以上。

16.于本技术一实施例中,在对所述数模转换器进行测试时,在所述比较器的比较结果为所述斜坡信号大于所述数模转换器的输出信号时,所述测试控制器控制所述数字向量生成器生成的数字向量增加1,所述计数器将时钟计数输入到所述码存储器进行存储,重复上述过程,直至所述数模转换器的输入码值范围被遍历。

17.于本技术一实施例中,所述斜坡信号的范围需大于所述数模转换器的模拟信号输出范围。

18.于本技术一实施例中,所述测试控制器包括:特性值获取模块,用于对对所述码存储器中存储的信号进行计算,生成特性值;测试对比模块,用于将生成的所述特性值与预设指标值进行对比,确认所述特性值是否符合所述预设指标值;测试结果输出模块,用于在所述特性值符合所述预设指标值时输出指示所述模数转换器或所述数模转换器正常的第一测试结果信号,在所述特性值不符合所述预设指标值时输出指示所述模数转换器或所述数模转换器异常的第二测试结果信号。

19.为实现上述目的及其他相关目的,本技术提供一种adc-dac组合的片上自测试方法,应用于包含模数转换器和数模转换器的片上系统芯片中,所述方法包括:在对所述模数转换器进行测试时,控制一斜坡信号进入模数转换器,由所述模数转换器将所述斜坡信号转换为数字信号,对所述数字信号进行测试; 在对所述数模转换器进行测试时,控制一数字向量进入所述数模转换器,由所述数模转换器将所述数字向量转换为模拟信号,将所述模拟信号输入到一比较器的负端,同时控制一斜坡信号进入所述比较器的正端,并根据所述比较器的比较结果控制所述数字向量递增,通过一计数器根据所述比较器的比较结果进行时钟计数,并对所述计数器输出的时钟计数进行测试。

20.如上所述,本技术的adc-dac组合的片上自测试系统及方法,具有以下有益效果:1、本技术的adc-dac组合的片上自测试系统设置于片上系统芯片内,无需外加测试设备,即可实现对模数转换器和数模转换器进行测试,无需昂贵专用的自动化测试设备,有效节省测试成本,提高测试精度。

21.2、本技术可灵活重复配置,可快速进行测试,可以做特性分析,有效提高adc-dac组合的片上自测试系统的重复使用率和使用范围。

22.3、本技术可以在整个片上系统芯片生命周期进行性能监控,自动输出测试结果,测试结构简单、方便。

附图说明

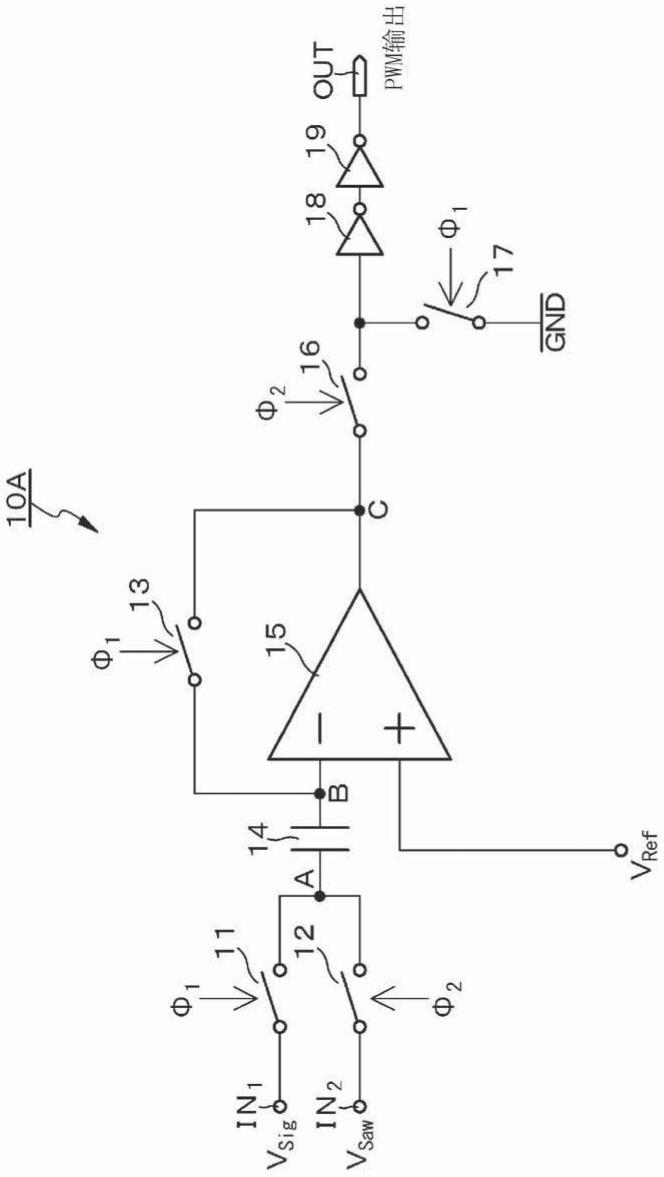

23.图1显示为现有技术中测试dac的原理结构框图。

24.图2显示为现有技术中测试adc的原理结构框图。

25.图3显示为现有技术中dac/adc混合测试的原理结构框图。

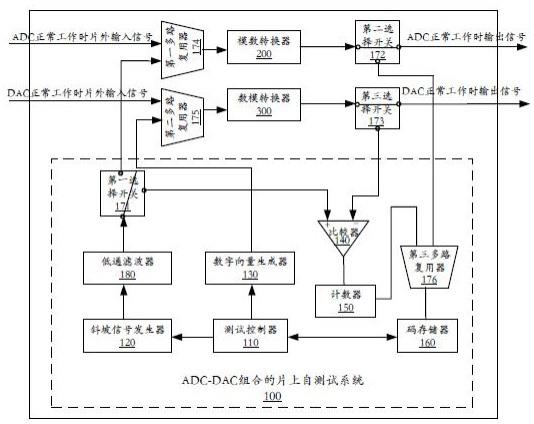

26.图4显示为本技术一实施例的adc-dac组合的片上自测试系统的原理结构框图。

27.图5显示为本技术一实施例的adc-dac组合的片上自测试系统测试adc时的原理结

构框图。

28.图6显示为本技术一实施例的adc-dac组合的片上自测试系统测试dac时的原理结构框图。

29.图7显示为本技术一实施例的adc-dac组合的片上自测试系统测试dac时的dac测试信号分析图。

30.图8显示为本技术一实施例的adc-dac组合的片上自测试方法的流程示意图。

31.元件标号说明:100-adc-dac组合的片上自测试系统;110-测试控制器;120-斜坡信号发生器;130-数字向量生成器;140-比较器;150-计数器;160

ꢀ‑

码存储器;171-第一选择开关;172-第二选择开关;173-第三选择开关;174-第一多路复用器;175-第二多路复用器;176-第三多路复用器;180-低通滤波器;200-模数转换器;300-数模转换器;s100~s200 步骤。

具体实施方式

32.以下通过特定的具体实例说明本技术的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本技术的其他优点与功效。本技术还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本技术的精神下进行各种修饰或改变。需说明的是,在不冲突的情况下,以下实施例及实施例中的特征可以相互组合。

33.需要说明的是,以下实施例中所提供的图示仅以示意方式说明本技术的基本构想,遂图式中仅显示与本技术中有关的组件而非按照实际实施时的组件数目,形状及尺寸绘制,其实际实施时各组件的型态,数量及比例可为一种随意的改变,且其组件布局型态也可能更为复杂。

34.本实施例提供一种adc-dac组合的片上自测试系统及方法,用于解决现有技术中模数转换器和数模转换器测试成本高,测试精度低的技术问题。

35.以下将详细阐述本实施例的adc-dac组合的片上自测试系统及方法的原理及实施方式,使本领域技术人员不需要创造性劳动即可理解本发明的adc-dac组合的片上自测试

系统及方法。

36.图4显示为本实施例中的adc-dac组合的片上自测试系统100的原理结构框图。如图4所示,所述adc-dac组合的片上自测试系统100配置于包含模数转换器200和数模转换器300的片上系统芯片中,所述adc-dac组合的片上自测试系统100包括:测试控制器110,斜坡信号发生器120,数字向量生成器130,比较器140,计数器150,码存储器160以及测试控制模块。

37.以下结合图5至图7对本实施例的adc-dac组合的片上自测试系统100进行详细说明。

38.本实施例中,所述adc-dac组合的片上自测试系统100配置于包含模数转换器200和数模转换器300的片上系统芯片中,无需昂贵复杂的混合信号测试的自动化测试设备(ate),节省测试成本。

39.图4显示为本实施例的adc-dac组合的片上自测试系统100的原理结构框图。

40.如图4所示,于本实施例中,所述测试控制器110分别与斜坡信号发生器120和数字向量生成器130相连,控制斜坡信号发生器120和数字向量生成器130输出信号,并与码存储器160相连,从所述码存储器160中读取信号进行测试分析。

41.于本实施例中,所述adc-dac组合的片上自测试系统100还包括:低通滤波器180,与所述斜坡信号发生器120相连,用于过滤所述斜坡信号,过滤的所述斜坡信号经选择进入模数转换器200或比较器140。

42.其中,所述斜坡信号发生器120用于向模数转换器200输入斜坡信号,模数转化器的输出信号经选择后输入所述码存储器160,以供所述测试控制器110对模数转换器200进行测试分析。

43.其中,所述数字向量生成器130用于向数模转换器300输入数字向量,数模转换器300输出信号经选择后输入比较器140,经计数器150计数后进入码存储器160,以供所述测试控制器110对数模转换器300进行测试分析。

44.于本实施例中,所述测试控制模块包括:第一选择开关171,第二选择开关172,第三选择开关173,第一多路复用器174,第二多路复用器175以及第三多路复用器176。

45.具体地,所述第一选择开关171控制所述斜坡信号发生器120输出的斜坡信号进入所述模数转换器200或进入所述比较器140。所述第一选择开关171一端与所述低通滤波器180相连,其中,在未进行测试时,所述第一选择开关171的另一端指向空挡,在对所述模数转换器200进行测试时,所述第一选择开关171的另一端与所述第一多路复用器174导通,在对所述数模转换器300进行测试时,所述第一选择开关171的另一端与所述比较器140导通。

46.所述第二选择开关172与所述模数转换器200的输出端相连,控制所述模数转换器200的输出信号进入所述码存储器160。其中,所述第二选择开关172的一端与所述模数转换器200的输出端相连,其中,在未对所述模数转换器200进行测试时,所述第二选择开关172的另一端与片外adc正常工作时输出的输出端相连,在对所述模数转换器200进行测试时,所述第二选择开关172的另一端与所述第三多路复用器176导通。

47.所述第三选择开关173与所述数模转换器300的输出端相连,控制所述数模转换器300的输出信号进入所述比较器140。所述第三选择开关173的一端与所述数模转换器300的输出端相连,其中,在未对所述数模转换器300进行测试时,所述第三选择开关173的另一端

与片外dac正常工作时输出的输出端相连,在对所述数模转换器300进行测试时,所述第三选择开关173的另一端与所述比较器140导通。

48.所述第一多路复用器174与所述第一选择开关171和所述模数转换器200相连,控制是否选通所述斜坡信号进入所述模数转换器200。其中,所述第一多路复用器174的一路输入端连接片外adc正常工作时输入的输入端,一路输入端连接所述第一选择开关171的输出端,所述第一多路复用器174的输出端与所述模数转换器200相连。其中,在未对所述模数转换器200进行测试时,所述第一多路复用器174输入端选择与片外adc正常工作时输入的输入端相连,在对所述模数转换器200进行测试时,所述第一多路复用器174输入端选择与所述第一选择开关171导通。也就是说,需要对模数转换器200模块进行测试时,控制第一多路复用器174选通所述斜坡信号发生器120输出的信号至所述模数转换器200模块,不需要对模数转换器200模块进行测试时,控制所述第一多路复用器174选通片外的模数信号(adc)输入到模数转换器200模块中。

49.所述第二多路复用器175与所述数字向量生成器130和所述数模转换器300相连,控制是否选通所述数字向量进入所述数模转换器300。其中,所述第二多路复用器175的一路输入端连接片外dac正常工作时输入的输入端,一路输入端连接所述数字向量生成器130的输出端,所述第二多路复用器175的输出端与所述数模转换器300相连。其中,在未对所述数模转换器300进行测试时,所述第二多路复用器175输入端选择与片外dac正常工作时输入的输入端相连,在对所述数模转换器300进行测试时,所述第二多路复用器175输入端选择与所述数字向量生成器130导通。也就是说,需要对数模转换器300模块进行测试时,控制第二多路复用器175选通所述数字向量生成器130输出的信号至所述数模转换器300模块,不需要对数模转换器300模块进行测试时,控制所述第二多路复用器175选通片外的数模信号(dac)输入到数模转换器300模块中。

50.所述第三多路复用器176与所述第二选择开关172和所述计数器150相连,控制所述模数转换器200的输出信号进入所述码存储器160或所述计数器150的时钟计数进入所述码存储器160。其中,所述第三多路复用器176的一路输入端连接所述第二选择开关172的输出端,一路输入端连接所述计数器150的输出端,所述第三多路复用器176的输出端与码存储器160的输入端相连。

51.所述比较器140的正端与所述第三选择开关173相连,接收输入数模转换器300的输出信号,所述比较器140的负端与所述第一选择开关171相连,接收所述斜坡信号发生器120经过过来的斜坡信号。所述比较器140的输出端与所述计数器150的输入端相连,所述计数器150的输出端与所述第三多路复用器176的一路输入端相连。

52.本实施例中,所述模数转换器200的测试原理为:在对所述模数转换器200进行测试时,所述测试控制器110控制所述斜坡信号发生器120发出预设幅度范围和速率的斜坡信号,所述测试控制模块控制所述斜坡信号进入所述模数转换器200,所述模数转换器200将所述斜坡信号转换为数字信号,并由所述测试控制模块控制所述数字信号输入到所述码存储器160进行存储,所述测试控制器110对所述码存储器160中存储的数值序列进行计算分析。

53.图5显示为本实施例的adc-dac组合的片上自测试系统100测试adc时的原理结构框图。具体地,于本实施例中,在对所述模数转换器200进行测试时:

如图5所示,所述第一选择开关171控制所述斜坡信号发生器120输出的斜坡信号进入所述第一多路复用器174,所述第一多路复用器174控制选通所述斜坡信号进入所述模数转换器200,所述第二选择开关172控制所述模数转换器200的输出信号进入所述第三多路复用器176,所述第三多路复用器176控制选通所述模数转换器200的输出信号进入所述码存储器160;所述第二多路复用器175选通所述数模转换器300的片外工作输入信号进入所述数模转换器300,所述第三选择开关173控制所述数模转换器300的信号输出到片上系统芯片外部。

54.本实施例中,adc测试流程如下:1)测试控制器110控制斜坡信号发生器120发出指定幅度范围与速率的斜坡信号;2)斜坡信号通过低通滤波器180,滤去高频噪声,然后到达被测的模数转换器200的输入端;3)模数转换器200将模拟输入的斜坡信号转换为数字信号,然后被码存储器160抓取存储;4)测试控制器110读取码存储器160中存储的数据序列,计算得出inl与dnl数值,并与预置的规格值进行比对,判断是否合格。

55.于本实施例中,所述adc-dac组合的片上自测试系统100可以在整个芯片生命周期进行性能监控,只需下一道指令控制斜坡信号发生器120,无需外加任何设备,简化了测试流程。同时,本实施例的adc-dac组合的片上自测试系统100只有一路对外输出:测试结果信号,表示测试通过(pass)/不通过(fail),最简化外部测试设备需求。

56.其中,于本实施例中,在对所述模数转换器200进行测试时,所述码存储器160中存储的数字信号的序列码长度为所述模数转换器200位数精度的8倍以上。

57.adc静态非线性测试为大数据量统计性测试,为了保证测试准确性,存储的数字信号序列码的长度需为被测adc位数精度的8倍以上。例如adc的精度为10位,则序列长度为2^10*8及以上,即要抓取8196个点或更多点的数值。

58.本实施例中,所述数模转换器300的测试原理为:在对所述数模转换器300进行测试时,所述测试控制器110控制所述数字向量生成器130生成数字向量,所述测试控制模块控制所述数字向量进入所述数模转换器300,所述数模转换器300将所述数字向量转换为模拟信号,并由所述测试控制模块控制所述模拟信号输入到所述比较器140的负端,同时所述测试控制器110控制所述斜坡信号发生器120发出斜坡信号,所述测试控制模块控制所述斜坡信号输入到所述比较器140的正端;所述测试控制器110根据所述比较器140的比较结果控制所述数字向量生成器130生成的数字向量递增,所述计数器150根据所述比较器140的比较结果将时钟计数输入到所述码存储器160进行存储,直至所述数模转换器300的输入码值范围被遍历,所述测试控制器110对所述码存储器160中存储的数值序列进行计算分析。

59.图6显示为本实施例的adc-dac组合的片上自测试系统100测试dac时的原理结构框图。

60.如图6所示,在对所述数模转换器300进行测试时:所述第一选择开关171控制所述斜坡信号发生器120输出的斜坡信号进入所述比较器140,所述第二多路复用器175选通所述数字向量生成器130输出的数字向量进入所述数模转换器300,所述第三选择开关173控

制所述数模转换器300的输出信号进入所述比较器140,所述第三多路复用器176控制选通所述计数器150的时钟计数进入所述码存储器160;所述第一多路复用器174选通所述模数转换器200的片外工作输入信号进入所述模数转换器200,所述第二选择开关172控制所述模数转换器200的信号输出到片上系统芯片外部。

61.于本实施例中,在对所述数模转换器300进行测试时,在所述比较器140的比较结果为所述斜坡信号大于所述数模转换器300的输出信号时,所述测试控制器110控制所述数字向量生成器130生成的数字向量增加1,所述计数器150将时钟计数输入到所述码存储器160进行存储,重复上述过程,直至所述数模转换器300的输入码值范围被遍历。

62.于本实施例中,所述斜坡信号的范围需大于所述数模转换器300的模拟信号输出范围,保证可遍历被测的数模转换器300的所有编码。

63.本实施例中,dac测试流程如下:1)测试控制器110发出控制指令,控制数字向量生成器130发出初始数字向量到被测的数模转换器300的输入端;2)被测的数模转换器300将输入的数字向量转换为模拟输出信号,送至比较器140的负端;3)测试控制器110发出控制指令,控制斜坡信号发生器120发出指定幅度范围与速率的斜坡信号;4)斜坡信号通过低通滤波器180,滤去高频噪声,然后到达比较器140的正端;5)如图7所示,比较器140比较数模转换器300的输出信号与斜坡信号,初始时斜坡信号小于数模转换器300的输出信号,比较器140输出为0,随着斜坡信号的不断增大,当斜坡信号大于数模转换器300的输出信号时,比较器140的输出为1,此时有两个动作:5-1)触发将当前的时钟计数送到码存储器160进行存储;5-2)同时,反馈比较结果给测试控制器110,测试控制器110指令数字向量生成器130发出的数字向量增加1;6)如图7所示,因为数字向量生成器130输出的数字向量值增大,数模转换器300的输出信号随之变大,大于斜坡信号,因此比较器140的输出电平由1变0;7)如图7所示,随着斜坡信号的不断增大,当斜坡信号大于数模转换器300的输出信号时,比较器140的输出由0变1,此时重复5)和6);直至被测的数模转换器300的输入码值范围已被遍历(如8位dac,输入码值范围为0~255),在码存储器160中记录下的时间数值序列用于计算dnl与inl,并与预置的规格值进行比较,判断是否合格。

64.于本实施例中,所述测试控制器110包括:特性值获取模块,测试对比模块以及测试结果输出模块。

65.于本实施例中,所述特性值获取模块用于对所述码存储器160中存储的信号进行计算,生成特性值;所述测试对比模块用于将生成的所述特性值与预设指标值进行对比,确认所述特性值是否符合所述预设指标值;所述测试结果输出模块用于在所述特性值符合所述预设指标值时输出指示所述模数转换器200或所述数模转换器300正常的第一测试结果信号,在所述特性值不符合所述预设指标值时输出指示所述模数转换器200或所述数模转换器300异常的第二测试结果信号。

66.于本实施例中,所述特性值获取模块用于对所述码存储器160中存储的信号进行

计算,生成特性值。其中,所述特性值为静态特性值,所述静态特性值包括dnl(微分非线性,differential non-linearity),inl(积分非线性integral non-linearity)。

67.第一,模数转换器测试中,获取所述静态特性值包括如下过程:1)对码存储器160中存储的数值序列进行柱状图分布处理,生成的柱状图,其中,柱状图横坐标code bin表示为模数转换器200模块的输出码从小到大排序(例如10位的模数转换器200的code bin范围为0~2

10-1,即0~1023),纵坐标height count 表示为一个采样周期内,落在每个code bin上的点的个数。例如10位的模数转换器200,一个采样周期采了32768个点(即2

15

个点),这些点是分布到0~1023共1024个code bin上,每个code bin上落到的点数由纵坐标表示,如code 111这个bin上落到了51个点。

68.模数转换器200的静态特性值(dnl/inl)测试计算流程如下:1)设被测的模数转换器adc的位数为n位,则adc的输出码值个数为n,;2)通过柱状图,计算得到adc每个输出码值(code bin)上的点的个数,设为;3)计算出adc最小有效位device

lsb

(least significant bit);4)计算adc的微分非线性 dnl:; 5)计算积分非线性 inl:;;6)因为斜坡信号的整体范围要大过被测adc的输入范围,所以柱状图上的横坐标0刻度上会累积小于adc输入下限的点数;柱状图上横坐标n-1刻度上累积大于adc输入下限的点数,所以0刻度与n-1刻度的inl与dnl不做计算。

69.于本实施例中,所述测试对比模块用于将生成的所述特性值与预设指标值进行对比,确认所述特性值是否符合所述预设指标值。

70.于本实施例中,所述测试结果输出模块用于在所述特性值符合所述预设指标值时输出指示所述模数转换器200或者所述数模转化器正常的第一测试结果信号,在所述特性值不符合所述预设指标值时输出指示所述模数转换器200或者所述数模转化器异常的第二测试结果信号。

71.即于本实施例中,所述测试控制器110对码存储器160中存储的信号进行计算,得到静态特性值(dnl,inl),然后与预设的指标值进行比对,看是否符合指标。如果符合,则输出第一测试结果信号(pass信号),如果不符合,则输出第二测试结果信号(fail信号)。

72.第二,数模转换器测试中,获取所述静态特性值包括如下过程:

1)码存储器中的数值序列为dac从小到大遍历的每一个码值对应的输出电压幅度的等比例时钟周期计数。如下表1所示:表12)对码存储器中存储的数值序列进行如下计算,可得到dac的静态特性值。

73.2-1)设被测数模转换器dac的位数为n位,则dac的输入码值个数为n, ;2-2)计算出芯片最小有效位device

lsb

(least significant bit):; 为码存储器中地址为n-1的存储单元存储的值,表示一个n位的dac的输入code跳变到最大值时对应的时钟周期累积数。

74.例如表1所示,一个8位的dac,n-1为255,表示为dac的输入code从254跳变到255时,对应的时钟周期累计数为12753。

75.为码存储器中地址为1的存储单元存储的值,表示一个n位的dac的输入code从0跳变到1是对应的时钟周期累积数。

76.例如表1所示,一个8位的dac,表示为dac的输入code从0跳变到1时对应的时钟周期累积数值为13。

77.注意,的值设为0,为时钟周期计数起始点,本身无物理意义,计算inl/dnl都是从开始。

78.2-3)计算微分非线性 dnl:;;为储器中地址为i 1的存储单元存储的值,表示一个n位的dac的输入code从

i跳变到i 1时对应的时钟周期累积数,为码存储器中地址为i的存储单元存储的值,表示一个n位的dac的输入code从i-1跳变到i时对应的时钟周期累积数。

[0079] 2-4)计算积分非线性 inl:;。

[0080]

为码存储器中地址为i的存储单元存储的值,表示一个n位的dac的输入code从i-1跳变到i时对应的时钟周期累积数,为码存储器中地址为1的存储单元存储的值,表示一个n位的dac的输入code从0跳变到1时对应的时钟周期累积数。

[0081]

实施例2图8显示为本实施例中的adc-dac组合的片上自测试方法的流程图。如图8所示,本实施例提供的adc-dac组合的片上自测试方法应用于包含模数转换器200和数模转换器300的片上系统芯片中,所述方法包括:步骤s100,在对所述模数转换器进行测试时,控制一斜坡信号进入模数转换器,由所述模数转换器将所述斜坡信号转换为数字信号,对所述数字信号进行测试;步骤s200,在对所述数模转换器进行测试时,控制一数字向量进入所述数模转换器,由所述数模转换器将所述数字向量转换为模拟信号,将所述模拟信号输入到一比较器的负端,同时控制一斜坡信号进入所述比较器的正端,并根据所述比较器的比较结果控制所述数字向量递增,通过一计数器根据所述比较器的比较结果进行时钟计数,并对所述计数器输出的时钟计数进行测试。

[0082]

由于本实施例中adc-dac组合的片上自测试方法的实现原理与adc-dac组合的片上自测试系统100的原理基本相同,原理间可以通用的技术内容不作重复赘述。

[0083]

需要说明的是,用来实现本技术的adc-dac组合的片上自测试方法的电路结构和原理并不限于图4至图6所示结构,本领域技术人员基于本技术的思想所做出的合理变形皆应被视为本技术的保护范围。

[0084]

综上所述,本技术的adc-dac组合的片上自测试系统设置于片上系统芯片内,无需外加测试设备,即可实现可以对模数转换器和数模转换器进行测试,无需昂贵专用的自动化测试设备,有效节省测试成本,提高测试精度;本技术可灵活重复配置,可快速进行测试,可以做特性分析,有效提高adc-dac组合的片上自测试系统的重复使用率和使用范围;本技术可以在整个片上系统芯片生命周期进行性能监控,自动输出测试结果,测试结构简单、方便。所以本技术有效克服了现有技术中的种种缺点而具高度产业利用价值。

[0085]

上述实施例仅例示性说明本技术的原理及其功效,而非用于限制本技术。任何熟悉此技术的人士皆可在不违背本技术的精神及范畴下,对上述实施例进行修饰或改变。因此,举凡所属技术领域中具有通常知识者在未脱离本技术所揭示的精神与技术思想下所完成的一切等效修饰或改变,仍应由本技术的权利要求所涵盖。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。