1.本实用新型涉及高速芯片技术领域,特别涉及一种具备高可靠度的高速芯片。

背景技术:

2.欲提升dfb芯片的传输速度达成25g的高速传播,必须增加其共振腔中光子的驰张振荡频率(fr),现有技术中往往采取的策略是为dfb设计出更短的共振腔以提升fr,目前一般高速25g-dfb芯片的共振腔约在150μm(左右);在另一方面,这将使得dfb芯片的体积缩小,更不利于散热,而在长时间运作下,芯片因散热不及,后续散热变得更加困难,造成热能积累的恶性循环;由于高温或热积累的运作条件,芯片之光电性表现不但不稳定,并很可能于2000hrs后即急遽劣化失效,即不具备可靠度。

3.所以,小共振腔设计虽能有效提升dfb芯片之传输速度,但是,散热能力弱化对于共振腔之缩小幅度实有相当大的限制,因此对于小共振腔dfb,芯片的散热能力是亟待改善之问题。

技术实现要素:

4.本实用新型要解决的技术问题是提供一种具备高可靠度的高速芯片,以解决现有技术中缩小dfb芯片的体积不利于散热从而使得dfb芯片可靠度低的技术问题。

5.为实现上述目的,本实用新型提供一种具备高可靠度的高速芯片,包括:基板、抗反射膜和高反射膜,所述基板上方从下至上依次设置有n-披覆层、主动层区、p-披覆层、接触层和p极金属电极层,所述基板的下方设有n极金属电极层;所述主动层区包含光栅,所述主动层区的左右两端分别设置有透光开窗层,两个所述透光开窗层的厚度皆大于所述主动层区的厚度,两个所述透光开窗层分别与所述主动层区完全贴覆;所述抗反射膜位于芯片的出光端面,所述高反射膜位于芯片的背光端面。

6.进一步地,两个所述透光开窗层的水平长度不小于所述主动层区水平长度的10%。

7.进一步地,两个所述透光开窗层的下端面皆不高于所述主动层区的下端面。

8.进一步地,所述主动层区之水平长度不大于200μm。

9.进一步地,两个所述透光开窗层的材质吸收波长小于所述主动层区发光波长30nm以上。

10.进一步地,两个所述透光开窗层的材质均为磷化铟。

11.与现有技术相比,本实用新型产生了以下有益效果:本实用新型的一种具备高可靠度的高速芯片,该通过设置两个透光开窗层为芯片提供更好之散热机制,使得芯片在长时间运作下,仍可维持良好之光电性表现,另外所加设的透光开窗层可转换光子路径之聚焦模式,而降低光场强度,此可减少热能积聚,进而提高芯片之可靠度。

附图说明

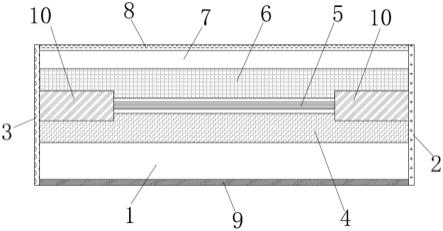

12.图1为本实用新型的结构示意图;

13.图2为本实用新型磊晶示意图;

14.图3为步骤1工序完成后之芯片示意图;

15.图4为步骤4工序完成后之芯片示意图;

16.图5为步骤5工序完成后之芯片示意图;

17.附图标记说明:1-基板,2-抗反射膜,3-高反射膜,4-n-披覆层,5-主动层区,6-p-披覆层,7-接触层,8-p极金属电极层,9-n极金属电极层,10-透光开窗层。

具体实施方式

18.下面结合附图对本实用新型的具体实施方式作进一步说明。在此需要说明的是,对于这些实施方式的说明用于帮助理解本实用新型,但并不构成对本实用新型的限定。此外,下面所描述的本实用新型各个实施方式中所涉及的技术特征只要彼此之间未构成冲突就可以相互组合。

19.请参阅图1,本实用新型的优选实施例提供了一种具备高可靠度的高速芯片,包括:基板1、抗反射膜2和高反射膜3,所述基板1上方从下至上依次设置有n-披覆层4、主动层区5、p-披覆层6、接触层7和p极金属电极层8,所述基板1的下方设有n极金属电极层9;所述主动层区5包含光栅,所述主动层区5的左右两端分别设置有透光开窗层10,两个所述透光开窗层10的厚度皆大于所述主动层区5的厚度,两个所述透光开窗层10分别与所述主动层区5完全贴覆;所述抗反射膜2位于芯片的出光端面,所述高反射膜3位于芯片的背光端面。两个所述透光开窗层10的水平长度不小于所述主动层区5水平长度的10%;透光开窗层10水平长度为10μm以上。两个所述透光开窗层10的下端面皆不高于所述主动层区5的下端面;所述主动层区5之水平长度不大于200μm;主动层区5水平长度为100~200μm。两个所述透光开窗层10的材质吸收波长小于所述主动层区5发光波长30nm以上;两个所述透光开窗层10的材质均为磷化铟。

20.参照图2,主动层区5长度为150μm,厚度为200nm;主动层区5左右二端设置的透光开窗层10,为相同形状、体积之结构,长度为50μm,厚度为500nm。透光开窗层10的下底面距主动层区5的下底面150nm。透光开窗层之材料之吸收波长小于发光材料之发光波长70nm。

21.图2至图5是本实施通过刻蚀、mocvd生长技术实现此实用新型之磊晶设计,以下概述其制作步骤。

22.步骤1、参照图3,完成第一次外延生长,其中包括:基板1、n-披覆层4、主动层区5、p-披覆层6,其左右水平长度为250μm,p-披覆层6厚度為150nm。

23.步骤2、将步骤1制的芯片进行pecvd沉积,沉积sio2做为保护层,厚度为0.3μm。

24.步骤3、进行光刻制程,正中中央区段150μm长度为sio2保护区,左右区段各50μm为曝光刻蚀区;使用boe溶液对曝光区的二氧化硅进行蚀刻。

25.步骤4、参照图4,使用icp蚀刻方法对曝光区之外延材料(主动层区5、n-披覆层4材料)进行蚀刻,外研材料之总蚀刻深度:500nm(制程温度:220℃,蚀刻参数:cl2/bcl3/ar:2/3/5),蚀刻完成后,将中央保护区之sio2去除。在蚀刻完成之后续过程中,尽可能避免蚀刻后之新界面与空气接触的机会,以免新界面因暴露于空气中而氧化。

26.步骤5、参照图5,将刻蚀完成的芯片置入mocvd,对左右二端蚀刻区进行第二次外研,先生长inp材质之透光开窗层10,厚度为500nm;过程中,尽可能避免芯片与空气接触的可能,以免晶圆之蚀刻界面因暴露于空气中而氧化。而后接续在主动层区5与二端之透光开窗层10上,接续生长p-披覆层6、接触层7。

27.步骤6、参照图2,使用光刻、等离子蚀刻技术在晶圆上方之接触层形成脊型(ridge)波导结构,然后在其表面使用pecvd沉积sio2形成绝缘层,之后再去除波导上表面的sio2绝缘层,露出接触层7,接续在接触层7与绝缘层上形成p极金属电极层8,之后将基板1背面减薄抛光至100μm,镀上n极金属电极层9。晶圆经过划裂后,在出光端镀上抗反射膜2,于背光端镀上高反射膜3。至此,工艺完成,此新得到一具高可靠性之高速25g-dfb芯片。

28.老化测试实验:window layer(实验组)、original(对照组)之晶圆磊晶程完成后,同时期、同环境、同方法进行晶圆与晶粒工艺,其中,经晶粒筛选除去电性、外观不良者后,将两组合格dfb芯片进行to封装,再经过to封装后之前测,各组提取合格32颗to进行2000小时老化测试。测试条件:85℃,75ma。

29.老化测试实验结果:结果显示,wl组之32颗to全数通过,而orl组有三颗to未能通过测试(δim大于10%或小于-10%);wl组dfb芯片于2000hrs之高温环境运作中,其光电性仍能具备良好之稳定度(δim于

±

5%内)。可知,本实用新型dfb较传统之dfb具备更高之可靠度。

30.总结来说,与传统高速25g-dfb相较,本实用新型具有以下优点:因于芯片主动区两端加设了inp透光开窗层10,优化了芯片散热机制与出光模式,可有效降低热能积累效应,进而达成芯片之高可靠度;另外,此透光开窗层10亦对主动区5端面提供覆盖保护,可避免主动层区5于后续工艺制程中之损伤与氧化,如此,相较于传统dfb之划裂镜面涵盖主动区层5,本实用新型将具备更高之可靠度。

31.从以上的描述中,可以看出,本实用新型上述的实施例实现了如下技术效果:该通过设置两个透光开窗层10为芯片提供更好之散热机制,使得芯片在长时间运作下,仍可维持良好之光电性表现,另外所加设的透光开窗层10可转换光子路径之聚焦模式,而降低光场强度,此可减少热能积聚,进而提高芯片之可靠度;所加设的透光开窗层10为在磊晶阶段即为主动层区5端面提供保护,并且,为芯片提供了划裂界面,镜面将发生于透光开窗层10,如此在后续之划裂、镀膜工艺制程中,主动层区5端面避免了损伤与氧化的机会,此尤其避开了导致传统dfb芯片发生镜面损耗(comd)的主要原因。

32.以上结合附图对本实用新型的实施方式作了详细说明,但本实用新型不限于所描述的实施方式。对于本领域的技术人员而言,在不脱离本实用新型原理和精神的情况下,对这些实施方式进行多种变化、修改、替换和变型,仍落入本实用新型的保护范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。