具有耦合栅极结构的图像像素

背景技术:

1.本发明整体涉及成像系统,并且更具体地涉及图像传感器中的像素电路。

2.图像传感器通常在电子设备用于捕获图像。在典型的布置中,图像传感器包括被布置成像素行和像素列的图像像素阵列。

3.通常,每个图像像素含有用于响应于入射光生成电荷的光敏元件、存储所生成的电荷的电荷存储结构,以及将一个或多个像素元件彼此耦合的晶体管。在一些应用中,可能期望提供具有一个或多个低增益电容器(例如,用于生成低增益信号的低增益操作模式)的图像像素。然而,包括此类电容器或其他电荷存储结构可能导致包括需要附加像素区域的附加晶体管或其他元件(用于图像像素内的连接性)。由于图像像素的大小被缩减,因此这变得尤其成问题。

4.因此,期望提供具有少量晶体管或其他元件的像素电路和像素配置,同时仍然提供令人满意的像素操作(例如,在低增益操作模式下)。

附图说明

5.图1是根据一些实施方案的具有用于捕获图像的一个或多个图像传感器和处理电路的例示性成像系统的示意图。

6.图2是根据一些实施方案的具有像素阵列和用于该像素阵列的控制和读出电路的例示性图像传感器电路的示意图。

7.图3是根据一些实施方案的具有耦合栅极结构的例示性图像像素的电路图。

8.图4、图5a和图5b是根据一些实施方案的用于操作图像像素诸如图3中的图像像素的例示性时序图。

9.图6是根据一些实施方案的用于实现耦合栅极结构诸如图3中的耦合栅极结构的例示性像素布局。

10.图7是根据一些实施方案的具有带三个输出端子的耦合栅极结构的例示性图像像素的电路图。

11.图8是根据一些实施方案的用于操作图像像素诸如图7中的图像像素的例示性时序图。

12.图9是根据一些实施方案的用于实现耦合栅极结构诸如图7中的耦合栅极结构的例示性像素布局。

13.图10是根据一些实施方案的用于实现耦合栅极结构诸如图7中的耦合栅极结构的另一例示性像素布局。

具体实施方式

14.诸如数码相机、计算机、蜂窝电话和其他电子设备的电子设备可包括图像传感器,该图像传感器收集入射光以捕获图像。图像传感器可包括图像像素阵列。图像传感器中的像素可包括将入射光转换成图像电荷(例如,图像信号)的光敏元件,诸如光电二极管。图像

传感器可具有任何数量(例如,数百或数千或更多)的像素。典型的图像传感器可例如具有数十万或数百万像素(例如,数兆像素)。图像传感器可包括控制电路(诸如,用于操作图像像素的电路)和用于读出图像信号的读出电路,该图像信号与光敏元件所生成的电荷相对应。

15.图1是例示性成像系统(诸如,电子设备)的示意图,该成像系统使用图像传感器捕获图像。图1的成像系统10可为便捷式电子设备,诸如相机、蜂窝电话、平板电脑、膝上型计算机、网络摄像头或摄像机,可为其他类型的成像系统,诸如视频监控系统、机动车成像系统、具有成像能力的视频游戏系统、增强现实和/或虚拟现实系统、无人机系统(例如,无人机)或工业系统,或者可为捕获图像数据的任何其他合适的成像系统或设备。相机模块12(有时称为成像模块)可用于将入射光转换成数字图像数据。相机模块12可包括一个或多个透镜14以及一个或多个对应图像传感器16。透镜14可包括固定透镜和/或可调透镜,并且可包括形成在图像传感器16的成像表面上的微透镜和其他微距镜头。在图像捕获操作期间,可通过透镜14将来自场景的光聚焦到图像传感器16上。图像传感器16可包括用于将模拟像素图像信号转换成提供给存储和处理电路18的对应数字图像数据的电路。如果需要,相机模块12可设置有透镜14的阵列和对应图像传感器16的阵列。

16.存储和处理电路18可包括一个或多个集成电路(例如,图像处理电路、微处理器、诸如随机存取存储器和非易失性存储器的存储设备等),并且可使用与相机模块分开和/或形成相机模块的一部分的部件(例如,形成包括图像传感器16的集成电路或者与图像传感器16相关联的模块内的集成电路的一部分的电路)来实施。当不同于图像传感器16的集成电路的集成电路(例如,芯片)上包括存储和处理电路18时,可相对于具有图像传感器16的集成电路堆叠或封装具有处理电路18的集成电路。可使用处理电路18处理和存储已被相机模块12捕获的图像数据(例如,使用处理电路18上的图像处理引擎、使用处理电路18上的成像模式选择引擎等)。可根据需要使用耦接到处理电路18的有线通信路径和/或无线通信路径将处理后的图像数据提供给外部设备(例如,计算机、外部显示器或其他设备)。

17.如图2所示,图像传感器16可包括含有图像传感器像素22(有时在本文称为图像像素或简称为像素)的像素阵列20以及控制和处理电路24。在本文中作为例示性示例描述的一些配置中,图像像素22可以布置成行和列。阵列20可包含例如数百或数千行以及数百或数千列的图像像素22。控制电路24可耦合到行控制电路26(有时称为行驱动器电路)和列读出和控制电路28(有时称为列控制电路、列读出电路或简称为读出电路)。行控制电路26可从控制电路24接收行地址并且通过一个或多个控制路径诸如行控制路径30将对应的行控制信号诸如复位控制信号、抗光晕控制信号、行选择控制信号、电荷转移控制信号、双转换增益(例如,低转换增益)控制信号和读出控制信号提供给像素22的每一行。可将一个或多个导电路径(诸如,列线32)耦合到阵列20中的像素22的每一列。列线32可用于从像素22读出图像信号以及用于将偏置信号(例如,偏置电流或偏置电压)提供给像素22。如果需要,在像素读出操作期间,可使用行控制电路26选择阵列20中的像素行,并且可沿列线32读出由该像素行中的图像像素22生成的图像信号。

18.列读出电路28可通过列线32接收图像信号(例如,由像素22生成的模拟像素值)。列读出电路28可包括用于临时存储从阵列20读出的校准信号(例如,复位电平信号、参考电平信号)和/或图像信号(例如,图像电平信号)的存储器电路、放大器电路、模数转换(adc)

电路、偏置电路、用于选择性启用或禁用列电路的锁存电路,或者耦合到阵列20中的一个或多个像素列以用于操作像素22和用于从像素22读出图像信号的其他电路。读出电路28中的adc电路可将从阵列20所接收的模拟像素值转换成对应数字像素值(有时称为数字图像数据或数字像素数据)。列读出电路28可将与一个或多个像素列中的像素相关联的数字像素数据提供给控制和处理电路24和/或处理器18(图1)。

19.像素阵列20还可设置有具有多个(颜色)过滤元件(每个过滤元件对应于一个或多个相应像素)的过滤器阵列,该过滤器阵列允许单个图像传感器对不同颜色或不同波长组的光进行采样。例如,图像传感器像素诸如阵列20中的图像像素可设置有具有红色、绿色和蓝色过滤元件的滤色器阵列,该滤色器阵列允许单个图像传感器使用被布置成拜耳马赛克图案的对应红色、绿色和蓝色图像传感器像素对红光、绿光和蓝光(rgb)进行采样。又如,拜耳图案中的绿色像素可被替换为具有宽带滤色器元件(例如,透明滤色器元件、黄色滤色器元件等)的宽带图像像素。在又一个示例中,拜耳图案中的一个绿色像素可被替换为在红外(ir)滤色器元件下形成的ir图像像素,并且/或者其余的红色、绿色和蓝色图像像素也可对ir光敏感(例如,可在除其相应颜色的光之外还使ir光穿过的过滤元件下形成)。这些示例仅仅是例示性的,一般来讲,可在任何期望数量的图像像素22上方形成任何期望颜色和/或波长以及任何期望图案的过滤元件。

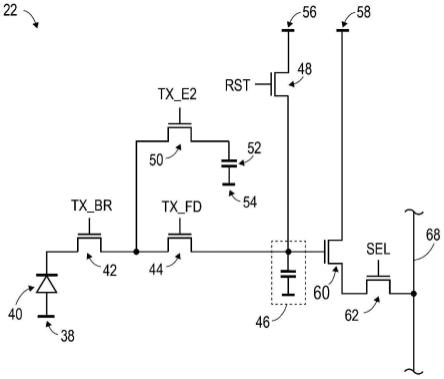

20.图3是例示性图像像素22的电路图。如图3所示,像素22包括光敏元件,诸如光电二极管40。光电二极管40具有耦合到电压端子38的第一端子,该电压端子接收参考电压(例如,接地电压)。可通过光电二极管40收集来自入射光的电荷。光电二极管40可响应于接收到入射光(例如,入射的光子)而生成电荷(例如,电子)。由光电二极管40收集的电荷量可取决于入射光的强度和曝光时间(或积聚时间)。

21.图3中的像素22还包括浮动扩散区,例如浮动扩散区46。浮动扩散区46可以是掺杂半导体区(例如,硅衬底中通过离子注入、杂质扩散或其他掺杂工艺而掺杂的区)。因此,浮动扩散区46可以具有相关联的电荷存储容量(例如,在图3中示意性地示出为电容器)。光电二极管电荷或其他电荷(例如,复位电压电平电荷、暗电流电荷等)可以被转移并存储在浮动扩散区46处以用于像素读出操作。

22.在一些应用中,可能期望延长浮动扩散区46的存储容量,并且通过包括低(转换)增益电容器以低(转换)增益操作模式来操作像素22。如图3所示,像素22包括电荷存储结构,诸如电容器52(例如,低增益电容器)。为了更有效地将浮动扩散区46耦合到电容器52,图3中的像素22可以包括位于电容器52与浮动扩散区46之间的耦合栅极结构(例如,包括彼此耦合的多个晶体管或栅极的结构)。

23.具体地,像素22可以包括晶体管42、44和50(例如,作为像素22中的耦合栅极结构的一部分)。如图3所示,晶体管42和44将光电二极管40耦合(例如,选择性地连接)到浮动扩散区46,从而允许光电二极管生成的电荷使用晶体管42和44从光电二极管40转移到浮动扩散区46。晶体管42和50将光电二极管40耦合到电容器52,从而允许光电二极管生成的电荷使用晶体管42和50从光电二极管40转移到电容器52。电容器52可以被配置为积聚多个接收电荷的实例并存储所积聚的电荷。晶体管44和50将浮动扩散区46耦合到电容器52,从而允许电容器52使用晶体管44和50通过浮动扩散区46与电容器52之间的导电路径连接(例如,以用于电荷共享操作,用于电荷转移操作等)。

24.晶体管50可以耦合到电荷存储结构52的第一端子(例如,电容器52的第一端子)。电荷存储结构52的第二端子(例如,电容器52的第二端子)可以耦合到接收参考电压(信号)的电压端子54。例如,电压端子54可以向电容器52的第二端子提供固定参考电压,或者可以向电容器52的第二端子提供可变参考电压信号(例如,在第一时间段期间表现出第一电压值,在第二时间段期间表现出第二电压值等)。

25.由于光电二极管40将生成的电荷提供到耦合栅极结构中,因此晶体管42的耦合到光电二极管40的端子可以被称为耦合栅极结构的输入端子。类似地,由于耦合栅极结构将光电二极管生成的电荷输出到浮动扩散区46和电容器52,因此晶体管44的耦合到浮动扩散区46的端子和晶体管50的耦合到电容器52的端子可以分别被称为耦合栅极结构的第一输出端子和第二输出端子。

26.如果需要,晶体管42、44和50之间(由其共享)的耦合栅极结构中的中间节点或区域可以是耗尽节点。更一般地,耦合栅极结构可以被配置为(例如,通过具有耗尽节点)使得光电二极管生成的溢出电荷进入对应区域(例如,从光电二极管40到浮动扩散区46或电容器52的溢出电荷)的每次转移可以将所有对应的溢出电荷完全转移到对应区域。如果需要,耦合栅极结构可以包括任何其他合适结构,以促进所有溢出电荷的这种完全转移以及其他(剩余)光电二极管生成的电荷的转移(在需要的情况下)。

27.为了将一个或多个像素元件复位(例如,复位到复位电压电平),像素22可以包括复位晶体管,诸如复位晶体管48。如图3所示,晶体管48将接收参考电压(例如,与复位电压电平相关联的电源电压)的电压端子56耦合到浮动扩散区域46。具体地,当晶体管48被激活(例如,通过断言控制信号rst)时,浮动扩散区46可以被复位到复位电压电平(例如,电源电压)。另外,当晶体管48与其他晶体管一起被激活(例如,通过断言对应的控制信号tx_br、tx_fd和tx_e2,与晶体管42、44和50一起被激活)时,也可以将光电二极管40和电容器52复位到复位电压电平。例如,晶体管42、44和48还可以提供用于光电二极管40的抗光晕路径(例如,到电压端子56)。

28.如图3所示,像素22包括形成像素22的读出部分的源极跟随器晶体管60和像素选择(或行选择)晶体管62。具体地,选择晶体管62具有由选择信号sel控制的栅极端子。当选择信号sel被断言时,晶体管62被激活并且大小与浮动扩散区46处的电荷量成比例的对应像素输出信号经由源极跟随器晶体管60被传递到像素输出路径诸如列线68(例如,图2中的线32)。当浮动扩散区46存储正被读出的光电二极管生成的电荷时,对应像素输出信号可被称为图像(电平)信号。当浮动扩散区46存储正被读出的复位电压电平电荷时,对应像素输出信号可被称为复位电平信号。

29.在例示性图像像素阵列配置中,存在多行和多列的像素22。列线68可与像素22的每一列相关联(例如,一列中的每个图像像素22可通过对应的行选择晶体管62耦合到同一列线68)。控制信号sel可被断言,以将来自所选择图像像素22的像素输出信号读出到列线68上。可将像素输出信号提供给读出电路28(图2),然后提供给处理电路18(图1),以供进一步处理。

30.具有图像像素阵列(诸如图3中的像素22)的图像传感器可在变化的光条件下(例如,在相对弱光环境中、在相对强光环境中、在介于弱光环境与强光环境之间的中等光环境中等)操作。在一些应用中(例如,为了提供高动态范围图像),可能期望图3中的像素22针对

每个积聚周期(例如,针对每个积聚时间段)生成多于一个图像信号(例如,两个图像信号)。

31.图3中的像素22基于溢出电荷(例如,光电二极管生成的电荷的一个或多个溢出部分)生成低转换增益图像信号并且基于剩余电荷(例如,在移除光电二极管生成的电荷的一个或多个溢出部分之后仍存储在该光电二极管处的光电二极管生成的电荷的一部分)生成高转换增益图像信号的配置在本文中作为例示性示例予以描述。因此,图4是示出了如何能够操作像素(诸如图3中的像素22)以生成这些低转换增益信号和高转换增益信号的例示性时序图。

32.在图4的示例中,控制信号sel、tx_br、tx_e2、tx_fd、rst、clg_ref和sh可用于控制像素22的操作。具体地,控制电路诸如行控制电路26和/或控制电路24(图2)可以被配置为通过相应的控制线30(图2)向像素22中的对应元件(以及其他电路诸如读出电路28)提供这些控制信号中的一个或多个(例如,全部)控制信号。参考图3中的像素22,控制电路可以向晶体管62提供控制信号sel,向晶体管42提供控制信号tx_br,向晶体管50提供控制信号tx_e2,向晶体管44提供控制信号tx_fd,向晶体管48提供控制信号rst,向电压端子54提供控制信号(或参考电压信号)clg_ref,并且向对应的读出电路部件(诸如读出电路28(图2)中的采样保持电路以及采样开关或电路)提供控制信号sh。

33.如图4所示,控制电路可以在快门时间段t1、积聚时间段t2和读出时间段t3期间操作像素22。在快门时间段t1期间,控制电路可以完全地断言控制信号sel、tx_br、tx_e2、tx_fd和rst以将像素22中的像素元件(例如,浮动扩散区46、光电二极管40、电容器52等)复位到复位电压电平(例如,在电压端子56处供提供的像素电源电压)。在光电二极管40已被复位到复位电压电平之后(例如,在快门时间段t1期间控制信号tx_br解除断言之后),光电二极管40的积聚时间段可以开始(例如,光电二极管40可以响应于入射光而开始聚积电荷)。

34.在积聚时间段t2期间,可以使用控制信号tx_br、tx_e2和tx_fd调节光电二极管生成的电荷的溢出部分在浮动扩散区46和电容器52之间的转移(例如,选择性地转移)。光电二极管溢出电荷的这种选择性转移可以在多个脉冲时间段内重复执行。晶体管42可以被配置为用作(例如,形成、限定等)势垒,该势垒将光电二极管40处的光电二极管生成的电荷分离成第一部分和第二部分(例如,高于该势垒的第一溢出部分和低于该势垒的第二剩余部分)。具体地,控制电路可以(部分地)将控制信号tx_br断言到合适的电压电平,以控制晶体管42并形成势垒。与tx_br的这种部分断言一起,控制电路还可以(部分地)断言控制信号tx_fd或tx_e2中的一者,以分别将光电二极管生成的电荷的溢出部分转移到浮动扩散区46或电容器52。

35.作为例示性示例,控制电路可以在第一电压电平下提供控制信号以完全地断言控制信号,可以在第二电压电平下提供控制信号以对控制信号解除断言,并且可以在介于第一电压电平与第二电压电平之间的第三合适电压电平下提供控制信号以部分地断言控制信号。用于每个控制信号的第三电压电平可以变化并且可以根据控制信号的类型和功能根据需要进行调整(例如,以提供期望的势垒水平,以确保足够的电荷转移等)。

36.在图4的示例中,积聚时间段t2可以包括多个脉冲时间段t2-1、t2-2、...、t2-n,在此期间进行溢出电荷到浮动扩散区46和电容器52的转移。虽然在图4的示例中,示出了三个此类脉冲时间段,但这仅仅是例示性的。如果需要,积聚时间段t2可以包括任何合适数量的脉冲时间段。在每个时间段期间,光电二极管生成的电荷的相应溢出电荷部分可以首先转

移到浮动扩散区46,然后转移到电容器52。

37.如图4所示,每个脉冲时间段可以包括控制信号tx_br的部分断言以及同时进行的tx_fd的(部分)断言(例如,控制信号tx_br和tx_fd的断言脉冲),以设置合适的势垒来限定光电二极管生成的电荷的溢出部分并将所限定的光电二极管生成的电荷的溢出部分转移到浮动扩散区46(例如,通过晶体管42和44)。在脉冲式提供控制信号tx_br和tx_fd之后的合适时间量之后,也可以在脉冲时间段内脉冲式提供控制信号tx_br和tx_e2。具体地,控制信号tx_br的部分断言可以与控制信号tx_e2的(部分)断言同时进行,以设置合适的势垒来限定光电二极管生成的电荷的溢出部分并将所限定的光电二极管生成的电荷的溢出部分转移到电容器52(例如,通过晶体管42和50)。在多个脉冲时间段内转移到电容器52的光电二极管生成的电荷的溢出部分可以彼此积聚或组合。

38.在积聚时间段期间,控制电路可以部分地断言控制信号rst(周期性地或连续地)以提供用于光电二极管生成的电荷的抗光晕路径(例如,用于转移到浮动扩散区46的电荷的溢出部分并且不用于生成任何图像信号)。

39.如图4所示,在每个脉冲时间段期间的像素22的操作仅仅是例示性的。如果需要,控制电路可以以任何其他合适的方式断言控制信号tx_br、tx_e2和tx_fd。作为图5a中所示的第一例示性示例,在每个脉冲时间段期间,控制电路在同时断言控制信号tx_br和tx_e2之前可以多次(例如,以多个脉冲)同时断言控制信号tx_br和tx_fd。作为图5b中所示的第二例示性示例,在每个脉冲时间段期间,控制电路可以连续地(并且部分地)断言控制信号tx_br而不是脉冲式提供控制信号tx_br(如图4和图5a所示),并且可以在脉冲式提供控制信号tx_e2之前断言控制信号tx_fd持续较长时间段(例如,持续相当长的时间量,在此期间控制信号tx_e2未被断言)。如果需要,控制电路可以使用图5a或图5b中所示的方案(例如,而不是图4中的方案)在积聚时间段中的一个或多个脉冲时间段处操作像素22。

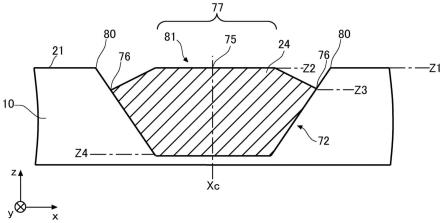

40.重新参考图4,控制电路可以操作像素22以在最终脉冲时间段t2_n之后的读出时间段t3期间执行像素读出操作。控制电路可以在读出时间段t3期间(或至少在像素输出信号被转移到像素输出或列线时)在整个像素读出操作中断言控制信号sel。读出时间段t3可以包括用于存储在电容器52处的溢出电荷的第一读出时间段t3-1和用于存储在光电二极管40处的剩余电荷的第二读出时间段t3-2。

41.在读出时间段t3-1期间,控制电路可以(部分地)断言控制信号tx_br和tx_fd并且断言控制信号rst,以从光电二极管40转移和移除溢出电荷部分并将浮动扩散区46复位到复位电压电平(例如,像素电源电压)。然后,控制电路可以同时(完全地)断言控制信号tx_e2和tx_fd,以通过晶体管44和50将电容器52导电地连接到浮动扩散区46。这可以通过使用电容器52扩展浮动扩散区46的存储容量来允许在电容器52处对溢出电荷(例如,将来自每个脉冲时间段的溢出电荷组合或积聚的溢出电荷)进行低转换增益读出。具体地,控制电路可以断言控制信号sh以激活读出电路中的采样电路,从而采样并存储(例如,在采样电路处)与在电容器52与浮动扩散区46之间共享的溢出电荷相关联的低转换增益图像信号。

42.然后,控制电路可以断言控制信号rst(同时控制信号tx_e2和tx_fd保持被断言)以将浮动扩散区46和电容器52复位到复位电压电平(例如,在电压端子56处提供的像素电源电压)。在控制信号rst被解除断言之后,控制电路可以断言控制信号sh(同时控制信号tx_e2和tx_fd保持被断言)以采样并存储基于浮动扩散区46(其具有在低转换增益操作模

式下通过电容器52扩展的存储容量)处的复位电平电压生成的复位电平信号。该复位电平信号可以与溢出电荷低转换增益图像信号相关联,并且可以用于补偿溢出电荷低转换增益图像信号中的噪声。

43.在读出时间段t3-1之后和读出时间段t3-2期间,控制电路可以再次断言控制信号rst以将浮动扩散区复位到复位电压。在控制信号rst被解除断言之后,控制电路可以断言控制信号sh(同时控制信号tx_e2和tx_fd被解除断言)以采样并存储基于浮动扩散区46处的复位电平电压生成的另一复位电平信号(在高转换增益操作模式下,其中电容器52与浮动扩散区46断开连接)。该复位电平信号可以与光电二极管存储电荷高转换增益图像信号相关联,并且可以与随后读出和采样的光电二极管存储电荷高转换增益图像信号形成相关双采样读出。

44.特别地,在对该复位电平信号进行采样之后,控制电路可以同时(完全地)断言控制信号tx_br和tx_fd,以通过晶体管42和44将光电二极管存储的电荷从光电二极管40转移到浮动扩散区46。随后,控制电路可以断言控制信号sh以激活读出电路中的采样电路,从而采样并存储与从光电二极管40转移到浮动扩散区46的光电二极管存储的电荷相关联的高转换增益图像信号(在高转换增益操作模式下,其中电容器52与浮动扩散区46断开连接)。

45.如果需要,在电压端子54(图3)处提供的参考电压信号可以在像素操作的不同时间段期间处于不同的电压,以向电容器52的第二端子提供不同的参考电压。作为图4所示的例示性示例,控制电路可以在快门时间段t1和读出时间段t3期间提供第一参考电压电平,并且可以在积聚时间段t2期间提供第二参考电压电平。这仅仅是例示性的。

46.以上文结合图4、图5a和图5b所述的方式,控制电路可以操作像素22以在低转换增益操作模式下生成并读出溢出电荷图像信号和对应的复位电平信号,并且在高转换增益操作模式下(并且在相关双采样读出中)生成和读出光电二极管存储电荷图像信号和对应的复位电平信号。有利地,通过利用耦合栅极结构,像素22被配置为在省略多个元件(例如,将电容器52直接连接到浮动扩散区46的晶体管)的同时生成这些像素信号。换句话说,电容器52仅通过至少两个晶体管(该两者也用于溢出电荷调节目的)连接到浮动扩散区46,并且不需要将电容器52直接连接到浮动扩散区46的单独晶体管。这有利地减少了实现像素时的面积要求,并且提供了改进的像素配置,特别是在利用具有小像素尺寸的像素的应用中。

47.图6是用于实现耦合栅极结构诸如图3中的像素22中的耦合栅极结构(例如,图3中的晶体管42、44和50)的例示性像素布局的示意性平面图。如图6所示,晶体管(或栅极)42可沿第一方向插置在光电二极管40与晶体管(或栅极)44和50之间。晶体管50和44可沿垂直于第一方向的第二方向插置在端子53(例如,连接到电容器52的第二端子,该第二端子与连接到电压端子54的端子相对)与端子47(例如,连接到或形成浮动扩散区46的一部分)之间。以这种方式配置,晶体管42(通过接收部分被断言的控制信号)可以在区域43中形成势垒(有时称为限定来自光电二极管40的溢出电荷的溢出势垒)。

48.在积聚时间段期间(例如,在图4、图5a或图5b之一中的每个脉冲时间段期间),可以以合适频率和持续时间一次一个地断言控制信号tx_fd(用于晶体管44)和tx_e2(用于晶体管50),以调节由势垒区域43限定的溢出电荷的流向端子47(例如,到浮动扩散区46)或端子53(例如,到电容器52)中的一者,分别如箭头72和74所示。在读出时间段(例如,图4中的读出时间段t3-1)期间,控制信号tx_fd和tx_e2可以被断言以导电地连接端子53和47,如箭

头76所示,从而连接电容器52和浮动扩散区46以用于低转换增益工作模式(同时用于晶体管42的控制信号tx_br被解除断言,并且光电二极管40与电容器52和浮动扩散区46隔离)。

49.如图6所示的像素中的耦合栅极结构的布局仅仅是例示性的。如果需要,可以使用任何合适的像素布局来实现耦合栅极结构(例如,图3中的像素22中的耦合栅极结构)。

50.在图3的示例中,像素22包括具有两个输出端子(例如,耦合到低增益电容器52的第一输出端子和耦合到浮动扩散区46的第二输出端子)的耦合栅极结构。这仅仅是例示性的。如果需要,图像像素可以包括具有耦合到适当对应元件的任何合适数量的输出端子的耦合栅极结构。

51.图7是具有带三个输出端子的耦合栅极结构的例示性图像像素22的电路图。在一些例示性实施方案中,阵列20(图2)可以包括图7中的图像像素22’。像素22’包括与图3中的像素22相同或类似元件中的一些(例如,光电二极管40、晶体管42、44、48、50、60和62、电容器52、浮动扩散区46)。省略了对这些相同或类似元件的描述,以免不必要地模糊图7的实施方案。除非另外指明,否则像素22’中的对应元件可以用于相同或类似的功能,以相同或类似的方式彼此耦合和连接,并且以与结合图3至图6中的像素22描述的元件相同或类似的方式进行配置和操作。

52.如图7所示,像素22’包括两个电荷存储结构,诸如两个低增益电容器52和82(与图3中的像素22中的一个低增益电容器52相比)。因此,像素22’包括具有一个输入端子(例如,晶体管42的耦合到光电二极管40的端子)和三个输出端子(例如,晶体管50的耦合到电容器52的端子,晶体管44的耦合到浮动扩散区46的端子,以及晶体管80的耦合到电容器82的端子)的耦合栅极结构。可以在图7的示例中的三个输出端子(而不是图3的示例中的两个输出端子)之间调节来自光电二极管40的溢出电荷流。

53.如图7所示并且类似于电容器52,电容器82在第一端子处耦合到晶体管80并且在第二端子处耦合到电压端子84。电压端子84可以接收参考电压(信号)。例如,电压端子84可以向电容器82的第二端子提供固定参考电压,或者可以向电容器82的第二端子提供可变参考电压信号(例如,在第一时间段期间表现出第一电压值,并且在第二时间段期间表现出第二电压值)。如果需要,电压端子54和84可以接收相同的参考电压(信号)。

54.在图7的示例中,晶体管42和80将光电二极管40耦合到电容器82,从而允许电容器82使用晶体管42和80从光电二极管40接收高于由晶体管42设置的势垒的溢出电荷。晶体管44和80将浮动扩散区46耦合到电容器82,从而允许电容器82使用晶体管44和80在浮动扩散区46与电容器82之间形成导电路径(例如,以用于电荷共享操作,用于电荷转移操作等)。类似于电容器52,电容器82可以被配置为在多个脉冲时间段内积聚从光电二极管40接收的溢出电荷并存储所积聚的溢出电荷。

55.图8是示出如何能够操作像素(诸如图7中的像素22’)以基于单个积聚周期(例如,单个积聚时间段)生成多个图像信号的例示性时序图。特别地,由于电容器52和82可以各自单独存储对应的所积聚溢出电荷并且被配置为扩展浮动扩散区46的存储容量,因此像素22’可以操作为生成两个低增益图像信号(例如,大于在结合图3至图6描述的例示性示例中的像素22的情况下生成的一个低增益图像信号)。

56.图8中的时序图(例如,结合图7中的像素22’描述)包括与图4中的时序图(例如,结合图3中的像素22描述)相同或类似的特征中的一些。省略了对这些相同或类似特征的描

述,以免不必要地模糊图8的实施方案。除非另有说明,否则图8的时序图中的对应特征可以用于相同或类似的功能,具有相同或类似的特性,并且以与结合图4的时序图描述的特征相同或类似的方式配置和操作像素(例如,像素行、像素阵列)。

57.在图8的示例中,除了控制信号sel、tx_br、tx_e2、tx_fd、rst、clg_ref和sh(如结合图4所描述)之外,控制信号tx_e3也可用于控制图7中像素22’的操作。如结合图3和图4类似地描述,可以将每个控制信号提供给图7中的像素22’中的对应元件。相对于控制信号tx_e3,控制电路可以向图7中的像素22’中的晶体管80提供控制信号tx_e3。具体地,控制电路诸如行控制电路26和/或控制电路24(图2)可以被配置为向像素22’中的对应元件(以及其他电路诸如读出电路28)提供这些控制信号中的一个或多个(例如,全部)控制信号。

58.如图8所示,控制电路可以在快门时间段t1、积聚时间段t2和读出时间段t3期间操作像素22’。在快门时间段t1期间,除了控制信号sel、tx_br、tx_e2、tx_fd和rst之外,控制电路还可以完全地断言控制信号tx_e3以将像素22’中的像素元件(例如,电容器82、浮动扩散区46、光电二极管40、电容器52等)复位到复位电压电平(例如,在电压端子56处提供的像素电源电压)。

59.在积聚时间段t2期间,控制电路可以类似地在多个脉冲时间段t2-1、t2-2、...、t2-n中操作像素22’。除了如结合图4所述在每个脉冲时间段期间在控制信号tx_fd(用于晶体管44)和tx_e2(用于晶体管50)之间进行调节之外,控制电路还可以在用于晶体管80的控制信号tx_e3(与控制信号tx_fd和tx_e2结合)之间进行调节。这可以用于将由晶体管42限定的溢出电荷分配到浮动扩散区46、电容器82或电容器52中的一者(一次一个)。在任何给定脉冲时间段期间,可以将相应的溢出电荷转移到浮动扩散区46、电容器82和电容器52中的每一者。

60.在图8的示例中,对于每个脉冲时间段,对控制信号tx_br和tx_e3的同时(部分)断言可以发生在对控制信号tx_br和tx_fd的同时(部分)断言和对控制信号tx_br和tx_e2的同时(部分)断言之间。另外,对于每个脉冲时间段,对tx_br和tx_fd的同时断言与对tx_br和tx_e3的同时断言之间的第一时间段可以短于对tx_br和tx_e3的同时断言与对tx_br和tx_e3的同时断言之间的第二时间段。例如,这可以允许电容器82在比电容器52更强(更亮)的光照条件下存储电荷。如结合图4所描述,电容器52可以积聚或组合在多个脉冲时间段内接收的溢出电荷。类似地,电容器82可以积聚或组合在多个脉冲时间段内接收的溢出电荷。

61.在读出时间段t3期间,控制电路可以针对像素22’以与针对像素22结合图4描述的类似方式分别在时间段t3-1和t3-2期间对与电容器52(例如,cap_e2读出)和光电二极管40(pd读出)相关联的信号执行像素读出操作。另外,当操作像素22’时,控制电路还可以执行读出操作以包括在读出时间段t3-1之前并且在积聚时间段t2之后的读出时间段t3-0期间对与电容器82相关联的信号的读出(例如,cap_e3读出)。

62.与电容器52的读出操作类似(例如,在图4中的时间段t3-1期间),在读出时间段t3-0期间,控制电路可以通过断言控制信号rst并且部分地断言控制信号tx_br和tx_fd来首先复位浮动扩散区46然后从光电二极管40移除任何附加溢出过量电荷。

63.然后,控制电路可以同时(完全地)断言控制信号tx_e3和tx_fd,以通过晶体管44和80将电容器82导电地连接到浮动扩散区46。这可以通过使用电容器82扩展浮动扩散区46的存储容量来允许在电容器82处对溢出电荷(例如,将来自每个脉冲时间段的溢出电荷组

合或积聚的溢出电荷)进行低转换增益读出。具体地,控制电路可以断言控制信号sh以激活读出电路中的采样电路,从而采样并存储(例如,在采样电路处)与在电容器82与浮动扩散区46之间共享的溢出电荷相关联的低转换增益图像信号。

64.随后,控制电路可以断言控制信号rst(同时控制信号tx_e3和tx_fd保持被断言)以将浮动扩散区46和电容器82复位到复位电压电平(例如,在电压端子56处提供的像素电源电压)。在控制信号rst被解除断言之后,控制电路可以断言控制信号sh(同时控制信号tx_e3和tx_fd保持被断言)以采样并存储基于浮动扩散区46(其具有在低转换增益操作模式下通过电容器82扩展的存储容量)处的复位电压电平生成的复位电平信号。该复位电平信号可以与溢出电荷低转换增益图像信号相关联,并且可以用于补偿溢出电荷低转换增益图像信号中的噪声。

65.由于在读出时间段t3-0之后,浮动扩散区46已被复位到复位电压电平,读出时间段t3-1可以省略另一浮动扩散区复位操作(例如,与如结合图4所描述的读出时间段t3-1形成对比)。否则,控制电路可以在读出时间段t3-1和t3-2期间操作像素22’,如针对图3中的像素22结合图4中的类似描述。另外,如果需要,可以将参考电压信号clg_ref提供给电压端子84(除电压端子54之外)。

66.在图3至图6的示例中,像素22可以生成对相对较强光照条件而言最优的第一(e2)低转换增益信号(与存储在电容器52处的溢出电荷相关联)和对相对较弱光照条件而言最优的第二(e1)高转换增益信号(与存储在光电二极管40处的剩余电荷相关联)。在图7和图8的示例中,像素22’也可以生成对相对较强光照条件而言最优的第一(e2)低转换增益信号(与存储在电容器52处的溢出电荷相关联)和对相对较弱光照条件而言最优的第二(e1)高转换增益信号(与存储在光电二极管40处的剩余电荷相关联)。另外,像素22’可以生成对相对更强光照条件而言最优的附加(e3)低转换增益信号(与存储在电容器82处的溢出电荷相关联),从而进一步扩展像素22’的动态范围(例如,在与像素22相比时)。

67.图9和图10是用于实现耦合栅极结构诸如图7中的像素22’中的耦合栅极结构(例如,图7中的晶体管42、44、50和80)的例示性像素布局的示意性平面图。如图9所示,晶体管(或栅极)42可插置在光电二极管40与晶体管(或栅极)44、50和80之间。晶体管42可以在一侧与晶体管50相邻,可以在相对侧与晶体管80相邻,并且可以在中间与晶体管44相邻。类似地,晶体管44可以在一侧与晶体管50相邻,可以在相对侧与晶体管80相邻,并且可以在中间与晶体管42相邻。晶体管50和80可以通过晶体管42和44的部分彼此分开。晶体管50可以耦合到连接到电容器52的第一端子的端子。晶体管80可以耦合到连接到电容器82的第一端子的端子。晶体管44可以耦合到连接到浮动扩散区46的端子。

68.以这种方式配置,晶体管42(通过接收部分被断言的控制信号)可以形成限定来自光电二极管40的溢出电荷的势垒。在积聚时间段期间(例如,在图8中的每个脉冲时间段期间),可以调节(例如,以合适频率和持续时间一次一个地断言)控制信号tx_fd(用于晶体管44)、tx_e2(用于晶体管50)和tx_e3(用于晶体管80),以将高于所形成势垒的溢出电荷引导到浮动扩散区46、电容器52或电容器82中的一者。在读出时间段(例如,图8中的读出时间段t3-1)期间,控制信号tx_fd和tx_e2可以被断言以导电地连接电容器52和浮动扩散区46以用于低转换增益操作模式(同时用于晶体管42的控制信号tx_br和用于晶体管80的tx_e3被解除断言,并且光电二极管40和电容器82与电容器52和浮动扩散区46隔离)。在读出时间段

(例如,图8中的读出时间段t3-0)期间,控制信号tx_fd和tx_e3可以被断言以导电地连接电容器82和浮动扩散区46以用于低转换增益操作模式(同时用于晶体管42的控制信号tx_br和用于晶体管50的tx_e2被解除断言,并且光电二极管40和电容器52与电容器82和浮动扩散区46隔离)。

69.在图10所示的另选布局中,晶体管42、50、80和44可以在矩形像素轮廓的四个角处形成。(导电)注入区90可与晶体管42(例如,突出部分42-1)、50、80和44重叠,从而允许溢出电荷转移到对应的电荷存储结构(例如,电容器52、电容器82和连接到晶体管44的浮动扩散区46)。另一(导电)注入区92可与晶体管50和44重叠,从而在电容器52和浮动扩散区46之间提供导电路径(例如,通过晶体管50和44并通过注入区92)。另一(导电)注入区94可与晶体管80和44重叠,从而在电容器82和浮动扩散区46之间提供导电路径(例如,通过晶体管80和44并通过注入区94)。图10中的配置可以配置像素22以表现出与图9的功能相同的功能。

70.如图9和图10所示的像素中具有三个输出端子的耦合栅极结构的布局仅仅是例示性的。如果需要,可以使用任何合适的像素布局来实现耦合栅极结构(例如,图7中的像素22’中的耦合栅极结构)。

71.已经描述了各种实施方案,示出了具有含耦合栅极结构的图像像素的图像传感器。

72.作为例示性示例,图像传感器像素可以包括光敏元件(例如,光电二极管)、浮动扩散区、将该光敏元件耦合到该浮动扩散区的第一晶体管和第二晶体管、电荷存储结构(例如,电容器)和第三晶体管。该第二晶体管和该第三晶体管可以被配置为在像素读出操作期间(例如,在存储在电荷存储结构处的溢出电荷的低转换增益读出期间)在浮动扩散区与电荷存储结构之间形成导电路径。该第一晶体管可以被配置为形成势垒,该势垒限定由光敏元件生成的电荷的溢出部分。该第一晶体管和该第三晶体管可以被配置为将电荷的溢出部分从光敏元件转移到电荷存储结构。图像传感器像素还可包括将浮动扩散区耦合到电源电压端子的复位晶体管,以及将浮动扩散区耦合到像素输出路径的源极跟随器晶体管。如果需要,图像传感器像素可以被配置为基于电荷的溢出部分输出低转换增益图像信号,并且可以被配置为基于存储在光敏元件处的电荷的剩余部分输出高转换增益图像信号。

73.如果需要,图像传感器像素还可包括附加电荷存储结构(例如,附加电容器)和第四晶体管。该第一晶体管和该第四晶体管可以被配置为将电荷的溢出部分从光敏元件转移到附加电荷存储结构。该第二晶体管和该第四晶体管可以被配置为在像素读出操作期间(例如,在存储在附加电荷存储结构处的溢出电荷的低转换增益读出期间)在浮动扩散区与该附加电荷存储结构之间形成附加导电路径。如果需要,图像传感器像素可以被配置为基于存储在该电荷存储结构处的电荷的第一部分输出第一低转换增益图像信号,可以被配置为基于存储在该附加电荷存储结构处的电荷的第二部分输出第二低转换增益图像信号,并且可以被配置为基于存储在该光敏元件处的电荷的剩余部分输出高转换增益图像信号。

74.作为另一例示性示例,图像传感器可以包括控制电路(例如,行控制电路)、读出电路(例如,列读出电路系统)和耦合到该控制电路并且耦合到该读出电路的图像像素阵列。该阵列中的一个或多个图像像素可以各自包括:光敏元件、浮动扩散区、电容器和耦合栅极结构,该耦合栅极结构具有耦合到该光敏元件的输入端子、耦合到该浮动扩散区的第一输出端子和耦合到该电容器的第二输出端子。该控制电路可以被配置为控制该耦合栅极结构

以在该第一输出端子和该第二输出端子之间形成导电路径,并且通过该耦合栅极结构将该浮动扩散区连接到该电容器。

75.具体地,该耦合栅极结构可以包括耦合到该光敏元件的第一晶体管、耦合到该浮动扩散区的第二晶体管和耦合到该电容器的第三晶体管。该控制电路可以被配置为控制该第一晶体管以限定由该光敏元件生成的电荷的溢出部分并且限定由该光敏元件生成并存储在该光敏元件处的电荷的剩余部分。该控制电路可以被配置为激活该第二晶体管以将该电荷的溢出部分的第一组转移到该浮动扩散区并且激活该第三晶体管以将该电荷的溢出部分的第二组转移到该电容器。该读出电路可以被配置为(例如,从图像像素)接收基于该电荷的溢出部分的第二组生成的第一图像信号并且接收基于存储在该光敏元件处的该电荷的剩余部分生成的第二图像信号。

76.作为另一例示性示例,一种操作图像传感器像素的方法可以包括:响应于光敏元件处的入射光而生成电荷,在第一晶体管处限定所生成电荷的溢出部分,使用第二晶体管和第三晶体管调节所生成电荷的溢出部分在浮动扩散区与电荷存储结构(例如,电容器)之间的转移(例如,一次一个地选择性地激活该第二晶体管和该第三晶体管,以将相应的溢出部分转移到该浮动扩散区或该电荷存储结构),并且在读出操作期间(例如,在存储在该电荷存储结构处的溢出电荷的低转换增益读出期间)使用该第二晶体管和该第三晶体管将该浮动扩散区连接到该电荷存储结构。

77.该方法还可包括在使用该第二晶体管和该第三晶体管将该浮动扩散区连接到该电荷存储结构时输出低转换增益图像信号,在读出操作期间(例如,针对存储在该光敏元件处的该剩余电荷的高转换增益读出)使用该第一晶体管和该第二晶体管将所生成的电荷的剩余部分转移到该浮动扩散区,以及在使用该第一晶体管和该第二晶体管将所生成的电荷的剩余部分转移到该浮动扩散区之后输出高转换增益图像信号。如果需要,该方法还可包括在使用该第二晶体管和该第三晶体管将该浮动扩散区连接到该电荷存储结构之前,移除转移到该浮动扩散区的所生成电荷的任何溢出部分(例如,通过将该浮动扩散区复位到复位电压电平)。

78.根据一个实施方案,一种图像传感器像素可包括:光敏元件;浮动扩散区;第一晶体管和第二晶体管,该第一晶体管和该第二晶体管将该光敏元件耦合到该浮动扩散区;电荷存储结构;和第三晶体管。该第二晶体管和该第三晶体管可被配置为在像素读出操作期间在该浮动扩散区与该电荷存储结构之间形成导电路径。

79.根据另一个实施方案,该电荷存储结构可包括电容器。

80.根据另一个实施方案,该电容器可以被配置为在低转换增益操作模式下扩展该浮动扩散区的存储容量。

81.根据另一个实施方案,该第一晶体管可以被配置为形成势垒,该势垒限定由该光敏元件生成的电荷的溢出部分。

82.根据另一个实施方案,该第一晶体管和该第三晶体管可以被配置为将该电荷的溢出部分从该光敏元件转移到该电容器。

83.根据另一个实施方案,该图像传感器像素可以被配置为基于该电荷的溢出部分输出低转换增益图像信号,并且可以被配置为基于存储在该光敏元件处的电荷的剩余部分输出高转换增益图像信号。

84.根据另一个实施方案,该图像传感器像素还可包括:复位晶体管,该复位晶体管将该浮动扩散区耦合到电源电压端子;和源极跟随器晶体管,该源极跟随器晶体管将该浮动扩散区耦合到像素输出路径。

85.根据另一个实施方案,该第一晶体管、该第二晶体管和该复位晶体管可以形成该光敏元件的抗光晕路径。

86.根据另一个实施方案,该图像传感器像素还可包括:附加电荷存储结构;以及第四晶体管。该第二晶体管和该第四晶体管可以被配置为在该像素读出操作期间在该浮动扩散区与该附加电荷存储结构之间形成附加导电路径。

87.根据另一个实施方案,该图像传感器像素可以被配置为基于存储在该电荷存储结构处的电荷的第一部分输出第一低转换增益图像信号,可以被配置为基于存储在该附加电荷存储结构处的电荷的第二部分输出第二低转换增益图像信号,并且可以被配置为基于存储在该光敏元件处的电荷的剩余部分输出高转换增益图像信号。

88.根据一个实施方案,一种图像传感器可包括:控制电路;读出电路;以及图像像素阵列,该图像像素阵列耦合到该控制电路并且耦合到该读出电路。该阵列中的图像像素可包括:光敏元件;浮动扩散区;电容器;以及耦合栅极结构,该耦合栅极结构具有耦合到该光敏元件的输入端子、耦合到该浮动扩散区的第一输出端子和耦合到该电容器的第二输出端子。该控制电路可以被配置为控制该耦合栅极结构以在该第一输出端子和该第二输出端子之间形成导电路径,并且通过该耦合栅极结构将该浮动扩散区连接到该电容器。

89.根据另一个实施方案,该耦合栅极结构可以包括耦合到该光敏元件的第一晶体管、耦合到该浮动扩散区的第二晶体管和耦合到该电容器的第三晶体管。

90.根据另一个实施方案,该控制电路可以被配置为控制该第一晶体管以限定由该光敏元件生成的电荷的溢出部分并且限定由该光敏元件生成并存储在该光敏元件处的电荷的剩余部分。

91.根据另一个实施方案,该控制电路可以被配置为激活该第二晶体管以将该电荷的溢出部分的第一组转移到该浮动扩散区并且激活该第三晶体管以将该电荷的溢出部分的第二组转移到该电容器。

92.根据另一个实施方案,该读出电路可以被配置为接收基于该电荷的溢出部分的第二组生成的第一图像信号并且接收基于存储在该光敏元件处的该电荷的剩余部分生成的第二图像信号。

93.根据一个实施方案,一种操作图像传感器像素的方法可以包括:在光敏元件处,响应于入射光生成电荷;在第一晶体管处,限定所生成的电荷的溢出部分;使用第二晶体管和第三晶体管调节所生成的电荷的溢出部分在浮动扩散区与电荷存储结构之间的转移;以及在读出操作期间,使用该第二晶体管和该第三晶体管将该浮动扩散区连接到该电荷存储结构。

94.根据另一个实施方案,该方法还可包括:在使用该第二晶体管和该第三晶体管将该浮动扩散区连接到该电荷存储结构时,输出低转换增益图像信号。

95.根据另一个实施方案,该方法还可包括:在该读出操作期间,使用该第一晶体管和该第二晶体管将所生成的电荷的剩余部分转移到该浮动扩散区。

96.根据另一个实施方案,该方法还可包括:在使用该第一晶体管和该第二晶体管将

所生成的电荷的剩余部分转移到该浮动扩散区之后,输出高转换增益图像信号。

97.根据另一个实施方案,该方法还可包括:在使用该第二晶体管和该第三晶体管将该浮动扩散区连接到该电荷存储结构之前,移除转移到该浮动扩散区的所生成电荷的任何溢出部分。

98.前述内容仅仅是对本发明原理的例示性说明,本领域技术人员可以在不脱离本发明的范围和实质的前提下进行多种修改。上述实施方案可单个实施或以任意组合方式实施。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。