1.本发明是有关于应用于显示面板的控制电路及控制方法。

背景技术:

2.液晶显示器所呈现的画面一般可以称为暂留型显示器(hold-type display),以显示画面每秒更新60次(60hz)来说,画面每16.67毫秒(ms)会更新一次,而在画面更新前,当前显示的画面是静置不动的。一般液晶显示器最大的缺点之一就是动态模糊(motion blur),而产生此类动态模糊的原因是因为眼睛在追踪物体时,会依据物体移动的速率而有当下预期的位置,但因为液晶显示器更新画面的时间是不连续的,因此在特定时间点上物体实际位置和大脑预期位置会有误差。另一方面,因为人眼有视觉暂留及动态补偿,大脑会在追踪物体的过程将画面接续起来,类似数学上积分的效果,所以如果画面更新频率不够高且停留在单一位置的时间过长,大脑补偿完后则会看到动态拖影的效果。

3.现有技术中已有解决动态模糊的方法,例如在两个帧之间插入补偿帧或是插入黑画面,然而,由于液晶显示器在显示画面时是采用逐行(row)扫描的方式,且液晶的反应时间也可能不够快,因此,上述方法除了会增加处理电路的计算量之外,也会有像素同步的问题,亦即屏幕上方与屏幕下方的画面效果可能会不一致。

4.此外,在某些应用中,影像来源产生影像数据的速度并不固定,因此,目前有部分的液晶显示器采用可变更新率(variable refresh rate)的显示方式,亦即液晶显示器所播放的影像的帧速率(frame rate)会随着所接收到的影像数据的速率而改变,亦即不具有固定的帧速率。在这种情况下,如何有效处理动态模糊是一个重要的课题。

技术实现要素:

5.因此,本发明的目的之一在于提出一种应用于液晶显示器的控制电路,其可以在影像数据的帧速率不固定的情形下,采用倍频的方式来驱动显示面板,以解决现有技术中的问题。

6.在本发明的一个实施例中,公开了一种应用于显示面板的控制电路,其包含有接收接口、影像处理电路以及传送接口。该接收接口用以接收影像数据,其中该影像数据具有不固定的帧速率;该影像处理电路用以从该接收接口接收该影像数据,并根据该影像数据的帧速率来将该影像数据进行倍频操作以产生输出影像数据,其中该输出影像数据的帧速率为该影像数据的正整数倍;以及该传送接口用以从该影像处理电路接收该输出影像数据,并传送至该显示面板。

7.在本发明的另一个实施例中,公开了一种应用于显示面板的控制方法,其包含有以下步骤:接收影像数据,其中该影像数据具有不固定的帧速率;根据该影像数据的帧速率来将该影像数据进行倍频操作以产生输出影像数据,其中该输出影像数据的帧速率为该影像数据的正整数倍;以及将该输出影像数据传送至该显示面板。

附图说明

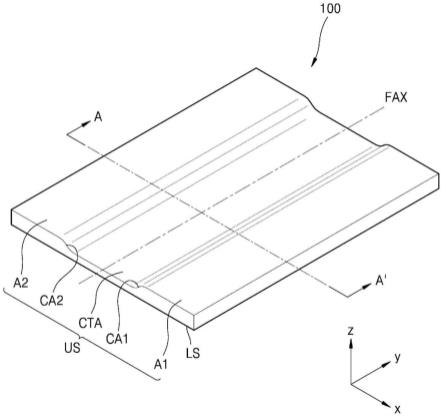

8.图1为根据本发明一个实施例的电子装置的示意图。

9.图2为根据本发明一个实施例的控制电路的操作时序图。

10.图3为根据本发明另一实施例的控制电路的操作时序图。

11.图4为根据本发明另一实施例的控制电路的操作时序图。

12.图5为根据本发明另一实施例的控制电路的操作时序图。

13.图6为根据本发明另一实施例的控制电路的操作时序图。

14.图7为根据本发明另一实施例的控制电路的操作时序图。

15.图8为根据本发明另一实施例的控制电路的操作时序图。

具体实施方式

16.图1为根据本发明一个实施例的电子装置100的示意图。如图1所示,电子装置100包含影像产生电路110、控制电路120以及显示面板130。在本实施例中,影像产生电路110可以是图形处理器(graphics processing unit,gpu),其用来产生影像数据din,而所产生的影像数据din的格式是符合显示端口(displayport,dp)或是高清晰度多媒体接口(high definition multimedia interface,hdmi)的规格,但本发明并不以此为限。控制电路120包含接收接口122、影像处理电路124、传送接口126以及背光控制电路128,其中接收接口122用来接收来自影像产生电路110的影像数据din后传送至影像处理电路124进行影像处理,而影像处理电路124可以将所接收到的影像数据din进行亮度、色彩、帧速率/更新率、或其他格式上的调整之后产生输出影像数据dout至传送接口126,以供传送至显示面板130进行显示;此外,背光控制电路128用来产生控制信号vc以控制显示面板130的亮度,其中控制信号vc可以是脉冲调制(pulse-width modulation,pwm)信号。在本实施例中,输出影像数据dout可以是任何规格的面板信号,例如低电压差分信号(low voltage differential signaling,lvds)、v-by-one、嵌入式显示端口(embedded display port,edp)

…

等等。显示面板130是液晶显示面板,而显示面板130包含时序控制器132、门驱动器133、源驱动器134、像素阵列136以及背光模块138,其中时序控制器132接收来自控制电路120的输出影像数据dout后产生对应的门驱动信号及源驱动信号至门驱动器133与源驱动器134,以供控制像素阵列136显示出影像画面;此外,背光模块138接收控制信号vc以显示出对应的亮度。

17.图1所示的电子装置100是支持可变更新率(variable refresh rate)的显示方式,亦即控制电路120所产生的输出影像数据dout的帧速率会随着图形处理器110产生影像数据din的帧速率而跟着变化。在一示例中,由于影像产生电路110产生每一个帧的时间并不固定,因此,控制电路120会被设计以支持一个较大的帧速率范围,例如48hz~144hz或是更高的240hz,以让使用者可以感受到影像画面具有较佳的流程度。然而,虽然控制电路120可以支持较大的帧速率,但一般来说影像产生电路110所输出的影像数据din的帧速率通常还是会在60hz左右,因此,本实施例提出了一种控制方法,其可以在影像产生电路110所输出的影像数据din的帧速率稳定低于控制电路120所支持的帧速率的情形下,采用倍频的方式来调整影像数据din的帧速率以产生输出影像数据dout,以改善现有技术中所述的动态模糊的问题。具体实施方式如下所述。

18.图2为根据本发明一个实施例的控制电路120的操作时序图。参考图2所示,假设影

像产生电路110所产生的影像数据din的帧速率为

‘

f’(单位可为每秒帧数(frame per second,fps)或是赫兹(hz))、则控制电路120在接收到影像数据din之后,其中的影像处理电路124可以直接将影像数据din进行二倍频处理,亦即输出影像数据dout的帧速率为

‘

2*f’(亦即,输出影像数据dout的相邻两个垂直同步信号vsync的时间差为影像数据din的相邻两个垂直同步信号vsync的时间差的一半);或是影像处理电路124可以直接将影像数据din进行三倍频处理,亦即输出影像数据dout的帧速率为

‘

3*f’(亦即,输出影像数据dout的相邻两个垂直同步信号vsync的时间差为影像数据din的相邻两个垂直同步信号vsync的时间差的三分之一);或是影像处理电路124可以直接将影像数据din进行n倍频处理,n为任意适合的正整数,只要输出影像数据dout的帧速率低于控制电路120及显示面板130所支持的最高帧速率即可。

19.在图2的实施例中,影像处理电路124在进行倍频操作时直接将影像数据进行复制,举例来说,以二倍频为例,当接收到帧f1时,影像处理电路124直接将帧f1中对应到主动区域的内容传送两次至显示面板130,以使得输出影像数据dout包含了两个帧f1’(倍频后帧),其中每一个帧f1’的主动区域的内容(亦即,显示在像素阵列136的部分)相同于帧f1的主动区域的内容;同理,当接收到帧f2时,影像处理电路124直接将帧f2中对应到主动区域的内容传送两次至显示面板130,以使得输出影像数据dout包含两个帧f2’(倍频后帧),其中每一个帧f2’的主动区域的内容相同于帧f2的主动区域的内容。另外,以三倍频为例,当接收到帧f1时,影像处理电路124直接将帧f1的主动区域的内容传送三次至显示面板130,以使得输出影像数据dout包含了三个帧f1”(倍频后帧),其中每一个帧f1”的主动区域的内容相同于帧f1的主动区域的内容;同理,当接收到帧f2时,影像处理电路124也直接将帧f2的主动区域的内容传送三次至显示面板130,以使得输出影像数据dout包含三个帧f3”(倍频后帧)。在本实施例的控制方法中,通过直接将影像数据din进行倍频处理以产生输出影像数据dout,而由于一般来说像素阵列136中的像素会因为液晶的反应速度而无法一次地到达所需的亮度(亦即,像素内的像素电极无法在一个周期内直接到达所需的目标电压电平),因此,通过直接对影像数据din进行倍频以多次地驱动像素电极至同一个目标电压电平,可以让显示面板130的颜色/亮度更为准确。

20.此外,在一个实施例中,对影像数据din进行倍频以产生输出影像数据dout的操作可以通过减少前肩区域(front porch)的内容(可参考图6)、或是改变用来传送输出影像数据dout的时钟信号的频率来完成。

21.图3为根据本发明另一实施例的控制电路120的操作时序图,其中图3以二倍频为例来进行说明,但本发明并不以此为限。参考图3,假设影像产生电路110所产生的影像数据din依序包含帧f1~f5,其中帧f1~f5的帧速率分别为48hz、48hz、60hz、60hz、48hz,则影像处理电路124可以直接将影像数据din进行二倍频处理,亦即输出影像数据dout依序包含帧f1’(96hz)、f1’(96hz)、f2’(96hz)、f2’(96hz)、f3’(120hz)、f3’(120hz)、f4’(120hz)、f4’(120hz)、f5’(96hz)、f5’(96hz)。通过本实施例的控制方法,可以在影像数据din的帧速率不固定的情形下,动态地根据影像数据din的帧速率来产生输出影像数据dout

22.图4为根据本发明另一实施例的控制电路120的操作时序图,其中图4以二倍频为例来进行说明,但本发明并不以此为限。参考图4,假设影像产生电路110所产生的影像数据din依序包含帧f1~f5,其中帧f1~f5的帧速率分别为48hz、48hz、60hz、60hz、48hz,则影像

处理电路124将影像数据din进行二倍频处理并进行插入黑画面的操作,亦即输出影像数据dout依序包含了黑画面(96hz)、f1’(96hz)、黑画面(96hz)、f2’(96hz)、黑画面(120hz)、f3’(120hz)、黑画面(120hz)、f4’(120hz)、黑画面(96hz)、f5’(96hz)。通过本实施例的控制方法,可以在影像数据din的帧速率不固定的情形下,动态地根据影像数据din的帧速率来产生输出影像数据dout,且对重复的帧进行插入黑画面的操作,以减少视觉暂留所造成的动态模糊。

23.需注意的是,图4所述的黑画面并不一定是全黑的画面,只要黑画面的亮度远低于帧f1~f5的亮度即可。

24.在一个实施例中,如果影像处理电路124将一帧进行n倍频处理并进行插入黑画面的操作以产生n个倍频后帧,而n为大于一的任意正整数,则该n个倍频后帧中的第一个倍频后帧为黑画面,且该n个倍频后帧中的最后一个倍频后帧的主动区域的内容相同于该帧的主动区域的内容。

25.图5为根据本发明另一实施例的控制电路120的操作时序图,其中图5以二倍频为例来进行说明,但本发明并不以此为限。参考图5,假设影像产生电路110所产生的影像数据din依序包含帧f1~f5,其中帧f1~f5的帧速率分别为48hz、48hz、60hz、60hz、48hz,则影像处理电路124可以直接将影像数据din进行二倍频处理,亦即输出影像数据dout依序包含帧f1’(96hz)、f1’(96hz)、f2’(96hz)、f2’(96hz)、f3’(120hz)、f3’(120hz)、f4’(120hz)、f4’(120hz)、f5’(96hz)、f5’(96hz)。此外,控制电路120中的背光控制模块128会产生控制信号vc以针对不同的帧采用第一背光模式或是第二背光模式,其中第一背光模式为完全地关闭背光模块138或是控制背光模块138产生很低的亮度、而第二背光模式为正常的亮度。具体来说,当显示面板130显示第一次出现的帧f1’时,背光控制模块128会产生控制信号vc以使得背光模块138操作在第一背光模式,亦即第一次出现的帧f1’可以视为黑画面;而当显示面板130显示第二次出现的帧f1’时,背光控制模块128会产生控制信号vc以使得背光模块138操作在第二背光模式,亦即显示面板130正常显示第二次出现的帧f1’。基于相同的操作,当显示面板130显示第一次出现的帧f2’、f3’、f4’、f5’时,背光控制模块128会产生控制信号vc以使得背光模块138操作在第一背光模式,亦即第一次出现的帧f2’、f3’、f4’、f5’可以视为黑画面;而当显示面板130显示第二次出现的帧f2’、f3’、f4’、f5’时,背光控制模块128会产生控制信号vc以使得背光模块138操作在第二背光模式,亦即显示面板130正常显示第二次出现的帧f2’、f3’、f4’、f5’。

26.在一个实施例中,如果影像处理电路124将一帧进行n倍频处理并进行插入黑画面的操作以产生n个倍频后帧,而n为大于一的任意正整数,则当传送接口126传送该n个倍频后帧中的第一个倍频后帧至显示面板130时,背光控制模块128产生控制信号vc以控制背光模块137操作在第一背光模式;以及当传送接口126传送该n个倍频后帧中的最后一个倍频后帧至显示面板130时,背光控制模块128产生控制信号vc以控制背光模块138操作在第二背光模式。

27.在一个实施例中,图5所示的背光控制方法可以是频闪背光(strobe backlight)控制方法,具体来说,参考图6所示,每一个完整的帧依序包含垂直同步信号vsync、后肩(back porch,bp)区域、主动区域(亦即,显示在像素阵列136上的内容)以及前肩(front porch,fp)区域,而在显示面板130显示第一次出现的帧f1’时,背光控制模块128会产生控

制信号vc以使得背光模块138的亮度为0或是很低的亮度,以使得第一次出现的帧f1’可以视为黑画面;接着,在显示面板130显示第二次出现的帧f1’时,背光控制模块128会产生控制信号vc以使得背光模块138在显示面板130的像素阵列136完全接收到第二次出现的帧f1’的驱动信号之后,才会控制背光模块138短暂地产生亮度以供显示面板130显示第二次出现的帧f1’。

28.图7为根据本发明另一实施例的控制电路120的操作时序图,其中图7以二倍频为例来进行说明,但本发明并不以此为限。参考图7,首先,在传送帧f1之前,影像产生电路110会先通知控制电路120接下来要传送的帧f1的帧速率,例如48hz,以供控制电路120设定目前的帧速率(亦即,96hz),而在经过一段内部操作的延迟时间之后,控制电路120内的影像处理电路124依序输出两个帧速率为96hz的帧f1’。由于帧f2的帧速率与帧f1的帧速率相同,故影像产生电路110不会通知控制电路120接下来要传送的帧f2的帧速率,而影像处理电路124便持续使用先前的帧速率(亦即,96hz),以依序输出两个帧速率为96hz的帧f2’。接着,在传送帧f3之前,影像产生电路110会先通知控制电路120接下来要传送的帧f3的帧速率,例如60hz,以供控制电路120设定目前的帧速率(亦即,120hz),而在经过一段内部操作的延迟时间之后,控制电路120内的影像处理电路124依序输出两个帧速率为120hz的帧f3’。由于帧f4的帧速率与帧f3的帧速率相同,故影像产生电路110则不会通知控制电路120接下来要传送的帧f4的帧速率,而影像处理电路124便持续使用先前的帧速率(亦即,120hz),以依序输出两个帧速率为120hz的帧f4’。接着,在传送帧f5之前,影像产生电路110会先通知控制电路120接下来要传送的帧f5的帧速率,例如48hz,以供控制电路120设定目前的帧速率(亦即,96hz),而在经过一段内部操作的延迟时间之后,控制电路120内的影像处理电路124依序输出两个帧速率为120hz的帧f5’。

29.在图7的实施例中,影像产生电路110只有在所产生的帧的帧速率有变化的时候才会通知控制电路120,然而,该特征并非是本发明的限制。在其他的实施例中,影像产生电路110可以在传送每一个帧前都先通知控制电路120接下来要传送的帧的帧速率,这些设计上的变化应隶属于本发明的范围。

30.需注意的是,图7所示的实施例也可以应用图4、图5所示的插入黑画面的方法,亦即图7所示的输出影像数据dout中第一次出现的帧f1’~f5’被替换为如图4所示的黑画面,或是如图5所示,当显示面板130显示第一次出现的帧f1’~f5’时,背光控制模块128会产生控制信号vc以使得背光模块138操作在第一背光模式,亦即第一次出现的帧f1’~f5’可以视为黑画面;而当显示面板130显示第二次出现的帧f1’~f5’时,背光控制模块128会产生控制信号vc以使得背光模块138操作在第二背光模式,亦即显示面板130正常显示第二次出现的帧f1’~f5’。

31.图8为根据本发明另一实施例的控制电路120的操作时序图,其中图8以二倍频为例来进行说明,但本发明并不以此为限。参考图8,首先,影像产生电路110传送帧f1至控制电路120,而影像处理电路124将帧f1暂存至内部的缓冲器中,并等到帧f1完成传送之后(例如,接收到下一个垂直同步信号vsync),影像处理电路124开始量测帧f1的帧速率(例如,48hz)以供设定目前的帧速率(亦即,96hz),而在经过一段内部操作的延迟时间之后,控制电路120内的影像处理电路124依序输出两个帧速率为96hz的帧f1’。接着,影像产生电路110传送帧f2至控制电路120,而影像处理电路124将帧f2暂存至内部的缓冲器中,并等到帧

f2完成传送之后影像处理电路124开始量测帧f2的帧速率(例如,48hz)以供设定目前的帧速率(亦即,96hz),而在经过一段内部操作的延迟时间之后,控制电路120内的影像处理电路124依序输出两个帧速率为96hz的帧f2’。类似地,影像产生电路110传送帧f3至控制电路120,而影像处理电路124将帧f3暂存至内部的缓冲器中,并等到帧f3完成传送之后影像处理电路124开始量测帧f3的帧速率(例如,60hz)以供设定目前的帧速率(亦即,120hz),而在经过一段内部操作的延迟时间之后,控制电路120内的影像处理电路124依序输出两个帧速率为120hz的帧f3’。如上所述,基于类似的操作,影像处理电路124在完整接收到帧f4的内容之后再依序输出两个帧速率为120hz的帧f4,且在完整接收到帧f5的内容之后再依序输出两个帧速率为96hz的帧f5’。

32.需注意的是,图8所示的实施例也可以应用图4、图5所示的插入黑画面的方法,亦即图8所示的输出影像数据dout中第一次出现的帧f1’~f5’被替换为如图4所示的黑画面,或是如图5所示,当显示面板130显示第一次出现的帧f1’~f5’时,背光控制模块128会产生控制信号vc以使得背光模块138操作在第一背光模式,亦即第一次出现的帧f1’~f5’可以视为黑画面;而当显示面板130显示第二次出现的帧f1’~f5’时,背光控制模块128会产生控制信号vc以使得背光模块138操作在第二背光模式,亦即显示面板130正常显示第二次出现的帧f1’~f5’。

33.需注意的是,在以上的实施例中假设影像产生电路110所输出的影像数据din的帧速率稳定低于控制电路120所支持的帧速率,故采用倍频的方式来调整影像数据din的帧速率以产生输出影像数据dout,以改善现有技术中所述的动态模糊的问题。然而,如果影像处理电路124判断目前所接收的影像数据din不符倍频标准,例如影像数据din中有部分帧的帧速率接近或高于控制电路120所支持的帧速率的一半,则影像处理电路124可以停止上述的倍频操作,亦即输出影像数据dout的帧速率相同于影像数据din的帧速率。

34.简要归纳本发明,在本发明的应用于显示面板的控制电路及控制方法中,通过根据影像数据的帧速率来将影像数据进行倍频操作以产生输出影像数据,并再通过插入黑画面的操作,可以有效地降低液晶显示面板在显示上的动态拖影问题,以改善显示品质。

35.以上所述仅为本发明的较佳实施例,凡依本发明权利要求所做的等同变化与修改,都应属于本发明的涵盖范围。

36.附图标记说明:

37.100:电子装置

38.110:影像产生电路

39.120:控制电路

40.122:接收接口

41.124:影像处理电路

42.126:传送接口

43.128:背光控制模块

44.130:显示面板

45.132:时序控制器

46.133:门驱动器

47.134:源驱动器

48.136:像素阵列

49.138:背光模块

50.bp:后肩区域

51.fp:前肩区域

52.din:影像数据

53.dout:输出影像数据

54.f1~f5:帧

55.f1’~f5’:帧

56.f1”~f5”:帧

57.vc:控制信号

58.vsync:垂直同步信号

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。