技术特征:

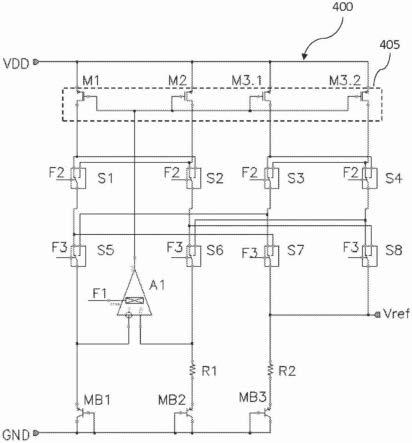

1.一种带隙参考电路,包括:第一电流镜,包括一对第一金属氧化物半导体场效应晶体管mosfet和第二mosfet;第二电流镜,包括第三mosfet,所述第三mosfet电连接到所述第一电流镜并被配置为在所述第三mosfet的漏极处提供参考电压;第一双极结型晶体管,电连接到所述第一电流镜;第二双极结型晶体管,经由第一电阻器电连接到所述第一电流镜;第三双极结型晶体管,经由第二电阻器电连接到所述第三mosfet;以及多个斩波开关,被配置为对所述第一电流镜和所述第二电流镜的输出执行斩波动作。2.根据权利要求1所述的带隙参考电路,还包括:运算放大器,具有第一输入和第二输入并具有输出,其中所述第一输入和所述第二输入中的每一个分别连接到所述第一双极结型晶体管和所述第二双极结型晶体管的发射极,并且所述输出分别连接到所述第一mosfet、所述第二mosfet和所述第三mosfet的栅极,其中所述运算放大器的所述第一输入和所述第二输入以第一频率被斩波。3.根据权利要求1所述的带隙参考电路,其中所述第一双极结型晶体管、所述第二双极结型晶体管和所述第三双极结型晶体管的集电极被电耦接以接地。4.根据权利要求1所述的带隙参考电路,还包括:第一开关,被配置为将所述第一mosfet和所述第二mosfet交替地电连接到所述第一双极结型晶体管;以及第二开关,被配置为将所述第一mosfet和所述第二mosfet交替地电连接到所述第一电阻器,其中当所述第一开关连接所述第一mosfet时,所述第二开关连接所述第二mosfet,并且当所述第一开关连接所述第二mosfet时,所述第二开关连接所述第一mosfet,其中所述第一开关和所述第二开关以第二频率操作。5.根据权利要求4所述的带隙参考电路,其中所述第二电流镜还包括第四mosfet,所述第四mosfet电连接到所述第一电流镜和所述第二电阻器。6.根据权利要求5所述的带隙参考电路,还包括:第三开关,被配置为将所述第三mosfet和所述第四mosfet二者择一地电连接到所述第二电阻器;以及第四开关,被配置为将所述第三mosfet或所述第四mosfet二者择一地电连接到所述第二电阻器,其中当所述第三开关连接所述第三mosfet时,所述第四开关连接所述第四mosfet,并且当所述第三开关连接所述第四mosfet时,所述第四开关连接所述第三mosfet,其中所述第三开关和所述第四开关以所述第二频率操作。7.根据权利要求6所述的带隙参考电路,还包括:第五开关,被配置为将所述第一开关和所述第三开关二者择一地连接到所述第一双极结型晶体管;第六开关,被配置为将所述第二开关和所述第四开关二者择一地连接到所述第一电阻器;

第七开关,被配置为将所述第一开关和所述第三开关二者择一地连接到所述第二电阻器;以及第八开关,被配置为将所述第二开关和所述第四开关二者择一地连接到所述第二电阻器,其中当所述第五开关连接所述第一开关时,所述第七开关连接所述第三开关,并且当所述第五开关连接所述第三开关时,所述第七开关连接所述第一开关,其中当所述第六开关连接所述第二开关时,所述第八开关连接所述第四开关,并且当所述第六开关连接所述第四开关时,所述第八开关连接所述第二开关,其中所述第五开关、所述第六开关、所述第七开关和所述第八开关被配置为以第三频率操作。8.根据权利要求7所述的带隙参考电路,根据权利要求2所述的带隙参考电路,其中所述第二频率的值能够等于所述第三频率的值乘以倍数,所述倍数是2的幂。9.根据权利要求1所述的带隙参考电路,还包括:第三电流镜,包括第五mosfet和第六mosfet,所述第三电流镜电连接到所述第一开关和所述第二开关,以及第四电流镜,包括第七mosfet和第八mosfet,所述第四电流镜电连接到所述第三开关和所述第四开关。10.根据权利要求2所述的带隙参考电路,还包括:第九mosfet,所述第九mosfet的栅极电连接到所述第一mosfet、所述第二mosfet、所述第三mosfet和所述第四mosfet的栅极,所述第九mosfet被配置为产生与绝对温度成比例ptat的输出参考电流。11.根据权利要求5所述的带隙参考电路,还包括:第一开关,被配置为在所述第一mosfet与所述第三mosfet之间二者择一地切换;第二开关,被配置为在所述第二mosfet与所述第四mosfet之间二者择一地切换;第三开关,被配置为在所述第一mosfet与所述第三mosfet之间二者择一地切换;以及第四开关,被配置为在所述第二mosfet与所述第四mosfet之间二者择一地切换,其中当所述第一开关连接所述第一mosfet时,所述第三开关连接所述第三mosfet,并且当所述第一开关连接所述第三mosfet时,所述第三开关连接所述第一mosfet,其中当所述第二开关连接所述第二mosfet时,所述第四开关连接所述第四mosfet,并且当所述第二开关连接所述第四mosfet时,所述第四开关连接所述第二mosfet,其中所述第一开关、所述第二开关、所述第三开关和所述第四开关以第四频率操作。12.根据权利要求11所述的带隙参考电路,还包括:第五开关,被配置为将所述第一开关和所述第二开关二者择一地电连接到所述第一双极结型晶体管;以及第六开关,被配置为将所述第一开关和所述第二开关二者择一地电连接到所述第一电阻器,其中当所述第五开关连接所述第一开关时,所述第六开关连接所述第二开关,并且当所述第五开关连接所述第一开关时,所述第六开关连接所述第二开关,其中所述第五开关和所述第六开关以第五频率操作。

13.一种带隙参考电路,包括:第一电流镜,包括一对第一金属氧化物半导体场效应晶体管mosfet和第二mosfet;第二电流镜,包括第三mosfet和第四mosfet,所述第三mosfet电连接到所述第一电流镜器件并被配置为提供参考电压,并且所述第四mosfet电连接到所述第一电流镜和第一电阻器;第一双极结型晶体管,电连接到所述第一电流镜;第二双极结型晶体管,经由所述第一电阻器电连接到所述第一电流镜;第三双极结型晶体管,经由第二电阻器电连接到所述第三mosfet;以及运算放大器,具有第一输入和第二输入并具有输出,其中所述第一输入和所述第二输入中的每一个分别连接到所述第一双极结型晶体管和所述第二双极结型晶体管的发射极,并且所述输出分别连接到所述第一mosfet、所述第二mosfet和所述第三mosfet的栅极,其中所述运算放大器的所述第一输入和所述第二输入以第一频率被斩波。14.根据权利要求13所述的带隙参考电路,还包括:第一开关,被配置为将所述第一mosfet和所述第二mosfet二者择一地电连接到所述第一双极结型晶体管;以及第二开关,被配置为将所述第一mosfet和所述第二mosfet二者择一地电连接到所述第一电阻器,其中当所述第一开关连接所述第一mosfet时,所述第二开关连接所述第二mosfet,并且当所述第一开关连接所述第二mosfet时,所述第二开关连接所述第一mosfet,其中所述第一开关和所述第二开关以第一频率操作。15.根据权利要求14所述的带隙参考电路,还包括:第三开关,被配置为将所述第三mosfet或所述第四mosfet二者择一地电连接到所述第二电阻器;以及第四开关,被配置为将所述第三mosfet或所述第四mosfet电连接到所述第二电阻器,其中所述第三开关连接所述第三mosfet,所述第四开关连接所述第四mosfet,并且所述第三开关连接所述第四mosfet,所述第四开关连接所述第三mosfet。16.根据权利要求15所述的带隙参考电路,还包括:第五开关,被配置为将所述第一开关或所述第三开关二者择一地连接到所述第一双极结型晶体管;第六开关,被配置为将所述第二开关或所述第四开关二者择一地连接到所述第一电阻器;第七开关,被配置为将第一开关或所述第三开关二者择一地连接到所述第二电阻器;以及第八开关,被配置为将所述第二开关或所述第四开关二者择一地连接到所述第二电阻器,其中当所述第五开关连接所述第一开关时,所述第七开关连接所述第三开关,并且所述第五开关连接所述第三开关,所述第七开关连接所述第一开关,其中当所述第六开关连接所述第二开关时,所述八开关连接所述第四开关,并且所述第六开关连接所述第四开关,所述第七开关连接所述第二开关,

其中所述第五开关、所述第六开关、所述第七开关和所述八开关被配置为以第二频率操作。17.根据权利要求16所述的带隙参考电路,根据权利要求2所述的带隙参考电路,其中所述第二频率的值能够等于所述第三频率的值乘以倍数,所述倍数是2的幂。18.根据权利要求14所述的带隙参考电路,还包括:第五mosfet,所述第五mosfet的栅极电连接到所述第一mosfet、所述第二mosfet、所述第三mosfet和所述第四mosfet的栅极,所述第五mosfet被配置为产生与绝对温度成比例ptat的输出参考电流。19.根据权利要求13所述的带隙参考电路,还包括:第一开关,被配置为在所述第一mosfet与所述第三mosfet之间二者择一地切换;第二开关,被配置为在所述第二mosfet与所述第四mosfet之间二者择一地切换;第三开关,被配置为在所述第一mosfet与所述第三mosfet之间二者择一地切换;以及第四开关,被配置为在所述第二mosfet与所述第四mosfet之间二者择一地切换,第五开关,被配置为将所述第一开关和所述第二开关二者择一地电连接到所述第一双极结型晶体管;以及第六开关,被配置为将所述第一开关和所述第二开关二者择一地电连接到所述第一电阻器,其中当所述第一开关连接所述第一mosfet时,所述第三开关连接所述第三mosfet,并且当所述第一开关连接所述第三mosfet时,所述第三开关连接所述第一mosfet,其中当所述第二开关连接所述第二mosfet时,所述第四开关连接所述第四mosfet,并且当所述第二开关连接所述第四mosfet时,所述第四开关连接所述第二mosfet,其中当所述第五开关连接所述第一开关时,所述第六开关连接所述第二开关,并且当所述第五开关连接所述第一开关时,所述第六开关连接所述第二开关,其中所述第一开关、所述第二开关、所述第三开关和所述第四开关以第四频率操作,其中所述第五开关和所述第六开关以第五频率操作。20.一种带隙参考电路,包括:第一电流镜器件,包括一对第一金属氧化物半导体场效应晶体管mosfet和第二mosfet;第二电流镜,包括第三mosfet和第四mosfet,所述第三mosfet电连接到所述第一电流镜器件并被配置为提供参考电压,并且所述第四mosfet电连接到所述第一电流镜和第一电阻器;第一双极结型晶体管,电连接到所述第一电流镜器件;第二双极结型晶体管,经由第二电阻器电连接到所述第一电流镜器件;第三双极结型晶体管,经由第三电阻器电连接到所述第三mosfet;第一开关,被配置为在所述第一mosfet与所述第三mosfet之间二者择一地切换;第二开关,被配置为在所述第二mosfet与所述第四mosfet之间二者择一地切换;第三开关,被配置为在所述第一mosfet与所述第三mosfet之间二者择一地切换;第四开关,被配置为在所述第二mosfet与所述第四mosfet之间二者择一地切换;第五开关,被配置为将所述第一开关或所述第二开关二者择一地电连接到所述第一双

极结型晶体管;以及第六开关,被配置为将所述第一开关或所述第二开关二者择一地电连接到所述第一电阻器,其中当所述第一开关连接所述第一mosfet时,所述第三开关连接所述第三mosfet,并且当所述第一开关连接所述第三mosfet时,所述第三开关连接所述第一mosfet,其中当所述第二开关连接所述第二mosfet时,所述第四开关连接所述第四mosfet,并且当所述第二开关连接所述第四mosfet时,所述第四开关连接所述第二mosfet,其中当所述第五开关连接所述第一开关时,所述第六开关连接所述第二开关,并且当所述第五开关连接所述第二开关时,所述第六开关连接所述第一mosfet。

技术总结

本公开提供了带隙参考电路,该带隙参考电路为了降低输出参考电压的闪烁噪声而对电流镜电路具有多级斩波动作。带隙参考电路包括:第一电流镜,包括一对第一MOSFET和第二MOSFET;第二电流镜,包括第三MOSFET,该第三MOSFET电连接到第一电流镜并被配置为在漏极处提供参考电压;第一双极结型晶体管,电连接到第一电流镜;第二双极结型晶体管,经由第一电阻器连接到第一电流镜;以及第三双极结型晶体管,经由第二电阻器连接到第三MOSFET。该带隙参考电路还包括用于控制MOSFET的运算放大器、以及被配置为对第一电流镜和第二电流镜的输出执行斩波动作的多个斩波开关。输出执行斩波动作的多个斩波开关。输出执行斩波动作的多个斩波开关。

技术研发人员:E

受保护的技术使用者:松下知识产权经营株式会社

技术研发日:2021.01.06

技术公布日:2022/8/26

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。