1.本发明涉及设有光电变换部的半导体装置及该半导体装置的制造方法。

背景技术:

2.作为在微弱的光子环境下有效的光电二极管,已知有雪崩光电二极管(avalanche photodiode:apd)(例如,参照专利文献1)。

3.在专利文献1中公开的作为光电变换部的一例的apd通过将在光吸收区域中产生的载流子在雪崩增倍区域中增倍,在微弱的光子环境下也能够检测光。此外,专利文献1中公开的apd为了使聚光效率提高,在形成有光吸收区域的硅基板的表面具备抑制入射光的反射的防反射膜。

4.现有技术文献

5.专利文献

6.专利文献1:日本特许第4131191号公报

技术实现要素:

7.发明要解决的课题

8.本发明提供能够提高聚光效率并且能够抑制暗电流的产生的半导体装置等。

9.用来解决课题的手段

10.本发明的一技术方案的半导体装置,具备:硅半导体基板,具有设有光电变换部的第1区域及与上述第1区域不同的第2区域;晶体管,设于上述第2区域,在侧部具有由绝缘材料构成的侧壁;防反射膜,设在上述第1区域中的上述硅半导体基板的主面上,由上述绝缘材料构成;以及第1衬膜,设在上述第2区域中的上述硅半导体基板的主面上,由上述绝缘材料构成;上述防反射膜和上述第1衬膜一体地形成;上述防反射膜的膜厚是上述侧壁的膜厚与上述第1衬膜的膜厚的和以上。

11.此外,本发明的一技术方案的半导体装置的制造方法,包括:光电变换部形成工序,在硅半导体基板中的第1区域形成光电变换部;电极形成工序,在上述硅半导体基板中的与上述第1区域不同的第2区域形成晶体管具有的栅极电极;第1成膜工序,通过在上述硅半导体基板的主面上沉积绝缘材料而成膜出绝缘膜;蚀刻工序,通过将上述绝缘膜蚀刻,在上述栅极电极的侧部形成由上述绝缘材料构成的侧壁;以及第2成膜工序,通过在上述硅半导体基板的主面上进一步沉积上述绝缘材料,成膜出设在上述第1区域中的上述硅半导体基板的主面上且由上述绝缘材料构成的防反射膜、以及设在上述第2区域中的上述硅半导体基板的主面上且由上述绝缘材料构成的第1衬膜。

12.发明效果

13.根据本发明,能够提供能够提高聚光效率并且能够抑制暗电流的产生的半导体装置等。

附图说明

14.图1是表示实施方式的半导体装置的剖视图。

15.图2a是用来说明实施方式的半导体装置的制造方法的剖视图。

16.图2b是用来说明实施方式的半导体装置的制造方法的剖视图。

17.图2c是用来说明实施方式的半导体装置的制造方法的剖视图。

18.图2d是用来说明实施方式的半导体装置的制造方法的剖视图。

19.图2e是用来说明实施方式的半导体装置的制造方法的剖视图。

20.图3a是用来说明比较例的半导体装置的制造方法的剖视图。

21.图3b是用来说明比较例的半导体装置的制造方法的剖视图。

具体实施方式

22.以下,参照附图对本发明的实施方式进行说明。另外,以下说明的实施方式都表示总括性或具体性的例子。在以下实施方式中表示的数值、形状、材料、构成要素、构成要素的配置位置及连接形态等作为一例而并不意欲限定本发明。此外,关于以下实施方式的构成要素中的、在表示本发明的最上位概念的独立权利要求中没有记载的构成要素,设为任意的构成要素进行说明。此外,本发明的实现形态并不由现有独立权利要求限定,也可以由其他独立权利要求表现。

23.另外,各图是示意图,并不一定严格地图示。此外,在各图中,对于实质上相同的结构赋予相同的标号,有将重复的说明省略或简化的情况。

24.此外,在本说明书中,“上方(上)”及“下方(下)”的用语不是指绝对空间识别中的上方(铅直上方)及下方(铅直下方),而是作为基于层叠结构中的层叠顺序由相对位置关系规定的用语来使用。此外,“上方”及“下方”的用语不仅能够应用于将两个构成要素相互隔开间隔配置而在两个构成要素之间存在其他构成要素的情况,还能够应用于两个构成要素相互密接配置从而两个构成要素相接的情况。

25.此外,在以下实施方式中用于说明的附图中,有示出坐标轴的情况。坐标轴的z轴方向例如是层叠方向及铅直方向,有将z轴正方向(侧)表现为上方(上侧)、将z轴负方向(侧)表现为下方(下侧)的情况。z轴方向换言之是与形成光电变换部的半导体基板的主面(形成聚光部的一侧的面)垂直的方向,也表现为层叠方向。此外,x轴方向及y轴方向是在与z轴方向垂直的平面(例如水平面)上相互正交的方向。

26.此外,在以下的实施方式中,“平面观察”是指从z轴方向观察半导体装置。

27.此外,本发明并不排除使在以下实施方式中说明的导电型反转了的构造。具体而言,以下说明的p型和n型都可以相反。

28.(实施方式)

29.[构造]

[0030]

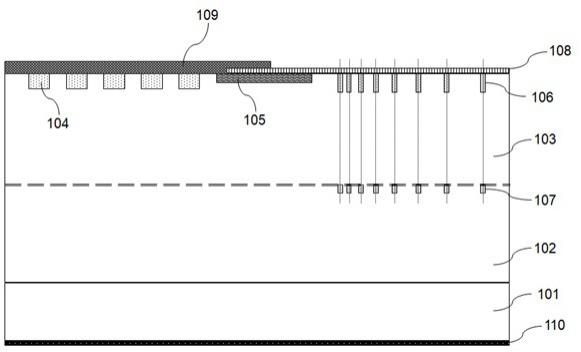

图1是表示实施方式的半导体装置100的剖视图。

[0031]

半导体装置100是检测所入射的光的光检测器。

[0032]

半导体装置100具备半导体基板(硅半导体基板)110、晶体管160、底层氧化膜130、防反射膜151、第1衬膜(liner film)152、第2衬膜153和滤色器170。

[0033]

半导体基板110是形成apd(光电变换部)111等光电变换区域的硅半导体基板。半

导体基板110具备像素区域(第1区域)200、逻辑区域(第2区域)210和其他区域(第3区域)220。另外,像素区域200、逻辑区域210和其他区域220是在半导体基板110中相互不同的区域。

[0034]

像素区域200是设置apd111的区域。在像素区域200中,在半导体基板110的主面112上具备底层氧化膜130和防反射膜151。

[0035]

另外,在本实施方式中,主面112上是指比主面112靠z轴正方向侧,是指与主面112相接的情况及不与主面112相接的情况中的任意情况。

[0036]

apd111是对入射的光进行光电变换的光电变换部。apd111例如是具有使通过光电变换生成的电子雪崩增倍的雪崩增倍区域的雪崩光电二极管。另外,apd111也可以是不具有雪崩增倍区域的光电二极管(photodiode/pd)。

[0037]

此外,在本实施方式中,apd111对波长为650nm以上的光进行光电变换。例如,选择半导体基板110的材料,以使apd111对波长为650nm以上的光进行光电变换。在本实施方式中,半导体基板110是硅半导体基板,从而apd111将波长为650nm以上的光吸收并进行光电变换。

[0038]

底层氧化膜130是与主面112相接而配置于半导体基板110的膜。底层氧化膜130例如是硅氧化膜。

[0039]

防反射膜151是用来防止(抑制)向apd111入射的光在主面112反射的膜。防反射膜151是由绝缘材料形成的膜。绝缘材料是具有电绝缘性的材料。绝缘材料例如是氮化物。即,防反射膜151例如是由氮化物形成的膜(氮化膜)。具体而言,例如防反射膜151是硅氮化膜。防反射膜151设在像素区域200中的半导体基板110的主面112上、即像素区域200的上方。

[0040]

防反射膜151的膜厚a根据抑制反射的光的波长而设定。防反射膜151的膜厚a例如是70nm以上。由此,防反射膜151难以反射例如波长为650nm以上的光。

[0041]

逻辑区域210是设置晶体管160的区域。在本实施方式中,在逻辑区域210中设有晶体管160和第1衬膜152。

[0042]

晶体管160是设于逻辑区域210的晶体管。另外,晶体管160具有的设于半导体基板110的源极及漏极等构成要素的图示省略。晶体管160例如被用于转送晶体管、复位晶体管、或用来将由光电变换部111生成的电子读出的逻辑电路的晶体管等。

[0043]

晶体管160具备栅极绝缘膜120、栅极电极121、底层氧化膜131和侧壁140。

[0044]

栅极绝缘膜120是晶体管160的栅极绝缘膜。

[0045]

栅极电极121是晶体管160的栅极电极。栅极电极121例如是多晶硅。

[0046]

底层氧化膜131是用来形成侧壁140的膜。底层氧化膜131由与底层氧化膜130相同的材料形成。

[0047]

侧壁140配置在晶体管160(更具体地讲,栅极电极121)的侧部,是用来将晶体管160(更具体地讲,栅极电极121)从侧方支承的膜。即,晶体管160(更具体地讲,栅极电极121)设在逻辑区域210中,在侧部具有由绝缘材料构成的侧壁140。侧壁140由与防反射膜151及第1衬膜152相同的材料(绝缘材料)构成。

[0048]

第1衬膜152是当在半导体基板110中形成未图示的布线时用来止住蚀刻的所谓衬垫(liner)用的膜。第1衬膜152由与防反射膜151相同的绝缘材料形成,例如是氮化膜。第1衬膜152设在逻辑区域210中的半导体基板110的主面112上、即逻辑区域210的上方。具体而

言,第1衬膜152与晶体管160及半导体基板110的主面112相接而成膜。

[0049]

在本实施方式中,第1衬膜152和防反射膜151一体地形成。换言之,防反射膜151和第1衬膜152作为1个膜(绝缘膜150)形成在半导体基板110的主面112上。

[0050]

绝缘膜150是被成膜在半导体基板110的主面112上的膜。绝缘膜150例如是氮化膜。

[0051]

其他区域220是半导体基板110中既非像素区域200也非逻辑区域210的区域,换言之,是没有设置晶体管及apd等光电变换部的区域。在其他区域220中的半导体基板110的主面112,形成有由上述绝缘材料构成的第2衬膜153。另外,在其他区域220中,例如不仅不形成与晶体管160相同种类的晶体管,也不形成不同种类的晶体管。例如,即使在晶体管160是转送晶体管的情况下,在其他区域220中,也不仅不形成转送晶体管,也不形成复位晶体管等晶体管。

[0052]

第2衬膜153是当在半导体基板110中形成未图示的布线时用来止住蚀刻的所谓衬垫用的膜。第2衬膜153由与防反射膜151及第1衬膜152相同的绝缘材料形成,例如是氮化膜。第2衬膜153与半导体基板110的主面112相接而成膜。

[0053]

此外,第2衬膜153与第1衬膜152及防反射膜151一体地形成。换言之,防反射膜151、第1衬膜152和第2衬膜153作为1个膜(绝缘膜150)形成在半导体基板110的主面112上。

[0054]

此外,第1衬膜152和第2衬膜153膜厚相同。

[0055]

这里,关于防反射膜151的膜厚a(在本实施方式中是z轴方向的宽度)、侧壁140的膜厚b(在本实施方式中是x轴方向的宽度)和第1衬膜152(及第2衬膜153)的膜厚c(在本实施方式中是z轴方向的宽度),以下的式(1)所示的关系成立。

[0056]

膜厚a≧膜厚b 膜厚c式(1)

[0057]

即,防反射膜151的膜厚a为侧壁140的膜厚b与第1衬膜152的膜厚c的和以上。

[0058]

另外,也可以是,式(1)的左边包括底层氧化膜131的膜厚(在本实施方式中是x轴方向的宽度),并且,式(1)的右边包括底层氧化膜130的膜厚(在本实施方式中是z轴方向的宽度)。

[0059]

此外,侧壁140的膜厚b例如可以是剖视下的底层氧化膜131的x轴方向的最长部位的宽度、与位于侧壁140和栅极电极121之间的底层氧化膜131的x轴方向的长度之差。

[0060]

滤色器170与半导体基板110的主面112对置而配置,是将向apd111入射的光的一部分遮光的滤光器。滤色器170例如载置在层叠于防反射膜151的未图示的层中。或者,滤色器170也可以被半导体装置100具备的未图示的壳体支承而配置在apd111上。或者,滤色器170也可以载置于防反射膜151。滤色器170例如将波长小于650nm的光遮光,并且使波长为650nm以上的光透射。

[0061]

[制造工序]

[0062]

《实施例》

[0063]

接着,详细地说明半导体装置100的制造方法。

[0064]

图2a~图2e是用来说明实施方式的半导体装置100的制造方法的剖视图。

[0065]

首先,在半导体基板110的像素区域200中形成apd111(光电变换部形成工序)。例如,如图2a所示,在含有硼的p型的半导体基板110中,在像素区域200中以与半导体基板110的主面112相接的方式形成apd111。为了形成apd111,例如向半导体基板110以2000kev(剂

量:2e12cm

-2

)、1000kev(剂量:4e12cm

-2

)、500kev(剂量:6e12cm

-2

)及100kev(剂量:1e13cm

-2

)依次将as多级注入。通过n型的as和半导体基板110中包含的p型的硼而形成apd111。

[0066]

接着,在半导体基板110的逻辑区域210中,形成晶体管160具有的栅极电极121(电极形成工序)。具体而言,如图2b所示,在逻辑区域210中的半导体基板110的主面112,形成膜厚5nm的栅极绝缘膜120。此外,在栅极绝缘膜120的上表面形成膜厚140nm的由多晶硅构成的栅极电极121。

[0067]

接着,在半导体基板110的主面112上沉积绝缘材料而将绝缘膜310成膜(第1成膜工序)。具体而言,如图2c所示,在半导体基板110的主面112上将底层氧化膜300以20nm成膜。此外,在半导体基板110的主面112上(更具体地讲,底层氧化膜300的上表面)沉积绝缘材料(例如氮化物)从而将绝缘膜310以60nm成膜。

[0068]

接着,将绝缘膜310蚀刻,从而在栅极电极121的侧部形成由上述绝缘材料构成的侧壁140(蚀刻工序)。具体而言,如图2d所示,在通过光刻技术在像素区域200中形成(配置)了抗蚀剂掩模400后,进行蚀刻(侧壁蚀刻)而在逻辑区域210的栅极电极121的侧部(侧面)隔着底层氧化膜131形成侧壁140。例如,抗蚀剂掩模400利用光刻将涂布在绝缘膜310上的抗蚀剂图案化而形成。由此,在逻辑区域210中,形成晶体管160具有的底层氧化膜131及侧壁140等构成要素。此外,在像素区域200中,在底层氧化膜130上形成绝缘膜310a。

[0069]

这里,在形成侧壁140的工序(蚀刻工序)中,由于像素区域200被抗蚀剂掩模400覆盖,所以不受到由侧壁蚀刻带来的等离子损伤。即,对于apd111,在蚀刻工序中不生成因制造工艺带来的缺陷。

[0070]

接着,如图2e所示,在半导体基板110的主面112上进一步沉积绝缘材料而将绝缘膜150成膜。具体而言,在半导体基板110的主面112上进一步沉积上述绝缘材料,从而成膜设在像素区域200中的半导体基板110的主面112上且由上述绝缘材料构成的防反射膜151、以及设在逻辑区域210中的半导体基板110的主面112上且由上述绝缘材料构成的第1衬膜152(第2成膜工序)。此外,在第2成膜工序中,进一步,在半导体基板110中,在没有设置晶体管及apd等光电变换部的其他区域220中的半导体基板110的主面112,形成由上述绝缘材料构成的第2衬膜153。

[0071]

由此,防反射膜151、第1衬膜152及第2衬膜153一体地形成在半导体基板110的主面112上。即,向在第1成膜工序中沉积的绝缘材料,进一步在第2成膜工序中沉积绝缘材料,从而成膜出防反射膜151。例如,在第2成膜工序中,第1衬膜152及第2衬膜153厚度相同而被成膜为15nm。

[0072]

另外,第1成膜工序、蚀刻工序及第2成膜工序被执行,以使防反射膜151的膜厚a成为侧壁140的膜厚b与第1衬膜152的膜厚c的和以上。

[0073]

此外,在第2成膜工序后,通过应用布线工艺而形成半导体基板110的布线,通过将滤色器170配置到半导体基板110上(更具体地讲,apd111上)(配置工序)而制造出半导体装置100。

[0074]

另外,虽然没有图示,但也可以在图2b所示的工序与图2c所示的工序之间,在晶体管160的栅极电极121的侧面形成由氧化膜构成的偏移间隔件(offset spacer)。偏移间隔件的膜厚没有特别限定,例如是15nm左右。

[0075]

此外,虽然在图2b~图2e中没有明示地图示,但在半导体基板110的主面112,还存

在当形成栅极绝缘膜120时残留的氧化膜(硅氧化膜)。

[0076]

根据以上这样的半导体装置100的制造方法,在像素区域200中的半导体基板110的主面112,氧化膜存在40nm左右,氮化膜存在75nm左右。因此,对于向像素区域200入射的例如940nm的近红外(infrared/ir)光,形成作为最佳的防反射膜151发挥功能的膜。

[0077]

《比较例》

[0078]

图3a及图3b是表示比较例的半导体装置100a的制造方法的图。另外,在以下的说明中,关于与实施例同样的顺序,有时将一部分说明简化或省略。

[0079]

在比较例的半导体装置100a的制造方法中,也与实施方式的半导体装置100的制造方法同样,首先,执行图2a~图2d所示的处理。

[0080]

具体而言,首先,如图2a所示,在包含硼的p型的半导体基板110中,在像素区域200中以与半导体基板110的主面112相接的方式形成apd111(光电变换部形成工序)。

[0081]

接着,如图2b所示,在逻辑区域210中的半导体基板110的主面112,形成栅极绝缘膜120。此外,在栅极绝缘膜120的上表面形成栅极电极121(电极形成工序)。

[0082]

接着,如图2c所示,通过在半导体基板110的主面112上沉积绝缘材料而将绝缘膜310成膜(第1成膜工序)。

[0083]

接着,如图2d所示,通过将绝缘膜310蚀刻,在栅极电极121的侧部形成由上述绝缘材料构成的侧壁140(蚀刻工序)。

[0084]

这里,在形成侧壁140的工序(蚀刻工序)中,像素区域200由于被抗蚀剂掩模400覆盖,所以不受到由侧壁蚀刻带来的等离子损伤。即,对于apd111,在蚀刻工序中不生成由制造工艺带来的缺陷。

[0085]

接着,如图3a所示,在形成了在俯视下在与像素区域200对应的部位形成有开口的抗蚀剂掩模410后,通过进行湿式蚀刻,使像素区域200的绝缘膜310a薄膜化从而形成绝缘膜310b(薄膜化工序)。例如,抗蚀剂掩模410通过光刻将涂布在主面112、绝缘膜310a、栅极电极121及侧壁140等之上的抗蚀剂图案化而形成。这样,在比较例的半导体装置100a的制造方法中,执行薄膜化工序。由此,形成比防反射膜151薄的膜厚的防反射膜151a。

[0086]

接着,如图3b所示,通过在半导体基板110的主面112上进一步沉积绝缘材料而成膜出绝缘膜150a。具体而言,通过在半导体基板110的主面112上进一步沉积上述绝缘材料,从而成膜出设在像素区域200中的半导体基板110的主面112上且由上述绝缘材料构成的防反射膜151a、以及设在逻辑区域210中的半导体基板110的主面112上且由上述绝缘材料构成的第1衬膜152(第2成膜工序)。此外,在第2成膜工序中,进一步,在半导体基板110中,在没有设置晶体管及apd等光电变换部的其他区域220中的半导体基板110的主面112,形成由上述绝缘材料构成的第2衬膜153。由此,在半导体基板110的主面112上一体地形成防反射膜151a、第1衬膜152及第2衬膜153。换言之,防反射膜151a、第1衬膜152和第2衬膜153作为1个膜(绝缘膜150a)形成在半导体基板110的主面112上。

[0087]

此外,在第2成膜工序后,通过应用布线工艺而形成半导体基板110的布线,通过将滤色器170配置到半导体基板110上(更具体地讲,apd111上)(配置工序),制造出半导体装置100a。

[0088]

另外,在半导体基板110的主面112,还存在当形成与侧壁140相接的底层氧化膜131、以及栅极绝缘膜120等时残留的、在图3a及图3b中没有明示地图示的氧化膜(硅氧化

膜)。

[0089]

如以上这样,在比较例的半导体装置100a的制造方法中执行薄膜化工序,而在实施例的半导体装置100的制造方法中不执行薄膜化工序。

[0090]

《作用》

[0091]

对于形成于像素区域200的防反射膜,利用实施例和比较例进行说明。

[0092]

在apd111中,通过入射光而发生该光的吸收,发生所吸收的光的光电变换。关于形成于像素区域200的膜(例如氮化膜),能够期待作为防止向像素区域200入射的光(入射光)的反射的膜的功能。即,在apd111的上部存在防反射膜151,从而能够防止向apd111入射的光的反射。因此,能够抑制半导体装置100的变换效率的下降。

[0093]

例如,考虑入射光是波长550nm的可见光的情况。在像素区域200的存在于半导体基板110的主面112上的硅氧化膜的膜厚是40nm的情况下,氮化膜作为防反射膜151发挥功能的最佳膜厚为30nm。

[0094]

另外,如上述那样,在半导体基板110的主面112,还存在当形成与侧壁140相接的底层氧化膜131、以及栅极绝缘膜120等时残留的没有明示地图示的氧化膜。

[0095]

此外,衬垫用的膜(第1衬膜152及第2衬膜153)是为了改善晶体管160的特性而用来向逻辑区域210导入应变、或者用来作为接触蚀刻(contact etching)时的蚀刻阻挡膜而发挥功能的膜。

[0096]

在衬垫用的膜的膜厚例如为15nm的情况下,为了形成作为最佳防反射膜发挥功能的30nm的膜,需要在将该衬垫用的膜成膜之前,使存在于像素区域200中的膜的膜厚成为15nm。

[0097]

侧壁140以膜厚b典型地是50nm程度而成膜。因此,例如通过执行图3a所示那样的绝缘膜的薄膜化工序,调整侧壁140的膜厚。在通过执行薄膜化工序而制造出的半导体装置100a中,关于防反射膜151a的膜厚a1、侧壁140的膜厚b、第1衬膜152的膜厚c,以下的关系成立,作为防止反射的膜(防反射膜151a),像素区域200的膜的膜厚a1成为最佳的膜厚。

[0098]

膜厚a1《膜厚b 膜厚c式(2)

[0099]

但是,在满足上述式(2)那样的半导体装置100a的制造方法中,与如满足上述式(1)那样制造的半导体装置100的制造方法相比,发生由图3a所示那样的追加工序带来的工艺成本的增大、以及伴随着防反射膜151a的完成膜厚的偏差的光学特性偏差。此外,由于在像素区域200中向半导体基板110导入了工艺损伤,所以所产生的暗电流有可能增大。

[0100]

因此,例如如图2a~图2e所示,在半导体装置100的制造方法中,不进行图3a所示的蚀刻(薄膜化工序),以满足上述式(1)的方式,在第1成膜工序和第2成膜工序中将相同的绝缘材料沉积而成膜。由此,能够制造出减小向apd111的工艺损伤、并且防反射膜151成为抑制入射光的反射的适当膜厚的半导体装置100。换言之,根据半导体装置100,向apd111入射的光量增加(即,能够提高聚光效率),并且能够抑制暗电流的发生。这里的聚光效率,例如对于向apd111照射的光的量,表示不被反射而入射到apd111中的光的量。

[0101]

另外,根据实施例的半导体装置的制造方法,膜厚a与膜厚b和膜厚c之和大致一致。换言之,执行蚀刻工序,以使绝缘膜310a的膜厚(z轴方向的宽度)与侧壁140的膜厚b大致一致。但是,在蚀刻工序中,有时被蚀刻为使得侧壁140的膜厚b比绝缘膜310a的膜厚(z轴方向的宽度)小。因此,如上述式(1)所示,防反射膜151的膜厚a成为侧壁140的膜厚b与第1

衬膜152的膜厚c的和以上。

[0102]

[效果等]

[0103]

如以上说明,实施方式的半导体装置100具备:半导体基板110,具有设有apd111的像素区域200及与像素区域200不同的逻辑区域210;晶体管160,设于逻辑区域210,在侧部具有由绝缘材料构成的侧壁140;防反射膜151,设在像素区域200中的半导体基板110的主面112上,由绝缘材料构成;以及第1衬膜152,设在逻辑区域210中的半导体基板110的主面112上,由绝缘材料构成。防反射膜151和第1衬膜152一体地形成。防反射膜151的膜厚a是侧壁140的膜厚b与第1衬膜152的膜厚c的和以上。

[0104]

如上述说明,通过不执行薄膜化工序地形成防反射膜151,防反射膜151的膜厚a成为侧壁140的膜厚b与第1衬膜152的膜厚c的和以上。换言之,防反射膜151的膜厚a是侧壁140的膜厚b与第1衬膜152的膜厚c的和以上的半导体装置100由于没有被执行薄膜化工序,所以在像素区域200中没有被导入用来形成防反射膜151的工艺损伤,能够抑制暗电流的发生。因此,由此半导体装置100因为具备防反射膜151而能够提高聚光效率,并且因为没有被执行薄膜化工序而能够抑制暗电流的发生。

[0105]

此外,例如,上述绝缘材料是氮化物。

[0106]

由此,能够使用以往的cmos(complementary metal oxide semiconductor)制造方法中的工艺,在半导体基板110上形成防止光的反射并且将防反射膜151和第1衬膜152一体化的1个膜(绝缘膜150)。即,能够通过以往的制造方法简便地制造防反射膜151。

[0107]

此外,例如,apd111对波长为650nm以上的光进行光电变换。

[0108]

例如,考虑将apd111用于对波长550nm的可见光进行光电变换的用途的情况。该情况下,作为防反射膜151发挥功能的最佳膜厚例如为30nm。这里,apd111进行光电变换的光的波长越长,防反射膜151发挥功能(即,将作为对象的光反射)的最佳膜厚越厚。例如,根据实施例的半导体装置100的制造方法,与比较例的半导体装置100a的制造方法相比,由于不进行薄膜化工序,所以防反射膜151变厚。因此,半导体装置100适合用于对长波长的光、例如波长为650nm以上的光进行光电变换。

[0109]

此外,例如,防反射膜151的膜厚是70nm以上。

[0110]

防反射膜151由于膜厚是70nm以上,例如难以将波长为650nm以上的光反射。因此,由此半导体装置100更适合用于对长波长的光、例如波长为650nm以上的光进行光电变换。

[0111]

此外,例如,半导体装置100还具备将波长小于650nm的光遮光的滤色器170。

[0112]

由此,半导体装置100例如在被用于对波长为650nm以上的光进行光电变换的情况下,能够精度良好地检测作为对象的波长的光。

[0113]

此外,例如,半导体基板110还具有不设置晶体管及apd等光电变换部的其他区域220。例如,在其他区域220中的半导体基板110的主面112,形成有由上述绝缘材料构成的第2衬膜153。防反射膜151、第1衬膜152和第2衬膜153一体地形成。第1衬膜152和第2衬膜153厚度相同。

[0114]

如上述那样,例如,根据实施例的半导体装置100的制造方法,防反射膜151、第1衬膜152和第2衬膜153一体地形成。此外,第1衬膜152和第2衬膜153由于以相同的工艺形成在半导体基板110的主面112,所以厚度相同。因此,防反射膜151、第1衬膜152和第2衬膜153一体地形成、并且第1衬膜152和第2衬膜153的厚度相同那样的半导体装置100能够利用以往

的cmos制造方法的工艺简便地制造。

[0115]

此外,实施方式的半导体装置100的制造方法,包括:光电变换部形成工序,在半导体基板110的像素区域200中形成apd111;电极形成工序,在半导体基板110的与像素区域200不同的逻辑区域210中形成晶体管160具有的栅极电极121;第1成膜工序,通过在半导体基板110的主面112上沉积绝缘材料而成膜出绝缘膜310;蚀刻工序,通过将绝缘膜310蚀刻,在栅极电极121的侧部形成由上述绝缘材料构成的侧壁140;以及第2成膜工序,通过在半导体基板110的主面112上进一步沉积上述绝缘材料,成膜出设在像素区域200中的半导体基板110的主面112上且由上述绝缘材料构成的防反射膜151、以及设在逻辑区域210中的半导体基板110的主面112上且由上述绝缘材料构成的第1衬膜152。

[0116]

由此,关于具备具有像素区域200和逻辑区域210的半导体基板110的半导体装置100,能够利用以往的cmos制造方法的工艺,不对像素区域200导入工艺损伤地制造抑制了暗电流的半导体装置100。进而,由于在像素区域200中存在对于入射光成为最佳膜厚的防反射膜151,所以聚光效率不下降。进而,由于不需要用来形成成为最佳膜厚的防反射膜151的追加工序,所以能够抑制工艺成本的增大。此外,抑制了伴随着防反射膜151的完成膜厚偏差的光学特性偏差的发生。换言之,根据实施方式的半导体装置的制造方法,能够制造向apd111入射的光量增加(即,能够提高聚光效率)并且抑制了暗电流的发生的半导体装置100。

[0117]

此外,例如,为了使防反射膜151的膜厚a为侧壁140的膜厚b与第1衬膜152的膜厚c的和以上,适当地设定第1成膜工序中的绝缘膜310的膜厚、以及蚀刻工序中的蚀刻速率等。

[0118]

由此,能够利用以往的cmos制造方法的工艺,在半导体基板110上形成防止光的反射并且防反射膜151和第1衬膜152一体化的1个膜(绝缘膜150)。

[0119]

此外,例如,执行第1成膜工序及第2成膜工序,以使防反射膜151的膜厚成为70nm以上。

[0120]

由此,防反射膜151膜厚是70nm以上,从而例如难以将波长为650nm以上的光反射。因此,由此半导体装置100更适合用于对长波长的光、例如波长为650nm以上的光进行光电变换。

[0121]

此外,例如,实施方式的半导体装置100的制造方法还包括配置将波长小于650nm的光遮光的滤色器170的配置工序。

[0122]

由此,在半导体装置100被用于例如对波长为650nm以上的光进行光电变换的用途的情况下,能够制造出能够精度良好地检测作为对象的波长的光的半导体装置100。

[0123]

此外,例如,在第2成膜工序中,进一步,在半导体基板110中,在没有设置晶体管及apd等光电变换部的其他区域220中的半导体基板110的主面112,形成由上述绝缘材料构成的第2衬膜153。此外,例如,防反射膜151、第1衬膜152和第2衬膜153一体地形成。此外,例如,第1衬膜152和第2衬膜153厚度相同。

[0124]

由此,能够利用以往的cmos制造方法的工艺,简便地制造防反射膜151、第1衬膜152和第2衬膜153。

[0125]

(其他实施方式)

[0126]

以上,对实施方式的半导体装置等进行了说明,但本发明并不限定于上述实施方式。

[0127]

例如,在上述实施方式中用于说明的数值全部是为了具体地说明本发明而例示的,本发明并不受例示的数值限定。

[0128]

此外,在上述实施方式中,对构成半导体装置具有的层叠构造的各层的主要材料进行了例示,但在半导体装置具有的层叠构造的各层中,在能够实现与上述实施方式的层叠构造同样的功能的范围内也可以包含其他材料。

[0129]

除此以外,对各实施方式施以本领域技术人员想到的各种变形而得到的形态、或在不脱离本发明的主旨的范围内通过将各实施方式的构成要素及功能任意地组合而实现的形态也包含在本发明中。例如,本发明也可以作为具备以矩阵状配置有多个本发明的半导体装置的摄像装置、以及该摄像装置的制造方法来实现。

[0130]

产业上的可利用性

[0131]

本发明能够应用于具有像素区域和逻辑区域、能够提高聚光效率并且能够抑制暗电流的发生的半导体装置及其制造方法。

[0132]

标号说明

[0133]

100、100a 半导体装置

[0134]

110 半导体基板(硅半导体基板)

[0135]

111 apd(光电变换部)

[0136]

112 主面

[0137]

120 栅极绝缘膜

[0138]

121 栅极电极

[0139]

130、131、300 底层氧化膜

[0140]

140 侧壁

[0141]

150、150a、310、310a、310b 绝缘膜

[0142]

151、151a 防反射膜

[0143]

152 第1衬膜

[0144]

153 第2衬膜

[0145]

160 晶体管

[0146]

170 滤色器

[0147]

200 像素区域(第1区域)

[0148]

210 逻辑区域(第2区域)

[0149]

220 其他区域(第3区域)

[0150]

400、410 抗蚀剂掩模

[0151]

a、a1、b、c 膜厚

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。