1.本技术涉及存储器技术领域,尤其涉及一种故障测试方法、装置、电子设备及存储介质。

背景技术:

2.动态随机存取存储器(dynamic random access memory,简称dram)是计算机中常用的半导体存储器件dram中的每个存储单元通常包括电容器和晶体管,晶体管的栅极与字线相连、漏极与位线相连、源极与电容器相连。通过字线上的电压信号控制晶体管的打开或关闭,进而通过位线读取存储在电容器中的数据信息,或者通过位线将数据信息写入到电容器中进行存储。每个存储单元通过电容内存储电荷的多少来代表一个二进制比特(bit)是1还是0。

3.dram的电路结构复杂且集成度高,随着制程的推进,工艺上会出现很多问题。在生产过程中,可能会出现导致dram中电路结构接触不良等问题,从而影响读写稳定性。因此,需要开发一种有效的故障测试方法。

技术实现要素:

4.本技术提供一种故障测试方法、装置、电子设备及存储介质,用以对提高读写故障抓取率,有效筛选出线上不稳定的产品。

5.根据一些实施例,本技术第一方面提供一种故障测试方法,包括:针对存储阵列的每个字线,执行测试处理,以确定字线下的故障存储单元;其中,测试处理包括:在设定的写入时长内,执行向字线下的存储单元写入测试数据;在设定的预充电操作时长内,执行对所有位线的预充电,并在预充电操作时长结束后,读取字线下的存储单元;通过比较测试数据和读取的数据,确定字线下的故障存储单元;根据存储阵列中所有字线下的故障存储单元,确定存储阵列中的故障单元。

6.一种可行的实施方式中,在设定的写入时长内,执行向字线下的存储单元写入测试数据,包括:激活字线后,在第一起始时刻向字线下的存储单元写入测试数据;自第一起始时刻经过写入时长时,去激活字线。

7.一种可行的实施方式中,去激活字线之前,还包括:激活字线的相邻字线。

8.一种可行的实施方式中,在设定的预充电操作时长内,执行对所有位线的预充电,并在预充电操作时长结束后,读取字线下的存储单元,包括:在去激活字线之后,对所有位线执行预充电;自执行预充电起经过预充电操作时长时,激活字线;读取字线下的存储单元。

9.一种可行的实施方式中,本技术第一方面提供一种故障测试方法,还包括:针对存储阵列的每个字线,执行多次测试处理,每次测试处理采用相同的一组测试数据,确定多次测试处理下的故障存储单元;根据多次测试处理下的故障存储单元,统计存储阵列中每个存储单元的故障次数,并计算存储单元的故障率;将故障率超过预设阈值的存储单元,确定

为存储阵列中的故障单元。

10.一种可行的实施方式中,本技术第一方面提供一种故障测试方法,还包括:针对存储阵列的每个字线,执行多次测试处理,每次测试处理采用不同的多组测试数据,确定多次测试处理下的故障存储单元;根据多次测试处理下的故障存储单元,统计存储阵列中每个存储单元的故障次数,并计算存储单元的故障率;将故障率超过预设阈值的存储单元,确定为存储阵列中的故障单元。

11.一种可行的实施方式中,本技术第一方面提供一种故障测试方法,还包括:根据不同的多组测试数据中的每组测试数据,针对存储阵列的每个字线,执行多次测试处理,确定多次测试处理下的故障存储单元;根据多次测试处理下的故障存储单元,统计存储阵列中每个存储单元的故障次数,并计算每组测试数据下存储单元的第一故障率;计算多组测试数据对应的第一故障率的平均值;将平均值超过预设阈值的存储单元,确定为存储阵列中的故障单元。

12.进一步地,不同的多组测试数据中,每个位置的数据只在其中一组测试数据中为逻辑1或逻辑0;每组测试数据中,每列只有一个位置的数据为逻辑1或逻辑0,且相邻列之间为逻辑1或逻辑0的位置不相邻。

13.一种可行的实施方式中,本技术第一方面提供一种故障测试方法,还包括:对存储阵列进行初始化。

14.进一步地,对存储阵列进行初始化,包括:对存储阵列全写入逻辑0或全写入逻辑1;设定测试环境参数的初始值。

15.进一步地,测试环境参数包括以下至少一项:感应放大器启动时间、字线激活电压以及电源电压。

16.一种可行的实施方式中,本技术第一方面提供一种故障测试方法,还包括:建立包括不同数值的测试环境参数的训练集;基于训练集,获取不同测试温度、不同写入时长下,测试环境参数的每一数值对应的存储阵列中故障单元的数量占比;获取测试环境参数的每一数值下数量占比的差值,将差值低于预设阈值,且数量占比满足预设范围所对应的数值,作为测试环境参数的初始值。

17.下面为本技术第一方面提供一种数据校验方法所对应的装置、电子设备及存储介质,其效果可参考方法部分。

18.根据一些实施例,本技术第二方面提供一种故障测试装置,包括:第一确定模块,用于针对存储阵列的每个字线,执行测试处理,以确定字线下的故障存储单元;其中,第一确定模块包括测试单元和比较单元;测试单元用于在设定的写入时长内,执行向字线下的存储单元写入测试数据;测试单元还用于在设定的预充电操作时长内,执行对所有位线的预充电,并在预充电操作时长结束后,读取字线下的存储单元;比较单元用于通过比较测试数据和读取的数据,确定字线下的故障存储单元;第二确定模块,用于根据存储阵列中所有字线下的故障存储单元,确定存储阵列中的故障单元。

19.一种可行的实施方式中,测试单元,具体用于激活字线后,在第一起始时刻向字线下的存储单元写入测试数据;测试单元,具体还用于自第一起始时刻经过写入时长时,去激活字线。

20.进一步地,测试单元用于去激活字线之前,具体还用于激活字线的相邻字线。

21.一种可行的实施方式中,测试单元,具体还用于在去激活字线之后,对所有位线执行预充电;测试单元,具体还用于自执行预充电起经过预充电操作时长时,激活字线;测试单元,具体还用于读取字线下的存储单元。

22.一种可行的实施方式中,测试单元,具体还用于针对存储阵列的每个字线,执行多次测试处理,每次测试处理采用相同的一组测试数据,确定多次测试处理下的故障存储单元;测试单元,具体还用于根据多次测试处理下的故障存储单元,统计存储阵列中每个存储单元的故障次数,并计算存储单元的故障率;测试单元,具体还用于将故障率超过预设阈值的存储单元,确定为存储阵列中的故障单元。

23.一种可行的实施方式中,测试单元,具体还用于针对存储阵列的每个字线,执行多次测试处理,每次测试处理采用不同的多组测试数据,确定多次测试处理下的故障存储单元;测试单元,具体还用于根据多次测试处理下的故障存储单元,统计存储阵列中每个存储单元的故障次数,并计算存储单元的故障率;测试单元,具体还用于将故障率超过预设阈值的存储单元,确定为存储阵列中的故障单元。

24.一种可行的实施方式中,测试单元,具体还用于根据不同的多组测试数据中的每组测试数据,针对存储阵列的每个字线,执行多次测试处理,确定多次测试处理下的故障存储单元;测试单元,具体还用于根据多次测试处理下的故障存储单元,统计存储阵列中每个存储单元的故障次数,并计算每组测试数据下存储单元的第一故障率;测试单元,具体还用于计算多组测试数据对应的第一故障率的平均值;测试单元,具体还用于将平均值超过预设阈值的存储单元,确定为存储阵列中的故障单元。

25.一种可行的实施方式中,不同的多组测试数据中,每个位置的数据只在其中一组测试数据中为逻辑1或逻辑0;每组测试数据中,每列只有一个位置的数据为逻辑1或逻辑0,且相邻列之间为逻辑1或逻辑0的位置不相邻。

26.一种可行的实施方式中,装置还包括:初始化模块,用于对存储阵列进行初始化。

27.一种可行的实施方式中,初始化模块,具体用于对存储阵列全写入逻辑0或全写入逻辑1;初始化模块,具体还用于设定测试环境参数的初始值。

28.一种可行的实施方式中,测试环境参数包括以下至少一项:感应放大器启动时间、字线激活电压以及电源电压。

29.一种可行的实施方式中,初始化模块,具体还用于建立包括不同数值的测试环境参数的训练集;初始化模块,具体还用于基于训练集,获取不同测试温度、不同写入时长下,测试环境参数对应的存储阵列中故障单元的数量占比;初始化模块,具体还用于获取测试环境参数的每一数值下数量占比的差值,将差值低于预设阈值,且数量占比满足预设范围所对应的数值,作为测试环境参数的初始值。

30.根据一些实施例,本技术第三方面提供一种电子设备,包括:处理器,以及与处理器通信连接的存储器;存储器存储计算机执行指令;处理器执行存储器存储的计算机执行指令,以实现如第一方面的方法。

31.根据一些实施例,本技术第四方面提供一种计算机可读存储介质,计算机可读存储介质中存储有计算机执行指令,计算机执行指令被处理器执行时用于实现如第一方面的方法。

32.本技术实施例提供的故障测试方法、装置、电子设备及存储介质,针对存储阵列的

每个字线,执行测试处理,以确定字线下的故障存储单元;其中,测试处理包括:在设定的写入时长内,执行向字线下的存储单元写入测试数据;在设定的预充电操作时长内,执行对所有位线的预充电,并在预充电操作时长结束后,读取字线下的存储单元;通过比较测试数据和读取的数据,确定字线下的故障存储单元;根据存储阵列中所有字线下的故障存储单元,确定存储阵列中的故障单元。本技术实施例通过对写入时长和预充电操作时长的卡控设定了较高的读写测试要求,有利于提高读写故障抓取率,有效筛选出线上不稳定的产品,进而提高产品质量。

附图说明

33.此处的附图被并入说明书中并构成本说明书的一部分,示出了符合本技术的实施例,并与说明书一起用于解释本技术的原理。

34.图1a、图1b为示例性的dram的结构示意图;

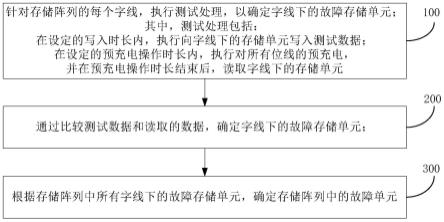

35.图2为本技术实施例提供的一种故障测试方法的流程图;

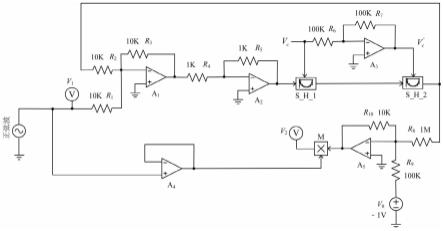

36.图3为示例性的dram的存储单元的电路图;

37.图4为示例性的dram数据读写过程的时序图;

38.图5为本技术实施例提供的一种测试数据的拓扑示意图;

39.图6为本技术实施例提供的一种感应放大器启动时间的测试结果;

40.图7a为本技术实施例提供的一种感应放大器启动调节时间表;

41.图7b为本技术实施例提供的sap及snp启动调节时间的变化曲线图;

42.图8为本技术实施例提供的一种感应放大器的工作时序图;

43.图9为本技术实施例提供的一种字线激活电压的测试结果;

44.图10为本技术实施例提供的一种电源电压的测试结果;

45.图11为本技术实施例提供的另一种故障测试方法的流程图;

46.图12为本技术实施例提供的一种故障测试装置的结构示意图;

47.图13为本技术实施例提供的另一种故障测试装置的结构示意图;

48.图14为本技术实施例提供的一种电子设备的结构示意图。

49.通过上述附图,已示出本技术明确的实施例,后文中将有更详细的描述。这些附图和文字描述并不是为了通过任何方式限制本技术构思的范围,而是通过参考特定实施例为本领域技术人员说明本技术的概念。

具体实施方式

50.这里将详细地对示例性实施例进行说明,其示例表示在附图中。下面的描述涉及附图时,除非另有表示,不同附图中的相同数字表示相同或相似的要素。以下示例性实施例中所描述的实施方式并不代表与本技术相一致的所有实施方式。相反,它们仅是与本技术的一些方面相一致的装置和方法的例子。

51.动态随机存取存储器(dynamic random access memory,简称dram)是计算机中常用的半导体存储器件,dram中的每个存储单元通常包括电容器和晶体管,晶体管的栅极与字线相连、漏极与位线相连、源极与电容器相连,字线上的电压信号能够控制晶体管的打开或关闭,进而通过位线读取存储在电容器中的数据信息,或者通过位线将数据信息写入到

电容器中进行存储。每个存储单元通过电容内存储电荷的多少来代表一个二进制比特(bit)是1还是0,存储单元排列成矩阵形式,即存储阵列。

52.图1a和图1b为示例性的dram的结构示意图。dram上的字线与位线的数量根据dram内存设计来定,图1a示出了七条位线bl0指bl6(bitline,简称bl),9条字线wl0至wl8,以及冗余字线(dummy wordline,简称dwl)。在字线与位线围成的区域内为多个有源区(active area,简称aa),存储单元坐落在有源区上,其中(0,0)、(1,0)、(2、0)等坐标用于标记存储单元的位置。图1b示出了存储单元cell、字线wl、位线bl、电容与硅衬底接触的部件nc、位线与硅衬底接触的部件blc、上电极板(top capacitance plate,简称tcp)的结构示意图,其中,采用沟槽式技术把字线埋到晶圆表面之下(buried wordline,简称bw)。

53.随着制程的推进,dram的电路结构复杂且集成度高,工艺上会出现很多问题。在生产过程中,可能出现nc/blc/cell开路问题,导致存储器无法进行读写;还可能出现nc-aa/blc-aa/cell-nc接触不好或不稳定而呈现高阻值,进而降低存储器的读写速度,影响读写稳定性。例如,在传输过程中电压信号被更多地消耗,为了达到逻辑“1”的电压,需要更长写入时间(write recovery time,简称twr);为了使bl和/bl的电压拉平,需要更长的预充电时间(row precharge time,简称trp)。

54.基于此,提供一种故障测试方法、装置、电子设备及存储介质,通过对dram的写操作过程中的写入时长与预充电时长的控制,实现对写入操作速度及读写准确率的测试,有效筛选出dram上存在读写故障的位置。

55.下面以具体地实施例对技术方案以及技术方案如何解决上述技术问题进行详细说明。下面这几个具体的实施例可以相互结合,对于相同或相似的概念或过程可能在某些实施例中不再赘述。下面将结合附图,对实施例进行描述。

56.实施例一

57.图2为本技术实施例提供的一种故障测试方法的流程图。该方法应用于存储器,其执行主体可以为故障测试装置,也可以为集成了故障测试装置的设备,下面以执行主体为故障测试装置为例进行说明。如图2所示,该方法可以包括以下步骤:

58.s100、针对存储阵列的每个字线,执行测试处理,以确定字线下的故障存储单元;其中,测试处理包括:在设定的写入时长内,执行向字线下的存储单元写入测试数据;在设定的预充电操作时长内,执行对所有位线的预充电,并在预充电操作时长结束后,读取字线下的存储单元;

59.s200、通过比较测试数据和读取的数据,确定字线下的故障存储单元;

60.s300、根据存储阵列中所有字线下的故障存储单元,确定存储阵列中的故障单元。

61.结合图3和图4,对dram的存储单元的电路结构进行说明。图3为示例性的dram的存储单元的电路图,自右向左分析,字线wl连接存储单元的晶体管的栅极;该晶体管的一端与位线bl连接,另一端与存储电容连接,存储电容连接固定电压vary/2(图3中未示出)。电路ys与晶体管ysw的栅极连接,晶体管ysw的一端与位线bl连接,另一端连接io端口,用于输入或输出信号。字线使能信号bleq,与三个晶体管的栅极连接,用于通过控制字线使能信号bleq将bl和/bl拉平至v

ble

(等于vary/2)。感应放大器(sense amplifier,简称sa)连接在bl和/bl之间,由两个nmos管和两个pmos管组成。

62.图4为示例性的dram数据读写过程的时序图,以读取“1”写入“0”为例,对dram的读

操作流程及写操作流程进行示例性说明。

63.(1)激活阶段(active,对应图4的act阶段):bl和/bl的电压相同,均为v

ble

,关闭字线使能信号bleq;激活字线wl使存储单元的晶体管导通,存储电容与bl连通,存储的电荷流向bl(即charge sharing),进而导致bl和/bl产生的电压差δv。若存储单元存储数据为“1”时,则charge sharing导致bl电压高于/bl的电压;若存储单元存储数据为“0”时,则charge sharing导致bl电压低于/bl的电压。

64.进一步地,感应放大器对bl和/bl的电压差进行感应放大(sa sensing),以存储单元存储数据为“1”为例,此时bl电压高于/bl的电压,感应放大器中晶体管2相比于晶体管4更具有导通性;晶体管3相比于晶体管1更具有导通性。此时,pcs晶体管连接的电压被设定为逻辑1的电压,即vary。由于晶体管3相比于晶体管1更具有导通性,bl上的电压会更快的被pcs晶体管连接的电压拉到逻辑1的电压。同理,ncs晶体管连接的电压被设定为逻辑0的电压,即vss。由于晶体管2相比于晶体管4更具有导通性,/bl上的电压会更快的被电压ncs拉到逻辑0的电压。其中,在发生感应放大时,bl上的电压由于分配到感应放大器上会发生稍微的下降,即如图4所示的下凹趋势。最后,bl的电压信号上升稳定至vary;/bl的电压信号下降稳定至vss。此时,打开电路ys导通晶体管ysw,则可向外部读出“1”。

65.(2)写入阶段(write,对应图4的wr)。以写入数据“0”为例,如图3所示,打开电路ys导通晶体管ysw,自外部向bl写入“0”。如图3所示,bl电压降低,并低于/bl。此时,感应放大器的晶体管4相比于晶体管2更具有导通性,/bl上的电压会更快的被电压pcs拉到逻辑1的电压;晶体管1相比于晶体管3更具有导通性,bl上的电压会更快的被电压ncs拉到逻辑0的电压。如图4所示,bl的电压信号下降稳定至vss;/bl的电压信号上升稳定至vary。此时,数据“0”通过bl写入存储单元。

66.(3)预充电阶段(pre charge,对应图4的per)。写入完成后,关闭wl,使存储单元的晶体管截止,断开存储电容与bl的连接;关闭感应放大器,断开pcs和ncs与bl和/bl的连接。打开bleq信号,连通bl和/bl,bl和/bl上的电压变化参照图4,最后bl和/bl上的电压拉平。

67.基于上述dram的读写流程,步骤s100中,对存储阵列的每个字线,在设定的写入时长内向该子线下的存储单元写入测试数据,可用于检测测试数据流经的电路的性能。以图3为例,具体可以检测用于控制io端口与bl连通或断开的电路ys和晶体管ysw的性能、位线bl的传输性能、感应放大器的性能、存储单元的性能。步骤s100中,对存储阵列的每个字线,在设定的预充电时长内执行预充电,可通过检测bleq控制电路的性能,以及位线bl和/bl的性能。

68.一个示例中,可以采用每次写入1bit的测试数据的测试方式,通常dram的每一条字线对应有多个存储单元,每次写入1bit测试数据可实现对一条字线的多次激活测试,提高测试可靠性。为了提高测试速度,另一个示例中,可以采用突发写入模式,每次写入多个bits的测试数据。本实施例对每次写入的测试数据的位数不作限定,在实际测试中,可根据测试效率要求和测试可靠性要求进行设定。

69.进一步地,读取先前写入测试数据的存储单元,获得读取数据。若读取数据与测试数据相同,则表明该存储单元性能良好,并且对应的字线、位线、感应放大器等电路没有故障;若读取数据与测试数据不同,则表明该存储单元为故障单元。

70.其中,故障可以表现为单个存储单元故障(single bit fail,简称sbit fail),该

故障表明对应的存储单元的电容或晶体管可能存在故障,也可能是对应的位线存在故障;还可以表现为列故障(column fail),该故障表明对应的字线可能存在故障。通过上述故障可对故障位置进行初步判断,有利于提高修补效率。

71.本技术实施例通过卡控写入时长twr和预充电时长trp设定了较高的读写测试要求,有利于提高读写故障抓取率,有效筛选出线上不稳定的产品,进而提高产品质量。

72.进一步地,在步骤s100中,在设定的写入时长内,执行向字线下的存储单元写入测试数据,包括:激活字线后,在第一起始时刻向字线下的存储单元写入测试数据;自第一起始时刻经过写入时长时,去激活字线。其中,“激活”是指拉高字线的电位以使存储单元的晶体管导通,存储单元的存储电容连接至对应的位线。“去激活”是指拉低字线的电位以使存储单元的晶体管截止,断开存储单元的存储电容与位线的连接。

73.一种可行的去激活字线方式为通过设计逻辑电路,根据待测试dram的内部或外部时钟信号,实现对字线的电平的控制,使字线的电平在第一时刻被拉高并维持预设时长(即激活),之后拉低(即去激活)。另一种可行的去激活字线方式为通过计算机程序控制对字线的电平,比如控制器、芯片等,使字线的电平在第一时刻被拉高并维持预设时长(即激活),之后拉低(即去激活)。

74.具体的,通过提前预充电的开始时间缩短写入时长。当执行完写入操作后需要关闭被激活的当前字线并进行预充电。其中,预充电也可以通过辅助芯片使待测试存储器在每次读写操作之后自动进行预充电,也可以为命令控制。以对字线wl0的测试为例,激活wl0;在第一时刻向wl0所连接的一个或多个存储单元写入测试数据;发出预充电命令,关闭wl0进入预充电状态。写入时长即为自第一时刻开始至关闭wl0结束。

75.进一步地,去激活字线之前,还包括:激活字线的相邻字线。实际的数据存储中,存储单元的数据写入过程、数据保留过程及数据读取过程会受到相邻电路的不同程度的影响。通过在上述写入期间内激活相邻电路,制造更恶劣的写入条件或数据保留条件,以筛选出不稳定的存储单元,有利于提高故障单元的抓取率。

76.具体的,以对字线wl0及其相邻字线wl1的测试为例。激活wl0;在第一时刻向wl0所连接的一个或多个存储单元写入测试数据;激活wl1;通过发出预充电命令,关闭wl0和wl1进入预充电状态。写入时长即为自第一时刻开始至关闭wl0和wl1结束。其中,若激活wl1的时刻靠近写入时长的开始时刻,则激活wl1会影响wl0的数据写入过程。激活wl1的时刻越靠近写入时长的结束时刻,则激活wl1会影响wl0的数据保留过程。

77.进一步地,在步骤s100中,在设定的预充电操作时长内,执行对所有位线的预充电,并在预充电操作时长结束后,读取字线下的存储单元,包括:在去激活字线之后,对所有位线执行预充电;自执行预充电起经过预充电操作时长时,激活字线;读取字线下的存储单元。

78.一种可行的设定预充电操作时长的方式为通过设计逻辑电路,根据待测试dram的内部或外部时钟信号,实现对bleq信号的电平的控制,使bleq信号的电平在去激活字线后被拉高并维持预设时长(即预充电),之后拉低(即停止预充电)。另一种可行的的设定预充电操作时长的方式为通过计算机程序控制对bleq信号的电平,比如控制器、芯片等,使bleq信号的电平在去激活字线后被拉高并维持预设时长(即预充电),之后拉低(即停止预充电)。

79.示例性的,通过提前对字线的激活缩短预充电操作时间。以对字线wl5的测试为例,在对字线wl5去激活进入预充电阶段后,可通过再次发出激活wl5的指令以结束预充电阶段,并读取先前向wl5对应的存储单元写入的测试数据。假设wl6为wl5之后要进行写入测试数据的字线,也可以通过发出激活wl6的指令以结束预充电阶段,并向wl6写入测试数据。假设wl0早于wl5执行写入测试数据的字线,也可以通过再次发出激活wl0的指令以结束预充电阶段,并读取先前向wl0对应的存储单元写入的测试数据,由于随着存储时间的延长,存储单元的存储电容会出现漏电的问题,上述间隔一段时间后再读取数据,有利于检测存储单元对数据的保留性。

80.可选地,本实施例提供的故障测试方法,还包括:针对存储阵列的每个字线,执行多次测试处理,每次测试处理采用相同的一组测试数据,确定多次测试处理下的故障存储单元;根据多次测试处理下的故障存储单元,统计存储阵列中每个存储单元的故障次数,并计算存储单元的故障率;将故障率超过预设阈值的存储单元,确定为存储阵列中的故障单元。

81.其中,测试数据可以为全0,可以为全1,可以为随机排列0与1的组合,也可以为按照预设规则排列的0与1的组合。选择全0或全1这种简单的测试数据,有利于快速地判断出读取数据的正确或错误,有利于提高测试速率。由于实际的存储阵列上相邻的存储单元之间会存在互相影响,选择0与1的排列组合,有利于提高存储阵列正确存储信息的难度,也有利于筛选出不稳定的故障单元,提高故障单元的抓取率。

82.图5为本技术实施例提供的一种测试数据的拓扑示意图,包括8种按照预设规则排列的拓扑数据。每个拓扑数据中黑色表示逻辑1,空心表示逻辑0;也可以黑色表示逻辑0,空心表示逻辑1。上述的测试数据可以选择图5所示的8种拓扑数据中的任意一种,其中黑色六边形比较均匀地分布在白色六边形中,由于实际的存储阵列上相邻的存储单元之间会存在互相影响,图5所示的拓扑结构更有利于使相邻的存储单元的测试数据不同,有利于提高存储阵列正确存储信息的难度,也有利于筛选出不稳定的故障单元,提高故障单元的抓取率。

83.具体的,选定一组测试数据,对待测试的存储阵列进行多次重复测试,统计每个存储单元的读取数据与测试数据不一致的次数,即该存储单元出现故障的次数。进一步,计算出现故障的次数与重复测试的次数的比值,即该存储单元的故障率。由于存储单元的存储性能可能不稳定,通过多次重复测试,有利于筛选出性能不稳定的故障单元。考虑到可能会出现读取误差,通过多次重复测试,有利于提高测试结果的可靠性,筛除部分故障率不超过预设阈值的存储单元,减少后续修补的工作。为了提高产品的质量,可将故障率的预设阈值设定为较小的值,提高故障单元的抓取率。

84.可选地,本实施例提供的故障测试方法,还包括:针对存储阵列的每个字线,执行多次测试处理,每次测试处理采用不同的多组测试数据,确定多次测试处理下的故障存储单元;根据多次测试处理下的故障存储单元,统计存储阵列中每个存储单元的故障次数,并计算存储单元的故障率;将故障率超过预设阈值的存储单元,确定为存储阵列中的故障单元。

85.其中,测试数据可以为全0,可以为全1,可以为随机排列0与1的组合,也可以为按照预设规则排列的0与1的组合。多组测试数据可以为前述的任意组合。具体的,多组测试数据可以为多种随机排列0与1的组合,也可以为按照不同预设规则排列的0与1的组合,也可

以为全0和全1两组测试数据。选择全0和全1这种简单的测试数据,有利于快速地判断出读取数据的正确或错误,有利于提高测试速率。

86.上述的测试数据可以选择图5所示的8种拓扑数据中的任意多种,其中黑色六边形比较均匀地分布在白色六边形中,且不同的拓扑数据中黑色六边形在白色六边形的分布位置不重复。由于实际的存储阵列上相邻的存储单元之间会存在互相影响,采用图5所示的多种拓扑数据,更有利于使每次测试中相邻的存储单元的测试数据不同,有利于提高存储阵列正确存储信息的难度,也有利于筛选出不稳定的故障单元,提高故障单元的抓取率。

87.具体的,选定多组测试数据,对待测试的存储阵列进行多次测试,统计每个存储单元的读取数据与测试数据不一致的次数,即该存储单元出现故障的次数。进一步,计算出现故障的次数与重复测试的次数的比值,即该存储单元的故障率。由于存储单元的存储性能可能不稳定,通过选择不同测试数据进行测试,有利于筛选出性能不稳定的故障单元。由于实际的存储阵列上相邻的存储单元之间会存在互相影响,通过选择不同测试数据进行测试,有利于提高存储阵列正确存储信息的难度,也有利于筛选出不稳定的故障单元,提高故障单元的抓取率。通过筛除部分故障率不超过预设阈值的存储单元,减少后续修补的工作。为了提高产品的质量,可将故障率的预设阈值设定为较小的值,提高故障单元的抓取率。

88.可选地,本实施例提供的故障测试方法,还包括:根据不同的多组测试数据中的每组测试数据,针对存储阵列的每个字线,执行多次测试处理,确定多次测试处理下的故障存储单元;根据多次测试处理下的故障存储单元,统计存储阵列中每个存储单元的故障次数,并计算每组测试数据下存储单元的第一故障率;计算多组测试数据对应的第一故障率的平均值;将平均值超过预设阈值的存储单元,确定为存储阵列中的故障单元。

89.其中,测试数据可以为全0,可以为全1,可以为随机排列0与1的组合,也可以为按照预设规则排列的0与1的组合。多组测试数据可以为前述的任意组合。具体的,多组测试数据可以为多种随机排列0与1的组合,也可以为按照不同预设规则排列的0与1的组合,也可以为全0和全1两组测试数据。选择全0和全1这种简单的测试数据,有利于快速地判断出读取数据的正确或错误,有利于提高测试速率。

90.上述的测试数据可以选择图5所示的8种拓扑数据中的任意多种,其中黑色六边形比较均匀地分布在白色六边形中,且不同的拓扑数据中黑色六边形在白色六边形的分布位置不重复。由于实际的存储阵列上相邻的存储单元之间会存在互相影响,采用图5所示的多种拓扑数据,更有利于使每次测试中相邻的存储单元的测试数据不同,有利于提高存储阵列正确存储信息的难度,也有利于筛选出不稳定的故障单元,提高故障单元的抓取率。

91.具体的,选定多组测试数据,并且每组测试数据进行多次重复测试。统计每组测试数据下的重复测试中,每个存储单元的读取数据与测试数据不一致的次数,即该存储单元出现故障的次数;计算出现故障的次数与重复测试的次数的比值,即当前测试数据下该存储单元的第一故障率。进一步,将每组测试数据对应的第一故障率进行平均,将该平均值作为存储单元的故障率。由于存储单元的存储性能可能不稳定,通过采用不同的测试数据以及多次重复测试,有利于筛选出性能不稳定的故障单元,有利于提高测试结果的可靠性。通过筛除部分故障率不超过预设阈值的存储单元,减少后续修补的工作。为了提高产品的质量,可将故障率的预设阈值设定为较小的值,提高故障单元的抓取率。

92.进一步地,不同的多组测试数据中,每个位置的数据只在其中一组测试数据中为

amplifier n-fet control简称san)和pmos控制器(sense-amplifier p-fet control,简称sap)。图7a为本技术实施例提供的一种感应放大器启动调节时间表,包括多种启动模式。每个启动模式对应一个四维的控制信号。示例性的,当要调节为t5启动模式时,通过四维控制信号1100,使得san的启动时间相对于正常的感应放大器启动时间提前了0.8ns,sap的启动时间相对于正常的感应放大器启动时间提前了1.1ns。图7a中的

“‑

m1”代表相对于正常的启动时间提前m1时长;“ m9”代表相对于正常的启动时间延后m9时长。另外,图7b为本技术实施例提供的sap及snp启动调节时间的变化曲线图,负值表示相对于正常的启动时间提前;正值表示相对于正常的启动时间延后。

101.进一步地,图8为本技术实施例提供的一种感应放大器的工作时序图,以读或写“1”为例对字线激活至感应放大器启动的过程进行了说明。具体的,响应于激活指令,bleqb信号和fxb信号低电平有效,子字线swl电平逐渐拉高并趋于平稳;子字线swl电平拉高至阈值电压使存储单元的晶体管导通,存储电容与位线blt连通,blt电压升高表明存储电容存储数据为逻辑1。由于感应放大器还未启动,此时位线blb(相当于/bl)电平保持不变。sap1的电平拉高表明sap1启动(图8中的sap1即sap),此时blt信号被感应放大器继续拉高;san的电平拉高表明san启动,此时blb信号被感应放大器拉低。

102.图9为本技术实施例提供的一种字线激活电压的测试结果。其中,ht表示较高的测试温度;lt表示较低的测试温度;twr为写入时长包括8.5ns、10.5ns、12.5ns三种情况。纵坐标为失效数量(fail bit count,简称fbc),横坐标为字线激活电压,2.9v表示vpp取2.9v。以ht-twr:8.5ns的测试曲线为例,字线激活电压越低,失效数量增加。将六条测试曲线进行对比,选择2.9v作为字线激活电压的初始值,尽量选择6个测试条件下的故障率相差不多时所对应的电源电压值,以减少测试温度及写入时长对故障率的作用。

103.图10为本技术实施例提供的一种电源电压的测试结果。其中,ht表示较高的测试温度;lt表示较低的测试温度;twr为写入时长包括8.5ns、10.5ns、12.5ns三种情况。纵坐标为失效数量(fail bit count,简称fbc),横坐标为电源电压,0.97v表示vary取0.97v。以lt-twr:10.5ns的测试曲线为例,电源电压值越低,失效数量增加。将六条测试曲线进行对比,选择0.92v与0.97v之间的0.95v作为电源电压值的初始值。取0.95v既不会使电源电压值太低,导致测试条件过于严苛,进而将良好的产品也当作故障单元;也要比正常的电源电压值低一点,才有可能对产线上不稳定的产品筛选出来。另外,尽量选择6个测试条件下的故障率相差不多时所对应的电源电压值,用于减少测试温度及写入时长对故障率的作用。

104.一个示例中,图11为本技术实施例提供的另一种故障测试方法的流程图。首先初始化,进行设定测试模式(tm entry)并对待测试的存储阵列弱写入(weak write)全0或全1。其中弱写入是指基于调整后的测试环境参数,在相对严苛的读写条件下,向存储阵列写入数据。初始化完成后进行测试,步骤(1)对wl0进行激活,并写入图5所示的x8c拓扑数据,同时对twr进行卡控。步骤(2)对wl1进行激活;步骤(3)做预充电动作,即对wl0的trp进行卡控。步骤(4)对wl0 act做读取动作。步骤(5)遍历所有的字线以及所有的位线,比较读取结果与输入的拓扑数据,进行故障判断。步骤(6)换取不同的拓扑数据,循环上述步骤。本实施例在预先设定的测试环境参数下,采用如图5所示的拓扑数据进行测试,提高了存储阵列正确存储信息的难度,有利于筛选出不稳定的故障单元,提高故障单元的抓取率。

105.进一步地,可通过对待测试存储芯片进行切片,辅助投射电子显微镜(tem)等扫描

技术,对待测试存储芯片的电路结构进行观测,以验证本实施例提供的故障测试方法的准确性。

106.本实施例提供的故障测试方法,针对存储阵列的每个字线,执行测试处理,以确定字线下的故障存储单元;其中,测试处理包括:在设定的写入时长内,执行向字线下的存储单元写入测试数据;在设定的预充电操作时长内,执行对所有位线的预充电,并在预充电操作时长结束后,读取字线下的存储单元;通过比较测试数据和读取的数据,确定字线下的故障存储单元;根据存储阵列中所有字线下的故障存储单元,确定存储阵列中的故障单元。本实施例通过对写入时长和预充电操作时长的卡控设定了较高的读写测试要求,有利于提高读写故障抓取率,有效筛选出线上不稳定的产品,进而提高产品质量。

107.实施例二

108.图12为本技术实施例提供的一种故障测试装置的结构示意图,包括:第一确定模块10,用于针对存储阵列的每个字线,执行测试处理,以确定字线下的故障存储单元;其中,第一确定模块10包括测试单元11和比较单元12;测试单元11用于在设定的写入时长内,执行向字线下的存储单元写入测试数据;测试单元11还用于在设定的预充电操作时长内,执行对所有位线的预充电,并在预充电操作时长结束后,读取字线下的存储单元;比较单元12用于通过比较测试数据和读取的数据,确定字线下的故障存储单元;第二确定模块20,用于根据存储阵列中所有字线下的故障存储单元,确定存储阵列中的故障单元。

109.基于上述dram的读写流程,步骤s100中,对存储阵列的每个字线,在设定的写入时长内向该子线下的存储单元写入测试数据,可用于检测测试数据流经的电路的性能。以图3为例,具体可以检测用于控制io端口与bl连通或断开的电路ys和晶体管ysw的性能、位线bl的传输性能、感应放大器的性能、存储单元的性能。步骤s100中,对存储阵列的每个字线,在设定的预充电时长内执行预充电,可通过检测bleq控制电路的性能,以及位线bl和/bl的性能。

110.一个示例中,可以采用每次写入1bit的测试数据的测试方式,通常dram的每一条字线对应有多个存储单元,每次写入1bit测试数据可实现对一条字线的多次激活测试,提高测试可靠性。为了提高测试速度,另一个示例中,可以采用突发写入模式,每次写入多个bits的测试数据。本实施例对每次写入的测试数据的位数不作限定,在实际测试中,可根据测试效率要求和测试可靠性要求进行设定。

111.进一步地,读取先前写入测试数据的存储单元,获得读取数据。若读取数据与测试数据相同,则表明该存储单元性能良好,并且对应的字线、位线、感应放大器等电路没有故障;若读取数据与测试数据不同,则表明该存储单元为故障单元。

112.其中,故障可以表现为单个存储单元故障(single bit fail,简称sbit fail),该故障表明对应的存储单元的电容或晶体管可能存在故障,也可能是对应的位线存在故障;还可以表现为列故障(column fail),该故障表明对应的字线可能存在故障。通过上述故障可对故障位置进行初步判断,有利于提高修补效率。

113.本实施例通过卡控写入时长twr和预充电时长trp设定了较高的读写测试要求,有利于提高读写故障抓取率,有效筛选出线上不稳定的产品,进而提高产品质量。

114.可选地,测试单元11,具体用于激活字线后,在第一起始时刻向字线下的存储单元写入测试数据;测试单元11,具体还用于自第一起始时刻经过写入时长时,去激活字线。

115.一种可行的去激活字线方式为通过设计逻辑电路,根据待测试dram的内部或外部时钟信号,实现对字线的电平的控制,使字线的电平在第一时刻被拉高并维持预设时长(即激活),之后拉低(即去激活)。另一种可行的去激活字线方式为通过计算机程序控制对字线的电平,比如控制器、芯片等,使字线的电平在第一时刻被拉高并维持预设时长(即激活),之后拉低(即去激活)。

116.具体的,通过提前预充电的开始时间缩短写入时长。当执行完写入操作后需要关闭被激活的当前字线并进行预充电。其中,预充电也可以通过辅助芯片使待测试存储器在每次读写操作之后自动进行预充电,也可以为命令控制。以对字线wl0的测试为例,激活wl0;在第一时刻向wl0所连接的一个或多个存储单元写入测试数据;发出预充电命令,关闭wl0进入预充电状态。写入时长即为自第一时刻开始至关闭wl0结束。

117.进一步地,测试单元11用于去激活字线之前,具体还用于激活字线的相邻字线。实际的数据存储中,存储单元的数据写入过程、数据保留过程及数据读取过程会受到相邻电路的不同程度的影响。通过在上述写入期间内激活相邻电路,制造更恶劣的写入条件或数据保留条件,以筛选出不稳定的存储单元,有利于提高故障单元的抓取率。

118.具体的,以对字线wl0及其相邻字线wl1的测试为例。激活wl0;在第一时刻向wl0所连接的一个或多个存储单元写入测试数据;激活wl1;通过发出预充电命令,关闭wl0和wl1进入预充电状态。写入时长即为自第一时刻开始至关闭wl0和wl1结束。其中,若激活wl1的时刻靠近写入时长的开始时刻,则激活wl1会影响wl0的数据写入过程。激活wl1的时刻越靠近写入时长的结束时刻,则激活wl1会影响wl0的数据保留过程。

119.可选地,测试单元11,具体还用于在去激活字线之后,对所有位线执行预充电;测试单元11,具体还用于自执行预充电起经过预充电操作时长时,激活字线;测试单元11,具体还用于读取字线下的存储单元。

120.一种可行的设定预充电操作时长的方式为通过设计逻辑电路,根据待测试dram的内部或外部时钟信号,实现对bleq信号的电平的控制,使bleq信号的电平在去激活字线后被拉高并维持预设时长(即预充电),之后拉低(即停止预充电)。另一种可行的的设定预充电操作时长的方式为通过计算机程序控制对bleq信号的电平,比如控制器、芯片等,使bleq信号的电平在去激活字线后被拉高并维持预设时长(即预充电),之后拉低(即停止预充电)。

121.示例性的,通过提前对字线的激活缩短预充电操作时间。以对字线wl5的测试为例,在对字线wl5去激活进入预充电阶段后,可通过再次发出激活wl5的指令以结束预充电阶段,并读取先前向wl5对应的存储单元写入的测试数据。假设wl6为wl5之后要进行写入测试数据的字线,也可以通过发出激活wl6的指令以结束预充电阶段,并向wl6写入测试数据。假设wl0早于wl5执行写入测试数据的字线,也可以通过再次发出激活wl0的指令以结束预充电阶段,并读取先前向wl0对应的存储单元写入的测试数据,由于随着存储时间的延长,存储单元的存储电容会出现漏电的问题,上述间隔一段时间后再读取数据,有利于检测存储单元对数据的保留性。

122.一种可行的实施方式中,测试单元11,具体还用于针对存储阵列的每个字线,执行多次测试处理,每次测试处理采用相同的一组测试数据,确定多次测试处理下的故障存储单元;测试单元11,具体还用于根据多次测试处理下的故障存储单元,统计存储阵列中每个

存储单元的故障次数,并计算存储单元的故障率;测试单元11,具体还用于将故障率超过预设阈值的存储单元,确定为存储阵列中的故障单元。

123.其中,测试数据可以为全0,可以为全1,可以为随机排列0与1的组合,也可以为按照预设规则排列的0与1的组合。选择全0或全1这种简单的测试数据,有利于快速地判断出读取数据的正确或错误,有利于提高测试速率。由于实际的存储阵列上相邻的存储单元之间会存在互相影响,选择0与1的排列组合,有利于提高存储阵列正确存储信息的难度,也有利于筛选出不稳定的故障单元,提高故障单元的抓取率。

124.图5为本技术实施例提供的一种测试数据的拓扑示意图,包括8种按照预设规则排列的拓扑数据。每个拓扑数据中黑色表示逻辑1,空心表示逻辑0;也可以黑色表示逻辑0,空心表示逻辑1。上述的测试数据可以选择图5所示的8种拓扑数据中的任意一种,其中黑色六边形比较均匀地分布在白色六边形中,由于实际的存储阵列上相邻的存储单元之间会存在互相影响,图5所示的拓扑结构更有利于使相邻的存储单元的测试数据不同,有利于提高存储阵列正确存储信息的难度,也有利于筛选出不稳定的故障单元,提高故障单元的抓取率。

125.具体的,选定一组测试数据,对待测试的存储阵列进行多次重复测试,统计每个存储单元的读取数据与测试数据不一致的次数,即该存储单元出现故障的次数。进一步,计算出现故障的次数与重复测试的次数的比值,即该存储单元的故障率。由于存储单元的存储性能可能不稳定,通过多次重复测试,有利于筛选出性能不稳定的故障单元。考虑到可能会出现读取误差,通过多次重复测试,有利于提高测试结果的可靠性,筛除部分故障率不超过预设阈值的存储单元,减少后续修补的工作。为了提高产品的质量,可将故障率的预设阈值设定为较小的值,提高故障单元的抓取率。

126.一种可行的实施方式中,测试单元11,具体还用于针对存储阵列的每个字线,执行多次测试处理,每次测试处理采用不同的多组测试数据,确定多次测试处理下的故障存储单元;测试单元11,具体还用于根据多次测试处理下的故障存储单元,统计存储阵列中每个存储单元的故障次数,并计算存储单元的故障率;测试单元11,具体还用于将故障率超过预设阈值的存储单元,确定为存储阵列中的故障单元。

127.其中,测试数据可以为全0,可以为全1,可以为随机排列0与1的组合,也可以为按照预设规则排列的0与1的组合。多组测试数据可以为前述的任意组合。具体的,多组测试数据可以为多种随机排列0与1的组合,也可以为按照不同预设规则排列的0与1的组合,也可以为全0和全1两组测试数据。选择全0和全1这种简单的测试数据,有利于快速地判断出读取数据的正确或错误,有利于提高测试速率。

128.上述的测试数据可以选择图5所示的8种拓扑数据中的任意多种,其中黑色六边形比较均匀地分布在白色六边形中,且不同的拓扑数据中黑色六边形在白色六边形的分布位置不重复。由于实际的存储阵列上相邻的存储单元之间会存在互相影响,采用图5所示的多种拓扑数据,更有利于使每次测试中相邻的存储单元的测试数据不同,有利于提高存储阵列正确存储信息的难度,也有利于筛选出不稳定的故障单元,提高故障单元的抓取率。

129.具体的,选定多组测试数据,对待测试的存储阵列进行多次测试,统计每个存储单元的读取数据与测试数据不一致的次数,即该存储单元出现故障的次数。进一步,计算出现故障的次数与重复测试的次数的比值,即该存储单元的故障率。由于存储单元的存储性能可能不稳定,通过选择不同测试数据进行测试,有利于筛选出性能不稳定的故障单元。由于

实际的存储阵列上相邻的存储单元之间会存在互相影响,通过选择不同测试数据进行测试,有利于提高存储阵列正确存储信息的难度,也有利于筛选出不稳定的故障单元,提高故障单元的抓取率。通过筛除部分故障率不超过预设阈值的存储单元,减少后续修补的工作。为了提高产品的质量,可将故障率的预设阈值设定为较小的值,提高故障单元的抓取率。

130.一种可行的实施方式中,测试单元11,具体还用于根据不同的多组测试数据中的每组测试数据,针对存储阵列的每个字线,执行多次测试处理,确定多次测试处理下的故障存储单元;测试单元11,具体还用于根据多次测试处理下的故障存储单元,统计存储阵列中每个存储单元的故障次数,并计算每组测试数据下存储单元的第一故障率;测试单元11,具体还用于计算多组测试数据对应的第一故障率的平均值;测试单元11,具体还用于将平均值超过预设阈值的存储单元,确定为存储阵列中的故障单元。

131.其中,测试数据可以为全0,可以为全1,可以为随机排列0与1的组合,也可以为按照预设规则排列的0与1的组合。多组测试数据可以为前述的任意组合。具体的,多组测试数据可以为多种随机排列0与1的组合,也可以为按照不同预设规则排列的0与1的组合,也可以为全0和全1两组测试数据。选择全0和全1这种简单的测试数据,有利于快速地判断出读取数据的正确或错误,有利于提高测试速率。

132.上述的测试数据可以选择图5所示的8种拓扑数据中的任意多种,其中黑色六边形比较均匀地分布在白色六边形中,且不同的拓扑数据中黑色六边形在白色六边形的分布位置不重复。由于实际的存储阵列上相邻的存储单元之间会存在互相影响,采用图5所示的多种拓扑数据,更有利于使每次测试中相邻的存储单元的测试数据不同,有利于提高存储阵列正确存储信息的难度,也有利于筛选出不稳定的故障单元,提高故障单元的抓取率。

133.具体的,选定多组测试数据,并且每组测试数据进行多次重复测试。统计每组测试数据下的重复测试中,每个存储单元的读取数据与测试数据不一致的次数,即该存储单元出现故障的次数;计算出现故障的次数与重复测试的次数的比值,即当前测试数据下该存储单元的第一故障率。进一步,将每组测试数据对应的第一故障率进行平均,将该平均值作为存储单元的故障率。由于存储单元的存储性能可能不稳定,通过采用不同的测试数据以及多次重复测试,有利于筛选出性能不稳定的故障单元,有利于提高测试结果的可靠性。通过筛除部分故障率不超过预设阈值的存储单元,减少后续修补的工作。为了提高产品的质量,可将故障率的预设阈值设定为较小的值,提高故障单元的抓取率。

134.一种可行的实施方式中,不同的多组测试数据中,每个位置的数据只在其中一组测试数据中为逻辑1或逻辑0;每组测试数据中,每列只有一个位置的数据为逻辑1或逻辑0,且相邻列之间为逻辑1或逻辑0的位置不相邻。

135.示例性的,多组测试数据可以为图5所示的8种拓扑数据。以每种拓扑数据中黑色表示逻辑1,空心表示逻辑0为例,采用该8种拓扑数据,表征逻辑1的黑色遍历了该拓扑下的所有位置。也就是说,对于128bit的存储区域,采用图5所示的8种拓扑数据进行测试时,128bit中的每个存储单元均只有一次写入1。若以每种拓扑数据中黑色表示逻辑0,空心表示逻辑1为例,则对于128bit的存储区域,每个存储单元均只有一次写入1。在实际应用中,可根据每种拓扑数据的规则自行扩展,以适应待测试存储阵列的大小。

136.图13为本技术实施例提供的另一种故障测试装置的结构示意图,装置还包括:初始化模块30,用于对存储阵列进行初始化。

137.可选地,初始化模块30,具体用于对存储阵列全写入逻辑0或全写入逻辑1;初始化模块30,具体还用于设定测试环境参数的初始值。

138.具体的,通过初始化向存储阵列写入全0或全1,实现了对存储阵列内原始存储数据的覆盖。在将写入的测试数据与读出的数据进行比较时,避免原始存储数据的干扰。另外,通过初始化还可以对测试环境参数既测试模式进行设定,比如读写模式可以设定为逐一读写或突发读写。

139.一种可行的实施方式中,测试环境参数包括以下至少一项:感应放大器启动时间、字线激活电压以及电源电压。

140.具体的,参见图3和图4,涉及到用于表征逻辑1的电源电压vary,vary为感应放大器的pcs晶体管的电压,用于拉高位线的电压;vary/2作为位线的拉平电压,还作为存储单元的存储电容的参考电压;vary的大小影响着存储器的读与写。还涉及到图4示出的字线激活电压vpp,vpp的大小影响着存储器的读与写;还涉及到感应放大器启动时间,若将感应放大器启动时间提前,则进行电荷分享(charge sharing)的时间缩短,则bl与/bl之间的压差较小,不足以使拉高位线电压。

141.为了提高产品质量,本技术实施例通过调整测试环境参数的取值,设置更严苛的测试条件,以提高故障抓取率。

142.一种可行的实施方式中,初始化模块30,具体还用于建立包括不同数值的测试环境参数的训练集;初始化模块30,具体还用于基于训练集,获取不同测试温度、不同写入时长下,测试环境参数对应的存储阵列中故障单元的数量占比;初始化模块30,具体还用于获取测试环境参数的每一数值下数量占比的差值,将差值低于预设阈值,且数量占比满足预设范围所对应的数值,作为测试环境参数的初始值。

143.图6为本技术实施例提供的一种感应放大器启动时间的测试结果。其中,ht表示较高的测试温度;lt表示较低的测试温度;twr为写入时长包括8.5ns、10.5ns、12.5ns三种情况。纵坐标为失效数量(fail bit count,简称fbc),横坐标为感应放大器启动时间提前的时长,-1.8ns表示提前了1.8ns的时长。以lt-twr:8.5ns的测试曲线为例,感应放大器启动时间越提前,失效数量增加。将六条测试曲线进行对比,选择-0.38ns作为感应放大器启动时间提前的时长,将当前的感应放大器启动时间提前0.38ns作为初始值。取-0.38ns既不会使感应放大器启动时间过于提前,导致测试条件过于严苛,进而将良好的产品也当作故障单元;也要比正常的感应放大器启动时间提前一点,才有可能对产线上不稳定的产品筛选出来。另外,尽量选择6个测试条件下的故障率相差不多时所对应的感应放大器启动时间提前的时长,用于减少测试温度及写入时长对故障率的作用。

144.图9为本技术实施例提供的一种字线激活电压的测试结果。其中,ht表示较高的测试温度;lt表示较低的测试温度;twr为写入时长包括8.5ns、10.5ns、12.5ns三种情况。纵坐标为失效数量(fail bit count,简称fbc),横坐标为字线激活电压,2.9v表示vpp取2.9v。以ht-twr:8.5ns的测试曲线为例,字线激活电压越低,失效数量增加。以ht-twr:8.5ns的测试曲线为例,字线激活电压越低,故障单元的占比越高。将六条测试曲线进行对比,选择2.9v作为字线激活电压的初始值,尽量选择6个测试条件下的故障率相差不多时所对应的电源电压值,以减少测试温度及写入时长对故障率的作用。

145.图10为本技术实施例提供的一种电源电压的测试结果。其中,ht表示较高的测试

温度;lt表示较低的测试温度;twr为写入时长包括8.5ns、10.5ns、12.5ns三种情况。纵坐标为失效数量(fail bit count,简称fbc),横坐标为电源电压,0.97v表示vary取0.97v。以lt-twr:10.5ns的测试曲线为例,电源电压值越低,失效数量增加。将六条测试曲线进行对比,选择0.92v与0.97v之间的0.95v作为电源电压值的初始值。取0.95v既不会使电源电压值太低,导致测试条件过于严苛,进而将良好的产品也当作故障单元;也要比正常的电源电压值低一点,才有可能对产线上不稳定的产品筛选出来。另外,尽量选择6个测试条件下的故障率相差不多时所对应的电源电压值,用于减少测试温度及写入时长对故障率的作用。

146.一个示例中,图11为本技术实施例提供的另一种故障测试方法的流程图。首先初始化,进行设定测试模式(tm entry)并对待测试的存储阵列弱写入(weak write)全0或全1。其中弱写入是指基于调整后的测试环境参数,在相对严苛的读写条件下,向存储阵列写入数据。初始化完成后进行测试,步骤(1)对wl0进行激活,并写入图5所示的x8c拓扑数据,同时对twr进行卡控。步骤(2)对wl1进行激活;步骤(3)做预充电动作,即对wl0的trp进行卡控。步骤(4)对wl0 act做读取动作。步骤(5)遍历所有的字线以及所有的位线,比较读取结果与输入的拓扑数据,进行故障判断。步骤(6)换取不同的拓扑数据,循环上述步骤。本实施例在预先设定的测试环境参数下,采用如图5所示的拓扑数据进行测试,提高了存储阵列正确存储信息的难度,有利于筛选出不稳定的故障单元,提高故障单元的抓取率。

147.进一步地,可通过对待测试存储芯片进行切片,辅助投射电子显微镜(tem)等扫描技术,对待测试存储芯片的电路结构进行观测,以验证本实施例提供的故障测试方法的准确性。

148.本实施例提供的故障测试装置,包括:第一确定模块10,用于针对存储阵列的每个字线,执行测试处理,以确定字线下的故障存储单元;其中,第一确定模块10包括测试单元11和比较单元12;测试单元11用于在设定的写入时长内,执行向字线下的存储单元写入测试数据;测试单元11还用于在设定的预充电操作时长内,执行对所有位线的预充电,并在预充电操作时长结束后,读取字线下的存储单元;比较单元12用于通过比较测试数据和读取的数据,确定字线下的故障存储单元;第二确定模块20,用于根据存储阵列中所有字线下的故障存储单元,确定存储阵列中的故障单元。本实施例通过对写入时长和预充电操作时长的卡控设定了较高的读写测试要求,有利于提高读写故障抓取率,有效筛选出线上不稳定的产品,进而提高产品质量。

149.实施例三

150.图14为本技术实施例提供的一种电子设备的结构示意图,如图14所示,电子设备包括:

151.处理器(processor)291,电子设备还包括了存储器(memory)292;还可以包括通信接口(communication interface)293和总线294。其中,处理器291、存储器292、通信接口293、可以通过总线294完成相互间的通信。通信接口293可以用于信息传输。处理器291可以调用存储器292中的逻辑指令,以执行上述实施例的方法。

152.此外,上述的存储器292中的逻辑指令可以通过软件功能单元的形式实现并作为独立的产品销售或使用时,可以存储在一个计算机可读取存储介质中。

153.存储器292作为一种计算机可读存储介质,可用于存储软件程序、计算机可执行程序,如本技术实施例中的方法对应的程序指令/模块。处理器291通过运行存储在存储器292

中的软件程序、指令以及模块,从而执行功能应用以及数据处理,即实现上述方法实施例中的方法。

154.存储器292可包括存储程序区和存储数据区,其中,存储程序区可存储操作系统、至少一个功能所需的应用程序;存储数据区可存储根据终端设备的使用所创建的数据等。此外,存储器292可以包括高速随机存取存储器,还可以包括非易失性存储器。

155.本技术实施例还提供了一种计算机可读存储介质,计算机可读存储介质中存储有计算机执行指令,计算机执行指令被处理器执行时用于实现实施例提供的方法。

156.本领域技术人员在考虑说明书及实践这里公开的发明后,将容易想到本技术的其它实施方案。本技术旨在涵盖本技术的任何变型、用途或者适应性变化,这些变型、用途或者适应性变化遵循本技术的一般性原理并包括本技术未公开的本技术领域中的公知常识或惯用技术手段。说明书和实施例仅被视为示例性的,本技术的真正范围和精神由下面的权利要求书指出。

157.应当理解的是,本技术并不局限于上面已经描述并在附图中示出的精确结构,并且可以在不脱离其范围进行各种修改和改变。本技术的范围仅由所附的权利要求书来限制。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。