1.本发明涉及电路设计技术领域,特别是一种离散忆阻器模拟电路及其设计方法。

背景技术:

2.1971年,蔡少棠教授基于电路完备性理论提出忆阻器的概念。2008年,惠普实验室利用tio2和金属铂首次实现了世界上首款纳米级忆阻器物理器件。从此掀起了忆阻器的研究热潮,使得忆阻器在图像处理、存储器、神经网络、神经动力学等领域都有了较深入的应用研究。但是,前面提到被广泛应用研究的忆阻器都是连续忆阻。对于离散忆阻器概念,虽然在2013年在材料领域被提出,但其并没有在数理基础上进行解释以及工程应用领域实现。在2018年,karthikeyan等人报道了分数阶离散忆阻器混沌映射,但其主要思想是通过离散连续忆阻器来获得离散迭代模型,而不是直接提出离散忆阻器数学模型,因此他们所提出的模型仍然只能用于连续系统或模拟系统中。如果要在离散系统或者其它数字领域中引入忆阻器做进一步应用研究,需要设计离散型忆阻器并开展离散忆阻仿真器设计研究。

3.连续忆阻器的定义为:

[0004][0005]

其中,v(t)为连续忆阻的输入电压,i(t)是输入电流,k为常数。式中连续忆阻内部电荷的表达式定义为:

[0006][0007]

再令电荷初始值为:

[0008][0009]

代入电荷初始值,得到内部电荷最终表达式为:

[0010][0011]

用模拟电路实现连续忆阻器时,关键在于(1)式中第二个等式的实现,通常采用由电阻电容以及运算放大器组成的积分电路,并通过设置电容c的初值来控制电荷初始值的输入。

[0012]

根据运算放大器虚短虚断以及基尔霍夫等定律,从积分电路中可以得到其输出电荷q(t)以及输入电流i(t)之间的关系为:

[0013][0014]

令:

[0015][0016]

即得到:

[0017][0018]

即可以通过调节电阻r与电容c的取值改变常数k的值。

[0019]

连续忆阻器与离散忆阻的模拟电路实现有相似之处,都主要使用运算放大器等实现加减法等运算,但是连续忆阻采用积分电路实现微分算子,离散忆阻计算则采用采样保持电路实现差分算子。

[0020]

现对于连续忆阻器的等效电路实现,离散忆阻器主要是结合运算放大器、数字模拟混合电路和有源放大器等构建其模拟电路,电路中主要采用积分电路或电流传输计等来实现忆阻器的相关特性。目前的离散忆阻器等效电路实现主要由fpga、dsp等数字电路实现,但其存在有限精度效应。相比于构建连续忆阻的电容等器件产生的是连续信号,离散忆阻器的模拟电路实现则需要寻找适合的能够输出离散信号或者能够实现延迟效果的元器件来离散模拟电路对应的模拟电路。

[0021]

离散忆阻器较连续忆阻器更有利于忆阻器在数字电路和离散领域中的应用。但目前离散忆阻还处于研究初期,具有较大的研究空间。

技术实现要素:

[0022]

本发明所要解决的技术问题是,针对现有技术不足,提供一种离散忆阻器模拟电路及其设计方法,解决现有离散忆阻器等效电路精度有限的问题。

[0023]

为解决上述技术问题,本发明所采用的技术方案是:一种离散忆阻器模拟电路,包括:

[0024]

第一反相加法器,用于实现输入电荷的迭代累加,得到第一累加值;

[0025]

第一反相器,用于使所述第一累加值恢复正值,得到忆阻内部电荷qn;

[0026]

采样保持电路,输入端接第一反相器的输出端,输出端接第一反相加法器的负输入端;

[0027]

第二反相器,负输入端和输出端均与所述采样保持电路连接,为所述采样保持电路输入相反相位的脉冲电压;

[0028]

第二反相加法器,用于实现以下运算:v(tn)=(α-βqn)i(tn),其中,α和β为忆阻参数,i(tn)为离散忆阻的输入电流,v(tn)为最终离散忆阻输出电压;

[0029]

电压跟随器,正输入端与输入电源连接;

[0030]

乘法器,输入端与第二反相加法器的输出端、电压跟随器的输出端连接。

[0031]

现有的基于数字处理器实现的数字电路,其本身精度是有限的,比如设计混沌电路会产生混沌退化的现象,而本发明的模拟电路实现并非基于有限精度的处理器,从而能够产生真正意义上的混沌,解决了现有离散忆阻器等效电路精度有限的问题,对离散忆阻物理意义解释以及工程应用具有重要的意义。同时,本发明基于模拟电路实现,可以为后续离散忆阻集成电路实现提供实验基础,方便离散忆阻在大规模集成电路中的应用实现。

[0032]

所述第一反相加法器包括:

[0033]

第一运算放大器;

[0034]

所述第一运算放大器正输入端接地,负输入端接第一电阻、第二电阻和第三电阻一端,所述第一电阻输入端接输入电源;

[0035]

所述第二电阻另一端接所述采样保持电路输出端;

[0036]

所述第三电阻另一端接所述第一运算放大器的输出端。

[0037]

所述第一反相器包括第二运算放大器,所述第二运算放大器的负输入端接第四电阻、第五电阻一端;所述第四电阻另一端接所述第一运算放大器输出端;所述第五电阻另一端接所述第二运算放大器的输出端;所述第二运算放大器的正输入端接地。

[0038]

所述采样保持电路包括两个采样保持器;第一采样保持器输入端接所述第二运算放大器的输出端,所述第一采样保持器输出端接第二采样保持器的输入端;所述第二采样保持器的输出端接所述第二电阻。

[0039]

第一采样保持器处于采样的状态,当信号经过第一采样保持器被采样从而离散化,第二采样保持器受到与第一采样保持器相反的脉冲信号控制,处于保持的状态,使采样过后的信号值保持现有值直到下一个采样脉冲信号,从而实现了原信号的延迟。

[0040]

运用前向差分推导出了离散忆阻内部电荷的计算公式,最后表达式为一个电荷和输入电流之间的累加迭代式,实现了使用加法运算来实现离散忆阻器内部电荷的计算,在电路中可以使用加法器(第一反相加法器和第二反相加法器)来表述电荷和输入电流之间的关系。本发明运用第一反相加法器实现迭代累加的过程,再通过第一反相器将它恢复成正值,实现迭代过程。

[0041]

所述第二反相器包括第三运算放大器,所述第三运算放大器负输入端接第六电阻、第七电阻一端;所述第六电阻另一端接所述第一采样保持器控制端;所述第七电阻另一端接所述第三运算放大器输出端;所述第三运算放大器输出端接第二采样保持器控制端。

[0042]

所述第二反相加法器包括第五运算放大器;所述第五运算放大器负输入端接第八电阻、第九电阻和第十电阻一端;所述第八电阻另一端接所述采样保持电路的器输出端;所述第九电阻另一端接直流电源;所述第十电阻另一端接所述第五运算放大器输出端。由于直流输入0.1v值太小,避免产生较大误差,采用输入1v的直流电压,再经过反相加法器电阻之间的比例关系实现α值0.1v的输入。

[0043]

作为一个发明构思,本发明还提供了一种忆阻器模拟电路设计方法,采用下述忆阻器数学模型设计本发明上述离散忆阻器模拟电路:

[0044][0045]

其中,n=0,1,2,3,

…

, ∞;δq(tn)=q(t

n 1

)-q(tn);m(q(tn))=α-βq(tn);k=1;q(tn)为tn时刻内部电荷,内部电荷初始值设置为零;其中忆阻器为金属和氧化物构成的惠普忆阻器,其主体宽度设为d,掺杂层宽度设为w,当电流正向流动时,有氧空位的移动导致掺杂层宽度w变宽,忆阻器阻值变小,且当w无限接近于d时忆阻器有最小阻值r

on

;当电流反向流动时,有氧空缺位的移动导致掺杂层宽度w变窄,忆阻器阻值变大,且当w无限接近于0时忆阻器有最大值r

off

,用μv表示掺杂离子的迁移率,就有忆阻参数α=r

off

,d为忆阻器主体宽度,w为忆阻器掺杂层宽度,r

on

为忆阻器的最小阻值,μ

ν

表示掺杂离子的迁移率。

[0046]

本发明中,α取值为0.1,β取值为0.01。

[0047]

与现有技术相比,本发明所具有的有益效果为:本发明采用两个受相反逻辑脉冲信号控制的采样保持器来实现信号的离散化和延迟,最终实现离散忆阻内部变量的累加以

及迭代运算,同时实现了连续信号的离散以及信号的延迟,不需要将两个过程分开处理,并且相比于数字电路实现,用模拟电路可以突破精度的限制;本发明使用模拟电路实现了结合差分算子所构建的离散忆阻器,一方面可验证离散忆阻器的物理意义,另一方面可以进一步拓广离散忆阻模型的应用研究;本发明用模拟电路实现离散忆阻器,更有利于离散忆阻在离散混沌系统中的进一步应用。

附图说明

[0048]

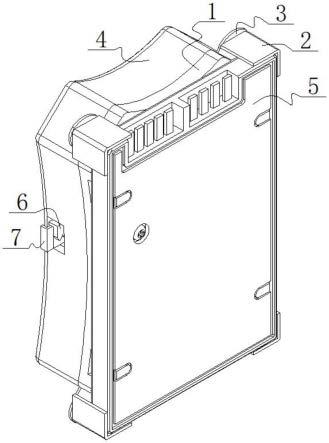

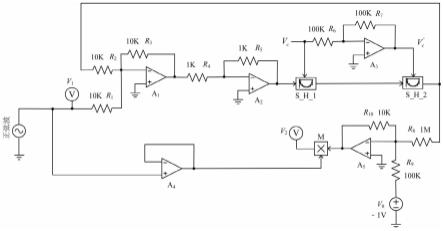

图1为本发明实施例离散忆阻器模拟电路图;

[0049]

图2(a)、图2(b)和图2(c)分别为结合psim对本发明实施例的离散忆阻器进行模拟仿真,保持输入正弦波幅值为1v,频率分别为20hz、25hz、30hz,采样频率为1khz,采样幅值为4v的仿真结果图;

[0050]

图3(a)、图3(b)和图3(c)分别为结合psim对本发明实施例的离散忆阻器进行模拟仿真保持输入正弦波频率为25hz,幅值分别为0.9v、1v、1.1v,采样频率为1khz,采样幅值为4v时的仿真结果图;

[0051]

图4(a)、图4(b)和图4(c)分别为结合实际电路实验对本发明实施例的离散忆阻器进行验证,保持输入正弦波幅值为1v,频率分别为20hz、25hz、30hz,采样频率为1khz,采样幅值为4v的测试结果图;

[0052]

图5(a)、图5(b)和图5(c)分别为结合实际电路实验对本发明实施例的离散忆阻器进行验证保持输入正弦波频率为25hz,幅值分别为0.9v、1v、1.1v,采样频率为1khz,采样幅值为4v时的测试结果图;

具体实施方式

[0053]

现有技术中,离散忆阻器主要是在材料领域或将连续忆阻离散化,都不能直接应用到离散系统中。本发明结合前向差分算子建立离散忆阻的数学模型,可以直接在到离散系统或数字领域中应用。

[0054]

结合前向差分算子所提出的离散忆阻器数学模型,其定义为:

[0055][0056]

其中,n=0,1,2,3,

…

∞,δq(tn)=q(t

n 1

)-q(tn)为前向差分。因为

[0057][0058]

等号两边相加,则忆阻“内部电荷”计算式为

[0059][0060]

在此基础上,惠普(hewlett-packard,简记为hp)忆阻器模型表达式为:

[0061]

v(tn)=(α-βqn)i(tn)

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(11)

[0062]

其中,α和β为忆阻参数,α=r

off

,qn为忆阻内部电荷。设置忆阻参数α值为0.1,β为0.01,即表达式为:

[0063]

v(tn)=(0.1-0.01qn)i(tn)

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(12)

[0064]

由于是离散系统,式(8)中对于初始电荷值的输入以及电荷的叠加不能直接使用积分电路再离散化实现,否则仍然无法用于离散系统,因此选用反相加法器实现叠加,利用采样保持器将信号离散化和延迟。对于电荷初始值可以在反相加法器中使用直流电源来输入,式(8)中k的值同样是利用反相加法器的输入电阻及反馈电阻之间的比值实现。在本发明实施例中,k=1,内部电荷初始值设置为零。对于两个受相反脉冲信号控制的采样保持器,将反相加法器输出的q

n 1

离散化并做延迟得到qn,再输入到反相加法器中进行累加,其延迟时间为一个周期内低电平所占时间,因此,需要合理调节脉冲信号输入频率以控制延迟时间长短。

[0065]

根据hp离散忆阻器的表达式(12),结合模拟器件对其进行模拟电路实现,设计的模拟电路包括运算放大器a1、运算放大器a2、运算放大器a3、运算放大器a4、运算放大器a5、采样保持器s_h_1、采样保持器s_h_2、乘法器m、外围电阻以及输入的直流源、正弦电压源和逻辑控制信号。其中运算放大器a1与电阻r1、r2、r3构成反相加法器,实现电荷qn的迭代累加的过程;运算放大器a2与电阻r4、r5实现反相器,使迭代过后的值恢复正值;运算阿放大器a3与电阻r6、r7构成反相加法器,将输入的脉冲信号进行反相;运算放大器a4为电压跟随器,用于隔离功率器件和逻辑器件;运算放大器a5与电阻r8、r9、r

10

也构成反相加法器,不仅实现忆阻参数值β的表述还实现hp离散忆阻器表达式(12)中的加法运算;两个采样保持器作为关键元件,并通过由a3及其外围电阻构成的反相器给两个采样保持器输入相位相反的脉冲电压,使得采样保持的状态正好相反,从而实现将连续信号离散化之后再将其做时间延迟;乘法器m,用来实现电流信号和忆阻值的乘积,并输出最后结果;直流源输入-1v的直流电压,然后经过运算放大器a5与其外围电阻组成的反相加法器中比例变换作用之后实现初始忆阻参数α值的表述;正弦信号源作为初始输入,用来输入正弦信号,验证所设计忆阻器电路的正确性。

[0066]

目前,离散忆阻还没有模拟电路实现,尚且可以结合psim仿真软件对其进行数值仿真以及结合数字电路对其进行fpga或dsp实现。而数值仿真没有真正的物理实体,离散忆阻作为一个器件,需要有相应的模拟电路实现从而清晰的解释其物理意义;对于使用数字电路实现离散忆阻器,数字电路的精度有限,不能实现真正意义上的混沌,而模拟电路能实现真正意义上的混沌,因此用模拟电路实现离散忆阻器更有利于离散忆阻在离散混沌系统中的进一步应用。除此之外,本发明不同于连续忆阻模拟电路中的积分电路来实现忆阻器内部电荷的计算,这里使用的是采样保持器来实现连续信号的离散化,以及信号的延迟,结合运算放大器和外围电阻构成的反相加法器最终实现内部电荷的迭代。

[0067]

对于目前的技术,我们可以结合psim仿真软件对所设计的离散忆阻器进行模拟仿真,保持输入正弦波幅值为1v,频率分别为20hz、25hz、30hz,采样频率为1khz,采样幅值为4v,仿真结果如图2(a)、图2(b)和图2(c)所示;保持输入正弦波频率为25hz,幅值分别为0.9v、1v、1.1v,采样频率为1khz,采样幅值为4v,仿真结果如图3(a)、图3(b)和图3(c)所示。

[0068]

实物测试利用面包板搭建,测试输入电流和输出电压之间的关系图,保持输入正

弦波幅值为1v,频率分别为20hz、25hz、30hz,采样频率为1khz,采样幅值为4v,测试结果如图4(a)、图4(b)和图4(c)所示;保持输入正弦波频率为25hz,幅值分别为0.9v、1v、1.1v,采样频率为1khz,采样幅值为4v,测试结果如图5(a)、图5(b)和图5(c)所示。可见,测试结果出现了斜8字形滞回曲线,并且滞回曲线随着输入信号幅值的增大而增大,随着输入信号频率增大而减小,最终退化为线性器件,满足广义忆阻器的忆阻定义,且实验测试结果与利用psim仿真结果基本一致,再次验证了本发明所构建离散忆阻模拟电路的正确性。

[0069]

本发明实施例的模拟电路中电阻r1一端与输入的正弦波相连,电阻r1另一端与运算放大器a1的负输入端相连;电阻r2的一端与两级采样保持器的输出端相连,电阻r2的另一端与运算放大器a1的负输入端相连;电阻r3的一端与运算放大器a1的输出端相连,电阻r3的另一端与运算放大器a1的负输入端相连;电阻r4的一端与运算放大器a2的负输入端相连,电阻r4的另一端与运算放大器a1的输出端相连;电阻r5的一端与运算放大器a2的输出端相连,电阻r5的另一端与运算放大器a2的负输入端相连;电阻r6的一端与运算放大器a3的负输入端相连,电阻r6的另一端与采样保持器s_h_1的逻辑控制端一同接入脉冲信号vc;电阻r7的一端与运算放大器a3的负输入端相连,电阻r7的另一端与运算放大器a3的输出端相连;采样保持器s_h_1的输入端接到运算放大器a2的输出端,采样保持器s_h_2的输出端接到电阻r2,两个采样保持器之间采用级联的方式,即采样保持器s_h_1的输出端接入到采样保持器s_h_2的输入端,并且两个采样保持器分别采用vc及其经过反相器得到的vc'两个相反的逻辑信号控制;电阻r8的一端与采样保持器s_h_2输出端相连,电阻r8的另一端与运算放大器a5的负输入端相连;电阻r9的一端与运算放大器a5的负输入端相连;电阻r9的另一端与输入的直流电源相连;电阻r

10

的一端与运算放大器a5的输出端相连,电阻r

10

的另一端与运算放大器a5的负输入端相连;运算放大器a5的输出连接到乘法器的一个输入端,输入的正弦电压信号经过运算放大器a4后与乘法器的另一个输入端相连;乘法器输出最终结果。最后用示波器检测被发明的输入信号v1输出信号v2,从而验证其正确性。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。