1.本发明属于半导体技术领域,特别涉及一种半导体器件的制作方法。

背景技术:

2.随着半导体器件集成度的不断提高,半导体器件微小化是一个普遍趋势。且需要将多种类型的器件集成在一起进行制作,例如同一衬底上制备不同类型的晶体管,其中,高压晶体管的栅极氧化层的厚度较厚。为确保形成的栅极氧化层的准确性,在形成栅极材料层之前,先通过刻蚀形成栅极氧化层,再形成栅极材料层时,栅极材料层存在显著的高低差,在栅极制备过程中,易在栅极氧化层的两侧残留部分栅极材料层,从而导致晶体管电性异常,造成半导体器件的制作良率下降。

3.因此,如何获得高良率的高性能半导体器件成为亟需解决的问题。

技术实现要素:

4.本发明的目的在于提供一种半导体器件的制作方法,通过本发明提供的一种半导体器件的制作方法,可以避免栅极材料层残留,提高半导体器件的制作良率。

5.为解决上述技术问题,本发明是通过以下技术方案实现的:本发明提供一种半导体器件的制作方法,其至少包括:提供一衬底;在所述衬底上形成栅极氧化层;在所述衬底和所述栅极氧化层上形成栅极材料层;在所述栅极材料层上形成平坦层;刻蚀所述平坦层和所述栅极材料层,形成栅极;在所述衬底中形成源极,且所述源极位于所述栅极的一侧;以及在所述衬底中形成漏极,且所述漏极位于所述栅极的另一侧。

6.在本发明一实施例中,所述平坦层的形成步骤包括:在所述栅极材料层上形成平坦材料层;在所述平坦材料层上形成光阻层,且所述光阻层表面平整;以及刻蚀所述光阻层和部分所述平坦材料层,获取表面平整的所述平坦层。

7.在本发明一实施例中,所述光阻层和所述平坦材料层采用干法刻蚀,且刻蚀气体包括四氟化碳、氧气、六氟化硫、氯气、二氧化硫或羰基硫中的一种或几种混合。

8.在本发明一实施例中,所述光阻层和所述平坦材料层的刻蚀速率相同。

9.在本发明一实施例中,所述平坦层包括非定型碳层或类金刚石层。

10.在本发明一实施例中,所述半导体器件的制作方法还包括:在所述平坦层上形成抗反射层和底部抗反射层。

11.在本发明一实施例中,所述半导体器件的制作方法还包括:刻蚀所述抗反射层和所述底部抗反射层,定位所述栅极的位置。

12.在本发明一实施例中,在所述抗反射层、所述底部抗反射层、所述平坦层和所述栅极材料层的刻蚀过程中,固定所述半导体器件的位置,在刻蚀到不同层时更换刻蚀气体,以实现所述栅极的自对准。

13.在本发明一实施例中,所述半导体器件的制作方法还包括:在形成所述栅极后,向刻蚀腔室内通入氧气,去除所述平坦层。

14.在本发明一实施例中,所述氧气的流量为7000sccm~9000sccm。

15.本发明提供的一种半导体器件的制作方法,能够减少在形成栅极时,栅极材料层在衬底上的残留,提高半导体器件的电学性能。减少栅极在衬底上残留的现象,精准控制栅极的形状与尺寸,增加半导体器件的效能。满足在同一衬底上不同功能的半导体器件的性能,获得高质量半导体器件。

16.当然,实施本发明的任一产品并不一定需要同时达到以上所述的所有优点。

附图说明

17.为了更清楚地说明本发明实施例的技术方案,下面将对实施例描述所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

18.图1为一实施例中衬底分布示意图。

19.图2为一实施例中浅沟槽隔离结构示意图。

20.图3为一实施例中阱区分布示意图。

21.图4为一实施例中氧化层结构示意图。

22.图5为一实施例中第一栅极氧化层示意图。

23.图6为一实施例中第二栅极氧化层示意图。

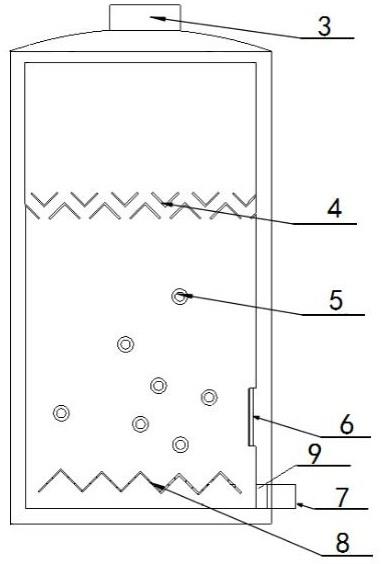

24.图7为一实施例中平坦材料层和光阻层结构示意图。

25.图8为一实施例中抗反射层和底部抗反射层结构示意图。

26.图9为一实施例中刻蚀到平坦层时器件结构示意图。

27.图10为一实施例中刻蚀到栅极材料层时器件结构示意图。

28.图11为一实施例中刻蚀完栅极材料层时器件结构示意图。

29.图12为一实施例中栅极示意图。

30.图13为一实施例中侧墙结构示意图。

31.图14为一实施例中轻掺杂区结构意图。

32.图15中一实施例中形成凹槽结构示意图。

33.图16为一实施例中应力层结构示意图。

34.图17为一实施例中自对准硅化物阻挡层结构示意图。

35.图18为一实施例中半导体器件结构示意图。

36.标号说明:110衬底;1第一区域;2第二区域;120垫氧化层;130垫氮化层;140第一图案化光阻层;141凹部;142第二图案化光阻层;143第三图案化光阻层;150浅沟槽隔离结构;160第一阱区;170第二阱区;180氧化层;181第一栅极氧化层;182第二栅极氧化层;190栅极材料层;

vapor deposition,cvd)等方法制备。在垫氧化层120上形成垫氮化层130,且垫氮化层130例如为氮化硅或氮化硅和氧化硅的混合物,垫氮化层130可通过化学气相淀积等方法形成。在形成浅沟槽隔离结构过程中,垫氧化层120可以改善衬底110与垫氮化层130之间的应力,同时可在进行离子注入形成阱区时,保护衬底110,防止衬底110被高能量离子损伤。在垫氮化层130上形成第一图案化光阻层140,第一图案化光阻层140上设置多个凹部141,凹部141用来定义浅沟槽隔离结构150的位置,且凹部141暴露出垫氮化层130。

44.请参阅图1至图2所示,在本发明一实施例中,在形成第一图案化光阻层140后,以第一图案化光阻层140为掩膜,例如使用干法刻蚀向衬底110的方向进行刻蚀,形成浅沟槽,且刻蚀气体例如可以是氯气(cl2)、三氟甲烷(chf3)、二氟甲烷(ch2f2)、三氟化氮(nf3)、六氟化硫(sf6)、溴化氢(hbr)或氮气(n2)等中的一种或几种混合。在浅沟槽内例如通过热氧化法在浅沟槽内形成一内衬氧化层(图中未显示),以修复在形成浅沟槽的过程中的刻蚀损伤,减少半导体器件漏电情况。在浅沟槽内例如通过高密度等离子体化学气相淀积(high density plasma cvd,hdp-cvd)或高深宽比化学气相淀积(high aspect ratio process cvd,harp-cvd)等方式沉积隔离介质,且隔离介质例如为氧化硅等绝缘物质。在隔离介质沉积完成后,例如通过化学机械抛光(chemical mechanical polishing,cmp)工艺平坦化隔离介质和垫氮化层130,形成浅沟槽隔离结构150,且浅沟槽隔离结构150高于垫氧化层120。

45.请参阅图3所示,在本发明一实施例中,在浅沟槽隔离结构150制备完成后,对衬底110进行离子注入,以形成不同的阱区。首先,以高注入能量注入比衬底110浓度高的掺杂区,即在衬底110内形成第一阱区160。在形成nmos晶体管的区域以高注入能量注入比第一阱区160浓度高的掺杂离子,以形成第二阱区170,且第二阱区170位于部分第一阱区160上。在本实施例中,第一阱区160和第二阱区170的类型不同,其中,第一阱区160例如设置为n型深阱,掺杂离子为磷(p)、砷(as)或铝(al)等,第二阱区170例如设置为p型深阱,掺杂离子为硼(b)或镓(ga)等。在第一阱区160和第二阱区170形成后,对在第一阱区160和第二阱区170进行快速热退火制程(rapid thermal anneal,rta)在本实施例中,退火温度例如为1000~1400℃,退火时间例如为1h~3h,且退火制程是在惰性气体氛围下进行,例如在氮气氛围下进行。通过退火制程,使得第一阱区160和第二阱区170的离子注入至合适深度,同时提高半导体器件的抗雪崩击穿能力。

46.请参阅图3至图4所示,在本发明一实施例中,在第一阱区160和第二阱区170形成之后,去除垫氧化层120。在本实施例中,例如采用湿法刻蚀去除垫氧化层120,且湿法刻蚀液例如选用氢氟酸,在常温下进行刻蚀。在其他实施例中,也可采用其他刻蚀方式,根据具体的制作要求进行选择。去除垫氧化层120后,在衬底110上形成氧化层180,且氧化层180在第一区域1和第二区域2的厚度不同,氧化层180在第二区域2的厚度例如为50nm~75nm,氧化层180在第一区域1的厚度例如为氧化层180在第二区域2的厚度的三分之一至三分之二。在本实施例中,氧化层180例如通过原子层沉积法(atomic layer deposition,ald)、金属有机气相沉积法(metal-organic chemical vapor deposition,mocvd)化学气相沉积法或物理气相沉积法(physical vapor deposition,pvd)等方法形成,氧化层180例如为氧化铪(hfo2)、氮氧化铪(hfon)、氧化锆(zro2)或一氧化铝(alo)等高介电常数介质材料。在本实施例中,例如先沉积高介电常数介质材料,在沉积完成后,分别对第一区域1和第二区域2进行图案化并刻蚀,分别形成制作要求厚度的氧化层180。在其他实施例中,也可以先在第一区

域1沉积氧化层180,再在第二区域2沉积氧化层180,且沉积的氧化层180的厚度不同。

47.请参阅图5至图6所示,在本发明一实施例中,在氧化层180形成后,对氧化层180进行刻蚀以形成栅极氧化层,且栅极氧化层包括第一栅极氧化层181和第二栅极氧化层182。具体地,例如采用湿法刻蚀去除部分氧化层180,且湿法刻蚀液例如选用氢氟酸,在常温下进行刻蚀。在其他实施例中,也可采用其他刻蚀方式,根据具体的制作要求进行选择。具体地,在第二区域2形成第二图案化光阻层142,对第一区域1的氧化层180进行刻蚀,在第一区域1上形成第一栅极氧化层181,后去除第二图案化光阻层142。在第一区域1形成第三图案化光阻层143,对第二区域2的氧化层180进行刻蚀,在第二区域2上形成第二栅极氧化层182,然后去除第三图案化光阻层143,以在第一区域1和第二区域2形成不同厚度的第一栅极氧化层181和第二栅极氧化层182。以满足在同一衬底上,同时制备不同压力要求的半导体器件。

48.请参阅图7所示,在本发明一实施例中,在形成第一栅极氧化层181和第二栅极氧化层182后,在第一栅极氧化层181、第二栅极氧化层182、衬底110以及浅沟槽隔离结构150上形成栅极材料层190,且栅极材料层190的厚度例如为10nm~300nm,在其他实施例中,栅极材料层190的厚度可根据制作要求进行选择。在本实施例中,栅极材料层190例如通过化学气相沉积或原子层沉积法等方法制备,且栅极材料层190例如为多晶硅、钨、氮化钨或硅化钨等材料。且由于衬底110的表面上存在栅极氧化层和部分浅沟槽隔离结构150,因此,栅极材料层190在第一栅极氧化层181和第二栅极氧化层182的两侧形成凹陷。

49.请参阅图7所示,在本发明一实施例中,在形成栅极材料层190后,在栅极材料层190上形成平坦材料层201。在本实施例中,平坦材料层201例如为非定型碳(advanced patterning film,apf)或类金刚石层(diamond-like carbon,dlc)等与光阻刻蚀速率相同材料,具体例如为非定型碳层。在平坦材料层201形成光阻层202,且光阻层202例如通过旋涂或涂布等工艺,以使光阻层202的表面平整。在光阻层202形成后,对光阻层202和部分平坦材料层201进行刻蚀,刻蚀完成后,形成平坦层200,平坦层200远离栅极材料层190的表面位于同一水平面内。在本实施例中,例如采用干法刻蚀,且刻蚀气体例如为四氟化碳(cf4)、氧气(o2)、六氟化硫(sf6)、氯气(cl2)、二氧化硫(so2)或羰基硫(cos)等刻蚀气体中的一种或几种混合,且气体的流速例如为10sccm~200sccm,刻蚀时间例如为20s~300s。因光阻层202和平坦材料层201的刻蚀速率相同,通过控制刻蚀时间,确保刻蚀完成后,获得的平坦层200远离衬底110的一侧位于同一平面内。通过设置平坦材料层201,使栅极材料层190的高度差落在平坦层200,以避免高度差落在底部抗反射涂层上。通过在栅极材料层上形成平坦层,可以避免在形成栅极的过程中,避免由于高度差落在底部抗反射涂层上,因底部抗反射涂层的残留导致栅极材料层的残留,降低半导体器件的性能,从而提高半导体器件的性能。

50.请参阅图8所示,在本发明一实施例中,在形成平坦层200后,在平坦层200上形成抗反射层210和底部抗反射层220,其中,抗反射层210设置在平坦层200上,底部抗反射层220设置在抗反射层210上。在本实施例中,抗反射层210例如为氮氧化硅(sion)等材料,且抗反射层210例如通过化学气相沉积法制备,底部抗反射层220例如为聚羟基苯乙烯(phs)、甲基丙烯酸酯、丙烯酸酯或萘等有机涂层,又例如为氮化钛(tin)以及氮氧化硅等无机材料组成,且底部抗反射层220例如通过化学气相沉积或旋涂等方式形成。其中,抗反射层210的厚度例如为10nm~200nm,底部抗反射层220的厚度例如为10nm~150nm。在底部抗反射层220

上形成第四图案化光阻层230,通过刻蚀,以形成栅极。通过形成抗反射层210和底部抗反射层220,能够减少反射和驻波等问题,提高刻蚀制程的准确性。

51.请参阅图8至图9所示,在本发明一实施例中,以第四图案化光阻层230为掩膜,进行刻蚀,以形成栅极。在本实施例中,例如采用干法刻蚀的方法对抗反射层210和底部抗反射层220进行刻蚀,将衬底110放入刻蚀腔室内,将腔室内的压力控制在例如为7mtorr~12mtorr,向腔室内通入cl2、o2或其组合,且气体流量例如为2sccm~150sccm,刻蚀时间例如为30~300s。控制刻蚀时间,当底部抗反射层220刻蚀完成后,将刻蚀气体更换为溴化氢(hbr)、三氟甲烷(chf3)或其组合,且气体流量例如为30sccm~80sccm,刻蚀时间例如为30s~300s。在其他实施例中,也可选择其他刻蚀方法对抗反射层210和底部抗反射层220进行刻蚀。因栅极氧化层高度不同而形成的高度差在平坦层200已进行找平,抗反射层210和底部抗反射层220在刻蚀过程中不会存在残留,确保刻蚀图形的准确性。

52.请参阅图10至图11所示,在本发明一实施例中,在抗反射层210和底部抗反射层220刻蚀完成后,此时,第四图案化光阻层230也被完全刻蚀,继续进行刻蚀。以底部抗反射层220为掩膜,更换刻蚀气体,对平坦层200进行刻蚀,将腔室内的压力控制在7mtorr~12mtorr,且刻蚀气体例如为cl2、o2或其组合,气体流量例如为30sccm~200sccm,刻蚀时间例如为30s~500s。当平坦层200刻蚀完成后,底部抗反射层220也刻蚀完全,此时,以抗反射层210为掩膜,更换刻蚀气体,对栅极材料层190进行刻蚀,以形成栅极191。具体地,在腔室内的压力控制在7mtorr~12mtorr,且刻蚀气体例如为cf4、sf6、o2或其组合,气体流量例如为5sccm~100sccm,刻蚀时间例如为30s~800s。因在刻蚀栅极材料层190时,在栅极材料层190上,不存在平坦层200、抗反射层210和底部抗反射层220的残留,因此,在刻蚀栅极材料层190层时,不会在衬底110上存在栅极材料层190残留,且减少因为防止栅极材料层残留而延长刻蚀时间,导致的栅极尺寸减小的现象,从而提高器件性能。栅极191的形成过程在同一刻蚀过程中即可完成,在刻蚀过程中,只需要一道光阻,通过自对准工艺,对刻蚀条件进行控制,即可形成形状良好的栅极191,且简化制作流程,节约制作成本。

53.请参阅图11至图12所示,在本发明一实施例中,在栅极191形成后,在栅极191上残留部分平坦层200。在本实施例中,当栅极材料层190刻蚀完成后,将腔室的压力控制在700mtorr~1000mtorr,向腔室内通入o2,且o2的流量例如为7000sccm~9000sccm,以去除残留的平坦层200。

54.请参阅图13所示,在本发明一实施例中,在栅极191形成后,在栅极191的两侧形成侧墙结构240,即侧墙结构240形成于栅极191和第一栅极氧化层181以及栅极191和第二栅极氧化层182的侧面。在本实施例中,侧墙结构240为叠层结构,其中,侧墙结构240例如包括绝缘层和应力层等,绝缘层例如为氧化硅等,应力层例如为氮化硅等。即侧墙结构240为氧化硅层/氮化硅层的叠层,以提高侧墙结构的稳定。在其他实施例中,侧墙结构240也可以为单层绝缘层或其他结构。通过将侧墙结构设置为多层结构,提高侧墙结构的绝缘性,减少漏电现象。

55.请参阅14所示,在本发明一实施例中,在侧墙结构240形成后,在第二阱区170中形成轻掺杂区250,且轻掺杂区250位于侧墙结构240与浅沟槽隔离结构150之间,并与侧墙结构240与浅沟槽隔离结构150相邻,以改善形成的晶体管的短沟道效应。具体地,以较低注入能量注入掺杂离子,因此,形成的轻掺杂区250位于第二阱区170靠近栅极191的一侧。其中,

注入的掺杂离子例如为磷、砷或铝等n型离子,轻掺杂区250可以作为nmos晶体管的源极或漏极。

56.请参阅图15至图16所示,在本发明一实施例中,在形成轻掺杂区250后,在第一阱区160上形成凹槽11,且凹槽11位于侧墙结构240与浅沟槽隔离结构150之间,并与侧墙结构240与浅沟槽隔离结构150相邻。具体地,在衬底110上形成图案化光阻层,通过干法刻蚀或湿法刻蚀第一阱区160上侧墙结构240两侧的衬底110,形成凹槽11。在本实施例中,凹槽11的侧壁呈开口多边形设置,可以扩大后续沉积应力区260与晶体管沟道区域的接触面积,提高沟道区域受到的应力作用,从而提高沟道区域内的迁移率。在凹槽11内沉积半导体材料以形成应力区260,且应力区260可以作为pmos晶体管的源极或漏极。在本实施例中,应力区260例如为硅锗(sige),且sige为掺杂了p型杂质的sige。其中应力区260的形状和凹槽11形状一致,例如为多边形形状,且多边形的一边与浅沟槽隔离结构150相邻,应力区260向栅极191底部延伸,且延伸至侧墙结构240和栅极191连接处。通过设置应力区260延伸至侧墙结构240和栅极191连接处,可避免应力区260延伸至栅极191底部时,而导致的漏电流现象,同时,当应力区260未延伸至侧墙结构240和栅极191连接处时,应力区260之间的沟道区域宽度较大,载流子迁移率降低,影响半导体器件性能。因此,通过将应力区260延伸至侧墙结构240和栅极191连接处时,半导体器件的电性可以达到最好效能。在本实施例中,应力区260例如通过低温外延工艺沉积制备,采用低温外延工艺的外源气体包括锗源气体、硅源气体、氯化氢气体和氢气等,通过调整锗源气体和硅源气体的比例,调节应力区260中锗的比例,且锗的比例例如为20%~40%。通过控制锗的含量,可以减小应力区260与凹槽11内壁的晶格常数差异,减少应力区260内的缺陷。在应力区260形成后,对轻掺杂区250和应力区260进行激活,例如采用将衬底110进行快速热退火。通过快速热退火,能够修复制作过程中产生的晶格缺陷、激活掺杂离子和最小化掺杂离子扩散三者之间取得优化,进而激活应力层和轻掺杂区,且快速热退火还能减小瞬时增强扩散。

57.请参阅图17所示,在本发明一实施例中,在栅极191、轻掺杂区250和应力区260形成自对准硅化物阻挡层(self-aligned block,sab)270。具体地,在栅极191、轻掺杂区250和应力区260上形成金属层(图中未显示),且金属层例如为钛层(ti)、钴层(co)或镍层(ni)等,然后对衬底110进行第一次退火,第一次退火的温度例如为300℃~350℃,使得金属原子与栅极191、轻掺杂区250或应力区260中的硅原子反应,形成中间硅化物层,然后通过化学溶液选择去除未反应的金属层,并对中间硅化物层进行第二次退火,第二次退火的温度比第一次退火的温度高,第二次退火的温度例如为400℃~500℃。中间硅化物层经过退火之后转化为硅化物层,也就是自对准硅化物阻挡层270。自对准硅化物阻挡层270具有良好的热稳定性,可以降低器件的电阻,其保证与后期制备的金属电极接触良好。

58.请参阅图18所示,在本发明一实施例中,在形成自对准硅化物阻挡层270后,在所述衬底110上形成绝缘层20,绝缘层20覆盖全部衬底110的表面,且绝缘层20例如设置为氧化硅层等绝缘物质。在形成绝缘层20后,进行平坦化工艺,且在绝缘层20上设置多个通道,且通道暴露出栅极191、轻掺杂区250以及应力区260上的自对准硅化物阻挡层270,在通道内设置金属连线,例如钨、铜或银等金属,以形成导电插塞。导电插塞包括第一导电插塞21、第二导电插塞22和第三导电插塞23,其中,第一导电插塞21设置在轻掺杂区250或应力区260上,与轻掺杂区250或应力区260上的自对准硅化物阻挡层270连接,以作为晶体管的漏

极引出端。第二导电插塞22设置在栅极191上,且与栅极191上的自对准硅化物阻挡层270连接在,以作为晶体管的栅极引出端。第三导电插塞23位于轻掺杂区250或应力区260上,且与自对准硅化物阻挡层270连接,以作为晶体管的源极引出端。

59.综上所述,本发明提供一种半导体器件的制作方法,由于栅极氧化层造成的高度差在栅极材料层的下一层进行找平,确保在形成栅极时,无残留物,减少栅极在衬底上残留的现象,精准控制栅极的形状与尺寸,增加半导体器件的效能。满足在同一衬底上不同功能的半导体器件的性能,获得高质量半导体器件。

60.以上公开的本发明实施例只是用于帮助阐述本发明。实施例并没有详尽叙述所有的细节,也不限制该发明仅为所述的具体实施方式。显然,根据本说明书的内容,可作很多的修改和变化。本说明书选取并具体描述这些实施例,是为了更好地解释本发明的原理和实际应用,从而使所属技术领域技术人员能很好地理解和利用本发明。本发明仅受权利要求书及其全部范围和等效物的限制。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。