2.本发明属于集成电路加工领域,涉及一种倒装芯片中的镀膜方法。

3.

背景技术:

4.倒装芯片焊接技术是一种新兴的微电子封装技术;它将工作面(有源区面)上制有凸点电极的芯片朝下,与基板布线层直接键合。是在芯片的p极和n极下方用金线焊线机只做的两个金丝球焊点,作为电极的引出机构,用金线来连接芯片外侧和si底板。led芯片通过凸凹点倒装连接到硅基上。这样大功率led产生的热量不必经由芯片的蓝宝石衬底,而是直接传到热导率更高的硅或者陶瓷衬底,再传到金属底座。倒封装芯片对比正封装芯片的具有以下优点:1.没有通过蓝宝石衬底散热,从芯片pn极上的热量通过金丝球焊点传到散热良好的si上;散热效果好;可大电流使用;2.尺寸可以更小;密度更高;增加单位面积i/o数量;光学更容易匹配;3.散热功能和抗静电能力都大幅提升。

5.在现代超大规模集成电路(vlsi:very large scale integration)中,绝缘薄膜被广泛使用,它能够给器件内的导电区域之间提供电隔离,并作为最终的封端钝化层,二氧化硅、氮化硅和氮氧化物被广泛使用。根据沉积温度的不同,可以采用不同的沉积方法。常压化学气相沉积法和低压化学气相沉积法通常要求高于400

°

c的高温,而等离子体增强化学气相沉积法的使用通常要求低于400

°

c的沉积温度。同时由于倒装芯片结构存在有聚合物与掩膜层相互堆叠的情况;而且由于聚合物层的存在,要求工艺的温度不能高于150℃,同时对侧壁覆盖和粘附性都有较高要求。目前常用的pecvd在低温(<200℃)时薄膜的致密性很难满足需求,同时容易在有机层和掩膜层处带来横向开裂的风险。因此人们对在更低的温度(《150

°

c)下沉积高密度介电薄膜的能力非常感兴趣,特别是在有机发光二极管等温度敏感器件中。

6.icp-cvd(电感耦合等离子体化学气相沉积)是利用高频电流所产生的诱导电场使电子加速,维持等离子体,它可以在低温度、低气压下形成大面积,高均匀度和高电子密度的等离子体;快速沉积得到均匀性好,致密度高的优质氮化硅,氧化硅,碳化硅等薄膜。虽然常规的icp-cvd在低温(<200℃)通过高功率实现高质量薄膜的生成;但在高功率的射频影响下容易造成衬底的损伤和薄膜应力的增加;应力的增大极其容易造成薄膜的粘附性差;导致后续工艺中出现薄膜脱落的问题。

7.因此,需要开发出一种在高密度等离子体、低沉积压力和低温度下沉积低应力高质量薄膜的工艺。

8.

技术实现要素:

9.解决的技术问题:针对上述技术问题,本发明提供一种倒装芯片中的镀膜方法。本发明通过控制反应气体及高低频功率分配方式可实现低功率低温条件下进行低应力致密

薄膜生成;同时提高薄膜侧壁覆盖和粘附性。

10.技术方案:本发明提供了一种倒装芯片中的镀膜方法,该方法的步骤如下:步骤1、先准备样品,该样品为倒装芯片;然后将样品传送至icp-cvd设备的反应腔室内,预热样品,使样品的衬底片温度达到薄膜生长温度,通过分子泵将反应腔室腔压抽至5mt以下,然后通入反应气体,所述反应气体包括硅基气体、含氧气体和稀释及溅射气体,同时保持腔室内的反应腔压为5-100mt;步骤2、使用30-200w高频进行启辉预镀膜3-20s;步骤3、同时启动高频和低频进行镀膜3-10s,高频和低频电源功率分别为200-800w、20-200w;步骤4、关闭低频并维持高频进行镀膜1.5-100s;步骤5、循环重复步骤3和步骤4,直至达到预期的膜厚后结束镀膜。

11.进一步的,所述薄膜生长温度为40-200℃。

12.进一步的,所述薄膜生长温度为80-120℃。

13.进一步的,所述硅基气体、含氧气体和稀释及溅射气体的流量分别为10-50sccm、20-1000sccm和50-800sccm。

14.进一步的,所述硅基气体为硅烷、乙硅烷、teos中的一种或多种混合。

15.进一步的,所述含氧气体为o2、n2o、o3或其组合气体中的一种或多种混合。

16.进一步的,所述稀释及溅射气体为h2、he、ar、n2中的一种或多种混合。

17.进一步的,所述步骤4中、镀膜时间为6-20s。

18.进一步的,所述步骤1中、腔室内的反应腔压为15-50mt。

19.有益效果:本发明通过控制反应气体及高低频功率分配方式可实现低功率低温条件下进行低应力致密薄膜生成,同时提高薄膜侧壁覆盖和粘附性;相比现有工艺,本发明方法所制得的薄膜的致密性更好;同期应力对比基本无变化;应力稳定在压应力250mpa;且在后续涂胶光刻工艺未出现薄膜脱落的问题。

20.具体实施方式

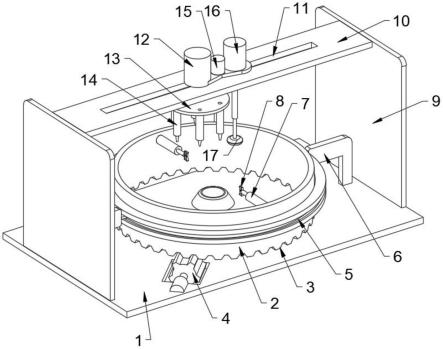

21.本发明所用的icp-cvd设备选用江苏鲁汶仪器有限公司生产的haasrode-c200a电感耦合等离子体化学气相沉积设备。

22.本发明使用腐蚀测试对以下样品的耐腐蚀效果进行模拟测试。腐蚀测试:在室温条件下用6:1boe对样品上的氧化硅进行腐蚀,腐蚀时间为30s-60s/次,至氧化硅腐蚀完全。

23.以下实施例中的腔压控制范围在0-100mtorr。以下实施例中所采用的硅基气体为硅烷、乙硅烷、teos、或其组合气体,含氧气体为o2、n2o、o3或其组合气体,稀释及溅射气体为h2、he、ar、n2、或其组合气体。

24.实施例1本发明提供了一种倒装芯片中的镀膜方法,该方法的步骤如下:步骤1、将样品(倒装芯片)传送至icp-cvd设备的反应腔室内,预热样品,使样品的衬底片温度达到薄膜生长温度120℃(升温前可通过通入一定量的惰性气体提高反应腔室内腔压使得样品迅速升温到设定温度),通过分子泵将反应腔室腔压抽至5mt以下,然后通

入反应气体(50sccmsih4、400sccmn2o 及200sccmar),同时保持腔室内的反应腔压为20mt;步骤2、使用200w高频进行启辉预镀膜20s;步骤3、同时启动高频和低频进行镀膜10s,高频和低频电源功率分别为600w、50w;步骤4、关闭低频并维持高频进行镀膜20s;步骤5、循环重复步骤3和步骤4,直至达到预期的膜厚后结束镀膜。

25.经检测,此工艺方法中sio沉积速率为500nm/min;折射率在1.461-1.463。样品上沉积的氧化硅薄膜的测试结果见表1所示,其腐蚀速度小于300nm/min。

26.现有icp-cvd工艺:先将样品(倒装芯片)传送至icp-cvd设备的反应腔室内,预热样品,使样品的衬底片温度达到薄膜生长温度40-200℃(升温前可通过通入一定量的惰性气体提高反应腔室内腔压使得样品迅速升温到设定温度),通过分子泵将反应腔室腔压抽至5mt以下,然后通入反应气体(50sccmsih4、400sccmn2o 及200sccmar),同时保持腔室内的反应腔压为20mt;再使用200w高频进行启辉预镀膜20s;最后同时启动600w高频和50w低频进行镀膜,直至达到预期的膜厚后结束镀膜。通过腐蚀测试,发现现有icp-cvd工艺中样品上沉积的氧化硅薄膜的腐蚀速率≥500nm/min。

27.对比现有icp-cvd工艺,本发明工艺沉积的薄膜的耐腐蚀性能得到提升,测试发现腐蚀速率从500nm/min(对比现有icp-cvd工艺)降低至220-230nm/min(实施例1),本发明方法所制得的薄膜的致密性更好;同期应力对比基本无变化;经检测应力稳定在压应力250mpa;且在后续涂胶光刻工艺未出现薄膜脱落的问题。

28.表1、实施例1样品的氧化硅薄膜腐蚀速率测试结果。time(min)thickness(nm)e.r(nm/min)02774.7 12544.7230.022315.7229.032080.7235.041859.7221.051631.7228.061397.7234.081168.7229.010930.7238.012692.7238.014455.7237.015225.7230.015.90250.8

29.实施例2本发明提供了一种倒装芯片中的镀膜方法,该方法的步骤如下:步骤1、将样品(倒装芯片)传送至icp-cvd设备的反应腔室内,预热样品,使样品的衬底片温度达到薄膜生长温度80℃,通过分子泵将反应腔室腔压抽至5mt以下,然后通入反应气体(20sccmsih4、200sccmo2、200sccmar),同时保持腔室内的反应腔压为20mt;步骤2、使用200w高频进行启辉预镀膜20s;

步骤3、同时启动高频和低频进行镀膜10s,高频和低频电源功率分别为600w、50w;步骤4、关闭低频并维持高频进行镀膜20s;步骤5、循环重复步骤3和步骤4,直至达到预期的膜厚后结束镀膜。

30.经检测,此工艺方法中sio沉积速率为100nm/min;折射率在1.461-1.463。样品上沉积的氧化硅薄膜的测试结果见表2所示,其腐蚀速度小于200nm/min。

31.表2、实施例2样品的氧化硅薄膜腐蚀速率测试结果。time(min)etch-pre(nm)etch-last(nm)e.r(nm/min)11918.71720.8197.921720.81549.7171.131549.71385.4164.341385.41240.0145.451240.01087.9152.161087.9932.3155.67932.3770.1162.28770.1608.9161.29608.9450.0158.910450.0288.9161.111288.9124.0164.911.8124.00.5154.5

32.实施例3本发明提供了一种倒装芯片中的镀膜方法,该方法的步骤如下:步骤1、将样品(倒装芯片)传送至icp-cvd设备的反应腔室内,预热样品,使样品的衬底片温度达到薄膜生长温度40℃,通过分子泵将反应腔室腔压抽至5mt以下,然后通入反应气体(10sccm乙硅烷、20sccmn2o、50sccmn2),同时保持腔室内的反应腔压为5mt;步骤2、使用200w高频进行启辉预镀膜3s;步骤3、同时启动高频和低频进行镀膜3s,高频和低频电源功率分别为200w、20w;步骤4、关闭低频并维持高频进行镀膜6s;步骤5、循环重复步骤3和步骤4,直至达到预期的膜厚后结束镀膜。

33.实施例4本发明提供了一种倒装芯片中的镀膜方法,该方法的步骤如下:步骤1、将样品(倒装芯片)传送至icp-cvd设备的反应腔室内,预热样品,使样品的衬底片温度达到薄膜生长温度200℃,通过分子泵将反应腔室腔压抽至5mt以下,然后通入反应气体(50sccmteos、1000sccmo3、800sccmhe),同时保持腔室内的反应腔压为100mt;步骤2、使用200w高频进行启辉预镀膜20s;步骤3、同时启动高频和低频进行镀膜10s,高频和低频电源功率分别为800w、200w;步骤4、关闭低频并维持高频进行镀膜20s;步骤5、循环重复步骤3和步骤4,直至达到预期的膜厚后结束镀膜。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。