带有si与有机中介层的先进封装结构及其制造方法

技术领域

1.本发明属于半导体封装领域,尤其涉及一种带有si与有机中介层的先进封装结构及其制造方法。

背景技术:

2.随着人工智能(ai)、数据中心、高性能计算(hpc)、网络和图形加速显卡等多种应用需要更高的内存带宽,先进封装成为支持高带宽内存(hbm,high bandwidth memory)宽i/o的越来越重要的因素。目前主要有三个先进封装技术为业界所使用,台积电tsmc的cowos(chip on wafer on substrate)、英特尔intel的emib(embedded multi-die interconnect bridge)及三星samsung的h-cube。

3.台积电tsmc的cowos:典型的2.5d封装,将processor、logic及hbm的芯片安装在si中介层上、si中介层上有复数层的再分配层(rdl,redistribution layer),分配层布线的线宽线距小于1.2微米(um)。如此细微的布线,可以提供芯片间高及中密度信号的连接,这时fcbga基板(或称载板)无法提供的布线密度,以及中及低密度信号的连接。si中介层再安装在fcbga基板上,si中介层有tsv(through silicon via,通过硅通孔),将上层信号导到下层,再与fcbga基板做信号导通。si中介层晶圆的制作由晶圆厂完成,因为光罩(reticle)及曝光制程设备的限制,si中介层很难做到足够的大来放置很多的芯片,另外成本高是cowos为人诟病的地方。

4.英特尔intel的emib:intel的作法是将昂贵si中介层尺寸缩小,si中介层没有tsv(through silicon via,通过硅通孔),将上层信号导到下层,因为信号只在si中介层表面的rdl内传输,没有tsv潜在会降低的芯片的表现。

5.单数颗或复数颗si中介层嵌入于fcbga基板内,需要高及中密度信号连接的布线设计在si中介层上,低密度信号连接的布线设计在fcbga基板上,虽然si中介层尺寸缩小降低了成本,不过fcbga基板无法设计中密度信号连接的布线(线宽线距介于8um到1.5um之间),abf材料内有二氧化硅填料(silica filler),盲孔(blind via hole)无法用蚀刻(etching)的方式开孔,而用雷射钻开盲孔(blind via hole),尺寸有限制,太小的孔无法钻,所以基板与芯片的接点的大小与间距无法缩小,si中介层及芯片尺寸无法进一步缩小,成本无法降低。

6.目前芯片与si中介层连接的接点间距55um,芯片与fcbga基板连接的接点间距130um。

7.三星samsung的h-cube:基本上与台积电tsmc的cowos类似,芯片安装在大片的si中介层上,si中介层再安装在细间距(fine pitch)的基板上,再安装在高密度互连(hdi,high density interconnect)的基板上。因为使用大片的si中介层及两个基板,面对的问题跟cowos一样,si中介层难做到足够的大、成本很高。

8.因此,现有的作法不是si中介层尺寸大(因为所有高、中、低密度的布线都在上面),造成成本太贵。就是si中介层尺寸缩小,高、中密度的布线在上面,fcbga基板只能设计

低密度(线宽线距大于8um)的布线,si中介层尺寸无法进一步缩小,甚至放更多的芯片的时候,si中介层尺寸还要加大,成本无法进一步降低。

技术实现要素:

9.本发明旨在至少解决现有技术中存在的技术问题之一。为此,本发明提供了一种带有si与有机中介层的先进封装结构及其制造方法,本发明兼具低成本及高的输入/输出密度,对整合更多的hbm及处理器芯片(或逻辑芯片)以提高运算的效能有很大的帮助。

10.本发明采用的技术方案为:

11.一种带有si与有机中介层的先进封装结构,其包括低密度布线的基板、高密度rdl布线的si中介层以及中密度rdl布线的有机介电层,所述si中介层内嵌于所述基板表面,所述有机介电层采用扇出面板级封装于所述si中介层及所述基板表面且与所述基板及所述si中介层电性连接;所述低密度布线的线宽线距大于所述中密度rdl布线的线宽线距,所述中密度rdl布线的线宽线距大于所述高密度rdl布线的线宽线距。

12.可选地,所述基板为fcbga基板,包括芯层以及压合堆栈于所述芯层两侧表面的若干层增层线路层,各层所述增层线路层及所述芯层间通过镭射开孔及孔内镀金属进行电性连接。

13.可选地,所述低密度布线的线宽线距大于8μm,所述中密度rdl布线的线宽线距介于8μm~1.5μm,所述高密度rdl布线的线宽线距小于1.5μm。

14.可选地,所述有机介电层包括交替堆栈的多层聚酰亚胺及多层中密度rdl布线,各层所述中密度rdl布线间通过蚀刻开孔其间的聚酰亚胺及孔内镀金属进行电性连接。

15.可选地,所述si中介层和所述有机介电层设于所述基板上表面,所述基板下表面设有锡球垫,所述有机介电层的上表面接点设有锡铜凸块。

16.可选地,所述中密度rdl布线的线宽线距随距离待安装内存芯片的位置的距离减小而减小。

17.可选地,所述基板上表面对应所述si中介层的位置形成空腔,所述si中介层与所述空腔间的间隙填入树脂。

18.可选地,所述si中介层的表面接点设有金属凸体,所述si中介层在内嵌于所述基板时,所述金属凸体与所述基板的表面接点共面。

19.一种用于制造如上所述的带有si与有机中介层的先进封装结构的制造方法,所述制造方法包括:

20.制作高密度rdl布线的si中介层;

21.制作低密度布线的基板,对应所述si中介层的位置于所述基板上表面开设空腔;

22.将所述si中介层内嵌于所述空腔内;

23.将内嵌有所述si中介层的所述基板下表面黏在载具上,上表面采用扇出面板级封装制作若干层中密度rdl布线的有机介电层,使所述有机介电层的rdl布线与所述si中介层及所述基板电性连接;

24.于所述si中介层的上表面接点制作锡铜凸块;

25.移除所述载具,切成单颗。

26.可选地,所述基板为fcbga基板,制作所述fcbga基板的步骤包括:

27.制作基板芯层,通过在所述芯层上开通孔、镀金属以导通所述芯层两侧表面的电路;

28.于所述芯层的两侧表面分别压合堆栈若干层增层线路层,各层所述增层线路层及所述芯层间通过镭射开孔及孔内镀金属进行电性连接。

29.可选地,所述si中介层的上表面接点设有金属凸体,在将所述si中介层内嵌于所述空腔内之后,于所述si中介层与所述空腔之间填入树脂,于所述si中介层及所述基板上表面继续压合增层线路层,所述增层线路层间镭射开孔内镀金属部分的高度与所述金属凸体的高度一致。

30.可选地,在采用扇出面板级封装于所述基板上表面制作所述有机介电层之前,还包括步骤:

31.研磨所述基板与所述si中介层上表面的增层线路层,研磨至所述金属凸体与所述增层线路层间镭射开孔内镀金属部分露出,并达到设计的厚度及平坦度。

32.可选地,制作所述有机介电层的步骤包括:于所述基板与所述si中介层上表面交替堆栈多层聚酰亚胺及多层中密度rdl布线,各层所述中密度rdl布线间通过蚀刻开孔其间的聚酰亚胺及孔内镀金属进行电性连接。

33.可选地,最后一层有机介电层制作完成后,用曝光显影蚀刻对聚酰亚胺开盲孔,制作与所述中密度rdl布线电性连接的锡铜凸块。

34.可选地,所述制造方法还包括步骤:

35.于切成单颗的基板上表面的si中介层上倒装处理器、逻辑及若干颗高带宽内存芯片,将所述芯片上若干个锡铜凸块与所述si中介层上表面的锡铜凸块焊接进行电性导通;

36.于所述芯片与所述si中介层的间隙做底部填充,贴上散热片,所述散热片与所述芯片背面有热界面材料,协助导热;

37.于所述基板下表面制作锡球垫。

38.由于采用上述技术方案,使得本发明具备以下有益效果:

39.本发明带有si与有机中介层的先进封装结构,si中介层提供高密度rdl布线,扇出面板级封装制程的有机介电层提供中密度rdl布线,而fcbga的基板提供低密度的布线,本发明先进封装结构同时使用这三种不同布线密度的介质,可以提供处理器(processor)、逻辑(logic)与高带宽内存(hbm,high bandwidth memory)多芯片整合在先进封装结构内,hbm从1个到6个都可以被放入封装体内,hbm数量越多,处理器processor的运算效率越好。

附图说明

40.为了更清楚地说明本发明实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

41.图1~5为本发明实施例提供的fcbga基板制程工艺的各步骤所呈现的结构示意图。

42.图6为本发明实施例提供的fcbga基板内嵌si中介层制程工艺所呈现的结构示意图。

43.图7~11为本发明实施例提供的fcbga基板上制作有机介电层制程工艺的各步骤所呈现的结构示意图。

44.附图标号对应关系如下:

45.1-fcbga基板;11-芯层;111-通孔;112-铜箔;12-增层线路层;121-abf增层膜片;122-铜导线;123-盲孔;124-电镀铜;13-空腔;2-si中介层;21-铜凸块或铜柱;22-daf黏膜;23-树脂;3-有机介电层;31-聚酰亚胺(pi);32-中密度rdl布线;33-光阻或光阻膜;4-锡铜凸块;5-锡球垫;6-玻璃载具;7-黏胶;8-处理器(processor);9-高带宽内层芯片(hbm);10-底部填充。

具体实施方式

46.下面结合附图对本发明的具体实施方式作进一步说明。在此需要说明的是,对于这些实施方式的说明用于帮助理解本发明,但并不构成对本发明的限定。此外,下面所描述的本发明各个实施方式中所涉及的技术特征只要彼此之间未构成冲突就可以相互组合。

47.首先,针对文中出现的技术术语解释如下:

48.rdl:redistribution layer,再分配层,包含铜连接线或走线,用于实现封装各个部分之间的电气连接,它是金属或高分子介电材料层,裸片可以堆叠在封装中,从而缩小芯片组的i/o间距;rdl已成为2.5d和3d封装解决方案中不可或缺的一部分,使其上芯片可以通过中介层相互进行通信;

49.daf:die attach film,晶片粘结薄膜,目的是在雷射切割时,晶片可一起切割与分离,进行剥离,使切割完后的晶片都还可粘着在薄膜上,不会因切割而造成散乱排列;

50.fcbga(flip chip ball grid array):倒装芯片球栅格阵列的封装格式,也是图形加速芯片最主要的封装格式;

51.增层:是在晶圆表面形成薄膜的加工工艺;

52.abf:abf材料是由intel主导研发的材料,用于导入flip chip等高阶载板的生产,相比于bt基材,abf材质可做线路较细、适合高脚数高传输的ic,多用于cpu、gpu和晶片组等大型高端芯片;abf作为增层材料,铜箔基板上面直接附着abf就可以作线路,也不需要热压合过程;

53.hbm:high bandwidth memory,高带宽内存芯片;

54.pi:polyimide,聚酰亚胺,指主链上含有酰亚胺环(-co-n-co-)的一类聚合物,是综合性能最佳的有机高分子材料之一。其耐高温达400℃以上,长期使用温度范围-200~300℃,部分无明显熔点,高绝缘性能,103赫兹下介电常数4.0,介电损耗仅0.004~0.007,属f至h级绝缘。

55.目前用于高效率运算结合processor及hbm芯片的封装有三大类,tsmc的cowos、intel的emib,及一些公司提出的将cpu及hbm芯片整合在fo封装体内,再将fo放封装在fcbga内的方案。其中cowos可以提供最佳的高输入/输出密度的解决方案,但是成本很高。另外两个解决方案虽然成本较低,不过可以提供输入/输出的密度比较低。本发明兼具低成本及高的输入/输出密度,对整合更多的hbm以提高运算的效能有很大的帮助。

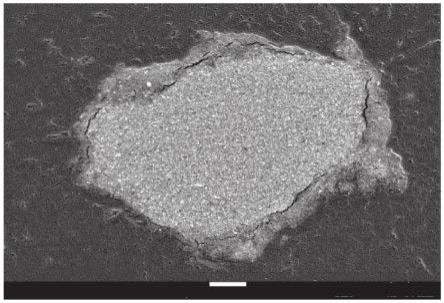

56.具体参阅1~11所示,其中,图1~5为本发明实施例提供的fcbga基板制程工艺的各步骤所呈现的结构示意图;图6为本发明实施例提供的fcbga基板内嵌si中介层制程工艺

所呈现的结构示意图;图7~11为本发明实施例提供的fcbga基板上制作有机介电层制程工艺的各步骤所呈现的结构示意图。

57.本发明实施例提供的带有si与有机中介层的先进封装结构,主要利用不同材质的中介层,表现出不同线路的宽度与间距,以支持高输入/输出(i/o:input/output)密度芯片间信号的互相连接。

58.该带有si与有机中介层的先进封装结构主要包括低密度布线的基板1、高密度rdl布线的si中介层2以及中密度rdl布线的有机介电层3,其中,si中介层2内嵌于基板1表面,有机介电层3采用扇出面板级封装于si中介层2及基板1表面且与基板1及si中介层2电性连接;其中,低密度布线的线宽线距大于中密度rdl布线的线宽线距,中密度rdl布线的线宽线距大于高密度rdl布线的线宽线距。优选地,低密度布线的线宽线距大于8μm,中密度rdl布线的线宽线距介于8μm~1.5μm,高密度rdl布线的线宽线距小于1.5μm。

59.如图1~5所示,基板1优选fcbga基板,包括芯层11以及压合堆栈于芯层11两侧表面的若干层增层线路层12,各层增层线路层12及芯层11间通过镭射开孔及孔内镀金属进行电性连接。

60.如图1所示,fcbga基板1的芯层11有若干层,主要的三层为玻璃纤维及树脂材质的中间层,中间层的上下两层为铜箔112。在芯层11基板上开通孔111,通孔111内镀铜(或其他等效金属),经蚀刻去除电路部分以外的铜箔112,形成电路且上下两层电路通过通孔111及孔内镀铜导通。

61.芯层11的上下两侧表面分别压合有多层增层线路层12,且通过通孔111及孔内镀铜电性导通芯层11两侧表面的增层线路层12。每层增层线路层12进一步包括abf增层膜片121以及形成于abf增层膜片121表面的铜导线122(或其他等效金属导线)构成的电路。具体做法是,采用积层(laminate)工序(或称增层工序)在芯层11的两面压合abf(ajinomoto build-up film,味之素增层膜)或同等的材料,将电路图案进行曝光,并通过显影蚀刻镀铜处理直接形成铜导线电路。多次重复该工序进行堆栈增层(积层),各层铜导线122间有盲孔123(blind via hole)作电性连接,盲孔123用雷射钻孔,尺寸有限制,太小的孔无法钻,盲孔123内填满电镀铜124(或其它等效金属)。积层(laminate)工序重复数次到需要的层数,如图2~4所示。

62.fcbga基板1上表面最后一层增层线路层12的abf增层膜片121开设空腔13,供放置si中介层2,如图5和图6所示,si中介层2与空腔13间的间隙填入树脂23。si中介层2上设有高密度rdl布线,且在si中介层2上表面接点位置设有铜凸块或铜柱21(或其他等效金属凸体),si中介层2在内嵌于fcbga基板1上表面的空腔13内时,该些铜凸块或铜柱21朝上且与fcbga基板1的表面接点共面,如图7所示,可以通过在fcbga基板1上嵌入si中介层2后,在fcbga基板1上表面继续压合增层线路层12,并使增层线路层12间镭射开孔内电镀铜124的高度与铜凸块或铜柱21的高度一致。

63.如图8~10所示,有机介电层3包括交替堆栈的多层聚酰亚胺31及多层中密度rdl布线32,各层中密度rdl布线32间通过蚀刻开孔其间的聚酰亚胺31及孔内电镀铜(或其他等效金属)进行电性导通,有机介电层3内的中密度rdl布线32和聚酰亚胺31采用扇出面板级封装制作于fcbga基板1及si中介层2之上,中密度rdl布线32电性导通fcbga基板1上的低密度布线以及si中介层2上的高中密度rdl布线。si中介层2和有机介电层3设于fcbga基板1上

表面,fcbga基板1下表面设有锡球垫5,如图11所示,有机介电层3的上表面接点设有锡铜凸块4。锡铜凸块4可用于焊接内存芯片9上的锡铜凸块,约靠近内存芯片8的位置,有机介电层3内的中密度rdl布线32的线宽线距越细微,甚至细到1.5μm~2.0μm。

64.缩小尺寸的si中介层嵌入在fcbga可以降低成本,封装制程也相对简单,封装成本也比较低。不过因为高、中密度的布线在si中介层上面,si中介层尺寸无法进一步缩小,甚至放更多的芯片的时候,si中介层尺寸还要加大。

65.本发明通过将中密度的布线从si中介层移出,放在聚酰亚胺有机介电层,这个聚酰亚胺有机介电层可以设计中密度的布线(rdl线宽线距的能力介于10~1.5微米),并且有较低的成本。

66.纵观整个电子及半导体供应链,晶圆厂的制程主要处理1微米(um)到3奈米(nm)的线宽线距,印刷电路板的制程处理几个毫米(mm)以上的线宽线距,封装厂的制程处理几个毫米(mm)到几个微米(um)的线宽线距,而封装厂用的基板,其制程处理8微米(um)到几百微米间的线宽线距,封装厂的凸块,扇入/扇出封装制程可处理几十微米到1微米的线宽线距,以此发想出解决目前先进封装遇到的瓶颈。

67.扇入晶圆级封装(fi-wlp,fan in wafer level package)及扇出晶圆级封装(fo-wlp,fan out wafer level package)的差异主要在于:扇入封装的锡球在芯片的范围内,扇出封装的锡球有到芯片的范围外。

68.封装厂(有些晶圆厂也有)的扇出晶圆级封装制程,是从半导体裸晶的端点(pad)上,拉出需要的电路至重分布层(redistribution layer),进而形成封装。因此不需封装基板,不用打线(wire)、凸块(bump),能够降低生产成本,也让芯片及封装更薄。为了形成重分布层,前段制程就须导入封装,对封装厂的制程能力大幅提升,从几毫米提升几微米。

69.晶圆级封装是以晶圆级制程为主,制程处理以一片或复数片晶圆为单位。

70.fowlp制程分为两类:

71.芯片优先fo:于晶圆级载具(carrier)上放置,从原始装置晶圆中挑拣出的合格晶元(kgd,known good die),以模压树脂包覆成重构晶圆(re-constitution wafer),再进一步处理成晶圆上的rdl、植球、移除载具、切单。

72.rdl优先fo:晶圆级载具建立rdl层并暂时接合,在顶端放置kgd然后压模树脂包覆(molding)、研磨、移除载具、植球、切单。

73.在这两种制程架构下,也能依据客户不同的需求,衍伸出多种变化,例如晶粒面向上接合、晶粒面向下接合、rdl细线优先、rdl粗线优先类型。fowlp的rdl线宽线距的能力最小可以到1.5微米。

74.fowlp较适用于芯片尺寸小于5mm2,若芯片很大,晶圆级是圆弧状,会浪费很多晶圆空间。解决的方法是用扇出型封装foplp(fan out panel level package),以面板级的制程方式,节省空间,让单位的产出增加,大幅降低成本。

75.面板级的制程能力可以跟晶圆级一样,如果将晶圆级设备的工作区域放大,当然这必须与材料商及设备商一起开发合适的材料及制程设备,以达到一样制程能力,rdl线宽线距的能力最小可以到1.5微米。

76.利用新开发的材料与设备,扇出面板级封装的rdl制程线宽线距的能力可以小到1.5微米,刚好符合中密度布线(rdl线宽线距的能力介于10~1.5微米)的需求,所以可以用

扇出面板级封装的制程来制作中布线密度的中介层。

77.si中介层提供高的rdl布线密度,扇出面板级封装制程的有机介电层提供中密度rdl布线,而fcbga基板提供低密度的布线,先进封装若同时使用这三种不同布线密度的介质,可以提供processor、logic与hbm多芯片整合在先进封装内,hbm从1个到6个都可以被放入封装体内,hbm数量越多,处理器processor的运算效率越好。

78.本发明提供的方案是将高密度rdl布线的si中介层内嵌于低密度布线的fcbga基板,这工作可以在基板厂完成,基板厂的制程是面板级,所以先不切成单颗,接下来送到有扇出面板级封装制程(rdl线宽线距的能力小到1.5微米)的地方,在基板表面做出复数层rdl(中密度布线)的有机介电层,最上面有铜锡凸块,作为之后贴装芯片的电性连接。最后切成单颗,出货给封装厂做后续fcbga的制程。

79.配合图1~11所示,为本发明实施例提供的用于制造如上实施例的带有si与有机中介层的先进封装结构的制造方法,该制造方法包括:

80.第1步:制作高密度rdl布线的si中介层,该si中介层2上设有高密度rdl布线,且在该si中介层2上表面接点位置设有铜凸块或铜柱21(或其他等效金属凸体),铜凸块或铜柱21与高密度rdl布线电性连接。

81.第2步:制作低密度布线的fcbga基板1,对应si中介层2的位置于fcbga基板1的上表面开设空腔13。

82.具体来说,制作fcbga基板1的步骤进一步包括:

83.制作基板芯层11,通过在芯层11上开通孔111、镀铜(或其他等效金属)以导通芯层11两侧表面的铜箔122蚀刻而成的电路,如图1所示;

84.于芯层11的两侧表面分别压合堆栈若干层增层线路层12,各层增层线路层12及芯层11间通过镭射盲孔123及盲孔123内填充电镀铜124(或其他等等效金属)进行电性导通。

85.更具体地,增层线路层12采用积层(laminate)工序(或称增层工序)。在芯层的两面压合abf(ajinomoto build-up film,味之素增层膜)增层膜片121或同等的材料,将电路图案进行曝光,并通过镀铜处理直接形成电路(即铜导线122构成的电路)。多次重复该工序进行堆栈增层(积层),各层铜导线122间有盲孔123(blind via hole)作电性连接,盲孔123用雷射钻孔,尺寸有限制,太小的孔无法钻。积层(laminate)工序重复数次到需要的层数,如图2~4所示。

86.第3步:在要放置si中介层2(有复数层rdl线宽线距小于1.5微米)的位置在fcbga基板1的上表面挖空腔,si中介层2上表面接点有铜凸块或铜柱21,将si中介层2的铜凸块或铜柱21朝上,si中介层2底部固定在空腔13内,si中介层2与空腔13间的间隙填入树脂23,之后压合abf增层膜片121将si中介层2(上表面有铜凸块或铜柱21)及基板1上的铜导线122覆盖,用雷射在基板1上开盲孔123(blind via hole),盲孔123内填充电镀铜124(或其他等效金属),高度与si中介层2上表面的铜凸块或铜柱21的高度一致,如图5~7所示。

87.第4步:增层工序之后进行外层工序,清洁、检查外观及电气特性,就完成fcbga基板1制程的部分。

88.第5步:将基板1的面板送到扇出面板级封装的生产线,基板厂作好的基板面板的表面形貌是不平坦的,对之后细微线路的成形有不良的影响(断线、短路等)。先将面板清洁后,下表面用黏胶7黏在玻璃载具6上,上表面为abf增层膜片121(上有复数个盲孔123,盲孔

123内有填电镀铜124,对abf增层膜片121的表面进行研磨,研磨的方式有机械研磨或化学机械抛光(cmp,chemical mechanical polish),研磨至si中介层2上表面的铜凸块或铜柱21以及盲孔123内所填电镀铜124露出,并达到设计的厚度及平坦度。

89.第6步:研磨后,清洁基板1面板,在平坦的表面做出复数层的中密度rdl布线32及复数层的介电层(聚酰亚胺polyimide或同等的材料),中密度rdl布线32层与层之间的聚酰亚胺31开盲孔(blind via hole),盲孔用蚀刻的方式开孔,电镀埋孔作各层铜导线间电性连接。越靠近芯片的中密度rdl布线32,其线宽线距越细微,甚至细到1.5~2.0微米,所以通过中密度rdl布线32层及介电层的厚度控制,介电层材料的选用,及制程的工法优化,能够使介电层表面形貌尽量的平坦,如此图案化rdl的铜导线才会达成细线化的要求。如图8~10所示。

90.第7步:最后一层中密度rdl布线32及聚酰亚胺31做好后,用曝光显影蚀刻的方式对聚酰亚胺31开孔,因为用蚀刻的方式开孔,孔的尺寸与间距可以缩小,在安装芯片(裸片)的接点部分形成锡铜凸块4。将面板切成复数个单颗fcbga基板,检查外观及电气特性,出货给封装厂继续后续的制程。聚酰亚胺31用蚀刻的方式开孔,比abf用雷射开孔有更小的尺寸与间距,所以芯片与si中介层连接的接点间距可以缩小到35~40um(目前55um)。芯片与si中介层的尺寸可以跟着缩小。降低成本。如图11所示。

91.第8步:封装厂将处理器8(processor)、逻辑(logic)及1到6颗高带宽内存(hbm,high bandwidth memory)芯片9等倒装在fcbga基板1上表面,芯片9上复数个锡铜凸块与fcbga基板1上表面复数个锡铜凸块4的接点焊接做电性导通,芯片9与基板1的间隙做底部填充10(underfill),贴上散热片,散热片与芯片背面有热界面材料(tim,thermal interface material),协助导热。最后在fcbga基板1下表面的球垫,植上复数个锡球,构成锡球垫5,散热片上盖印,检查外观及电气特性,完成fcbga基板的封装制程,如图11所示。

92.在本发明的描述中,需要说明的是,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本发明中的具体含义。

93.在本发明的描述中,需要理解的是,术语“上”、“下”、“竖直”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。

94.术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。

95.以上结合附图对本发明的实施方式作了详细说明,但本发明不限于所描述的实施方式。对于本领域的技术人员而言,在不脱离本发明原理和精神的情况下,对这些实施方式进行多种变化、修改、替换和变型,仍落入本发明的保护范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。