1.本发明涉及集成电路技术领域,特别涉及一种低功耗带隙基准电路。

背景技术:

2.模拟集成电路广泛的采用电压基准和电流基准电路,作为全芯片的参考电压或电流。这些基准电路要求对电源电压、工艺参数和温度漂移变化很小。目前业界普遍采用带隙基准源电路,不仅可以实现基准电压对电源电压、工艺参数的不敏感,同时可以实现基准输出电压的近似零温度漂移特性,性能相对于传统基准源有显著提升。

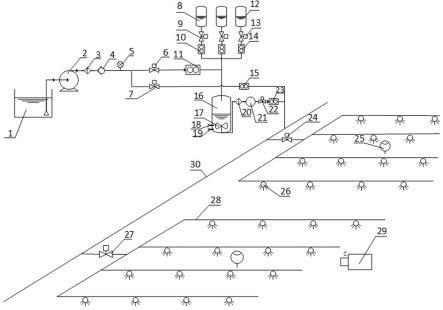

3.传统的带隙基准电路如图1所示,其中q11是发射极面积为a的npn三极管,其基极-集电极相连等效为二极管器件,q12是发射极面积为n

×

a的npn三极管,基极-集电极也短接。npn三极管q12的集电极串联电阻r13后与npn三极管q11的集电极分别接入运算放大器a11的负端与正端。运算放大器a11的输出为带隙基准电压输出端,同时通过电阻r11、r12连接到运算放大器a11的正、负端,构成反馈。

4.该带隙基准电路的原理是利用两个正、负温度系数的电压相加,得到一个零温度系数的基准。首先,利用运放的“虚短”特性,节点x、节点y电压近似相等,根据基尔霍夫电压定律,有:

[0005]vbe,q11

=v

be,q12

i

×r13

ꢀꢀ

(1)

[0006]

其中v

be,q11

为q11的基极(集电极)-发射极电压,v

be,q12

为q12的基极(集电极)-发射极电压,i为流过电阻r13的电流。

[0007]

pn结电压满足如下关系:

[0008][0009]vt

为热电压,是一个物理常数。io为pn结正向导通电流,is为饱和电流,是pn结的器件参数。将等式(2)的关系代入等式(1),可得:

[0010][0011]vt

为热电压物理常量,忽略电阻r13的温度系数。所以流过r13的电流为正温度系数电流。

[0012]

所以带隙基准输出为:

[0013][0014]

由于三极管基极-发射极电压为负温度系数,所以通过合理配置等式(4)中的第一项和第二项的关系,就可以得到零温度系数的带隙基准电压。

[0015]

电路的功耗i

gnd

为:

[0016][0017]

由此可见,传统带隙基准电路功耗包含两个部分:基准电压产生模块的功耗和运算放大器的功耗。为了保证节点x、y两点电压精确相等,电路内置了运算放大器a11,增加了电路面积,电路结构不紧凑;由于需要额外的运放来保证电路性能,电路需要消耗额外的功耗,电路功耗无法有效降低,不适合低功耗应用。

技术实现要素:

[0018]

本发明的目的在于提供一种低功耗带隙基准电路,以解决背景技术中的问题。

[0019]

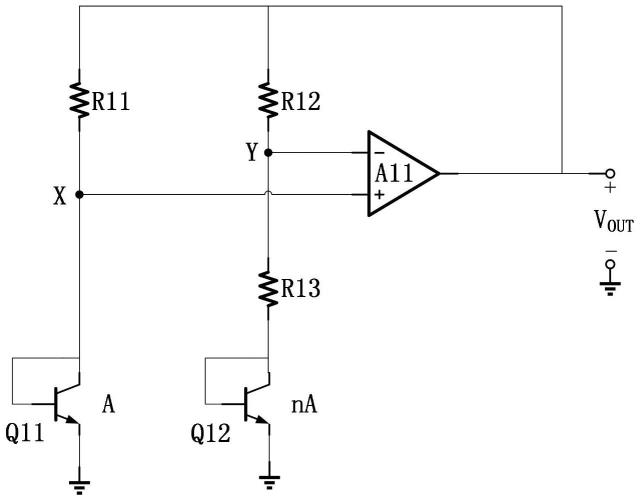

为解决上述技术问题,本发明提供了一种低功耗带隙基准电路,包括pmos管mp1~mp2、电阻r1~r3和三极管q1~q2;

[0020]

pmos管mp1的漏端接电阻r3的第一端,栅端接pmos管mp2的栅端;

[0021]

pmos管mp2的漏端接三极管q2的集电极,栅端接自身漏端;

[0022]

三极管q1的集电极接电阻r3的第二端,基极接电阻r3的第一端,发射极接电阻r1的第一端;

[0023]

三极管q2的集电极接pmos管mp2的漏端,基极连接三极管q1的集电极,发射极连接电阻r2的第一端。

[0024]

可选的,所述电阻r2的第二端连接所述电阻r1的第一端,所述电阻r1的第二段接地。

[0025]

可选的,所述pmos管mp1的源端和所述pmos管mp2的源端共同连接电源vdd。

[0026]

可选的,所述pmos管mp1和所述pmos管mp2分别作为所述三极管q1和所述三极管q2的有源负载,器件尺寸相同。

[0027]

在本发明提供的低功耗带隙基准电路中,包括pmos管mp1~mp2、电阻r1~r3和三极管q1~q2;pmos管mp1的漏端接电阻r3的第一端,栅端接pmos管mp2的栅端;pmos管mp2的漏端接三极管q2的集电极,栅端接自身漏端;三极管q1的集电极接电阻r3的第二端,基极接电阻r3的第一端,发射极接电阻r1的第一端;三极管q2的集电极接pmos管mp2的漏端,基极连接三极管q1的集电极,发射极连接电阻r2的第一端。

[0028]

本发明相比于目前现有技术具有如下优点:

[0029]

(1)电路复用三极管q1、q2与pmos管mp2、mp1、电阻r3构成反馈环路以确定电路工作点,省去了额外的运放电路,大大减小了面积开销;

[0030]

(2)由于省去了额外的运放模块,且电路到地只有两条电流通路,可以大大降低带隙基准模块的功耗。

附图说明

[0031]

图1是传统带隙基准电路结构示意图;

[0032]

图2是本发明提供的低功耗带隙基准电路结构示意图。

具体实施方式

[0033]

以下结合附图和具体实施例对本发明提出的一种低功耗带隙基准电路作进一步

详细说明。根据下面说明和权利要求书,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

[0034]

实施例一

[0035]

本发明提供了一种低功耗带隙基准电路,其结构如图2所示,包括pmos管mp1~mp2、电阻r1~r3和三极管q1~q2;pmos管mp1的漏端接电阻r3的第一端,栅端接pmos管mp2的栅端;pmos管mp2的漏端接三极管q2的集电极,栅端接自身漏端;三极管q1的集电极接电阻r3的第二端,基极接电阻r3的第一端,发射极接电阻r1的第一端;三极管q2的集电极接pmos管mp2的漏端,基极连接三极管q1的集电极,发射极连接电阻r2的第一端。所述电阻r2的第二端连接所述电阻r1的第一端,所述电阻r1的第二段接地。所述pmos管mp1的源端和所述pmos管mp2的源端共同连接电源vdd。

[0036]

在本发明中,三极管q1的发射极连接r1到地,三极管q2的发射极依次串联r2、r1到地。三极管q1的集电极连接电阻r3的一端,并通过电阻r3的另一端与其自身的基极相连。pmos管mp1、mp2作为三极管q1、q2的有源负载,器件尺寸相同。

[0037]

电路中正温度系数电流i满足如下等式(假设三极管q1的基极电流远小于集电极电流):

[0038][0039]

i为电路中正温度系数电流,v

t

为热电压,δv

be

为三极管q1的基极-发射极电压与三极管q2的基极-发射极电压之差,v

be1

为三极管q1的基极-发射极电压,v

be2

为三极管q2的基极-发射极电压,n为三极管q2的发射极面积与三极管q1的发射极面积的比值,等式两边变换后得到:

[0040][0041]

最终带隙基准电压输出v

out

为:

[0042][0043]

同时整个电路的功耗为:

[0044][0045]

通过对比等式(5)与等式(9),发现本发明的带隙基准省去了额外的运放模块,功耗较传统结构明显减小。

[0046]

上述描述仅是对本发明较佳实施例的描述,并非对本发明范围的任何限定,本发明领域的普通技术人员根据上述揭示内容做的任何变更、修饰,均属于权利要求书的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。