具有hkmg的mos晶体管及其制造方法

技术领域

1.本发明涉及半导体集成电路领域,特别涉及一种具有高介电常数金属栅(hkmg)的mos晶体管。本发明还涉及一种具有高介电常数金属栅的mos晶体管的制造方法。

背景技术:

2.在现有半导体产业中,多晶硅广泛地应用于半导体元件如mos晶体管中,一般被作为标准的栅极填充材料。然而,随着mos晶体管尺寸减小,传统多晶硅栅极因硼穿透(boron penetration)效应导致元件效能降低,及难以避免的空乏效应(depletion effect)等问题,使得等效栅极介电层厚度增加、栅极电容值下降,进而导致元件性能衰退等。因此,半导体业界便尝试以新的栅极填充材料,例如利用功函数(work function,wf)金属层来取代传统的多晶硅栅极,用以作为匹配高介电常数(high-k,hk)的栅介质层的控制电极即金属栅(mg)。hkmg具有高介电常数(hk)的栅介质层以及金属栅(mg),故本领域中通常缩写为hkmg。

3.但随着半导体元件尺寸的进一步持续缩小,又在填入功函数金属层之后,还须再填入阻挡层等其他材料层,同时这种材料层必须有足够的厚度才能阻挡其上的铝向下扩散,因而占据了部分凹槽的体积及缩减了凹槽的开口尺寸,进而发生后续铝填洞困难的问题。再者,随着元件尺寸的减小,所填入铝所占的体积及所露出的表面积也日趋缩小,进而增加了接触插塞(ct)与铝的接触电阻。此外,随着半导体元件的精密化及精致化,其电性需求更为严苛,如何在不增加栅极凹槽中阻挡层厚度情况下,阻止铝向下扩散逐渐成为现今急需解决的问题。

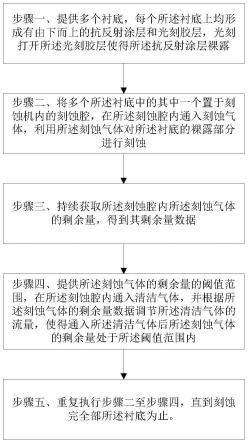

4.如图1所示,是现有具有hkmg的nmos的结构图,现有具有hkmg的nmos的hkmg的栅极结构包括栅介质层和金属栅。

5.通常,hkmg是采用后栅极工艺形成,栅极结构形成于栅极凹槽中,栅极凹槽由形成于半导体衬底101表面上的层间膜102和侧墙103围绕形成。栅极凹槽是通过去除伪栅极结构后形成。侧墙103会自对准形成在伪栅极结构的侧面,在层间膜102的顶部表面和伪栅极结构的顶部表面相平后,去除伪栅极结构即可形成栅极凹槽。

6.所述栅介质层包括高介电常数层105。所述高介电常数层105的材料通常采用二氧化铪(hfo2),也能采用氮化硅(si3n4),三氧化二铝(al2o3),五氧化二钽(ta2o5),氧化钇(y2o3),硅酸铪氧化合物(hfsio4),氧化镧(la2o3),二氧化锆(zro2),钛酸锶(srtio3),硅酸锆氧化合物(zrsio4)等。

7.在所述高介电常数层105和半导体衬底101之间通常设置由第一界面层104(il)。现有工艺中,所述高介电常数层105的材料通常采用hfo2,第一界面层104通常采用sio2。

8.所述栅介质层还包括第一覆盖层106。通常,所述第一覆盖层106采用氮化钛层(tin)组成。

9.金属栅包括了第二覆盖层107、n型功函数金属层108和金属导电材料层109。

10.其中,第一覆盖层106和第二覆盖层107叠加形成底部阻障层(bottom barrier metal,bbm)。

11.金属导电材料层109通常为al层。为了防止金属导电材料层109的al往下扩散,通常需要在n型功函数金属层108和金属导电材料层109之间设置顶部阻障层(top barrier metal,tbm),tbm的材料为tin或者为tin和ti的叠加层。tbm作为al向下扩散的阻挡层。

12.n型功函数金属层108的材料通常为tial。

13.所述金属栅的材料为al。

14.为了防止al向下扩散,tbm即阻挡层的厚度需要采用较大值。而随着器件尺寸的不断缩小,栅极凹槽的宽度也会不断缩小,此时,阻挡层的厚度取较大值时,在阻挡层形成之后,栅极凹槽的剩余开口宽度会变小。而金属导电材料层109是填充在栅极凹槽的剩余开口中,栅极凹槽的剩余开口宽度会变小显然会增加金属导电材料层109填充栅极凹槽的难度。同时,填充后金属导电材料层109的体积变小以及顶部露出的表面面积会变小,这样在金属导电材料层109的顶部形成接触孔之后,二者之间的接触电阻会变大,这样影响器件的性能。

技术实现要素:

15.本发明所要解决的技术问题是提供一种具有hkmg的mos晶体管,在满足阻挡金属导电材料层的金属向下扩散的条件下,能减少阻挡金属导电材料层的金属向下扩散的阻挡层的厚度,从而有利于金属导电材料层的填充,有利于mos晶体管的尺寸进一步缩小。

16.为解决上述技术问题,本发明提供的具有hkmg的mos晶体管包括nmos,所述nmos的栅极结构为第一栅极结构,所述第一栅极结构形成在位于nmos形成区域的第一栅极凹槽中。

17.所述第一栅极结构包括栅介质层、n型功函数金属层和金属导电材料层;所述栅介质层中包括高介电常数材料层。

18.所述n型功函数金属层由第一n型功函数金属子层和第二n型功函数金属子层叠加而成,所述第一n型功函数金属子层和所述第二n型功函数金属子层具有不同的晶格结构并在所述第一n型功函数金属子层和所述第二n型功函数金属子层接触面处形成晶格排列变化的第一界面层,利用所述第一界面层作为阻挡所述金属导电材料层的金属向下扩散的阻挡层。

19.进一步的改进是,所述第一n型功函数金属子层的材料包括tial。

20.所述第二n型功函数金属子层的材料包括tialc。

21.进一步的改进是,所述第一n型功函数金属子层采用pvd工艺沉积形成;所述第二n型功函数金属子层采用ald工艺沉积形成。

22.进一步的改进是,所述金属导电材料层的材料包括al。

23.进一步的改进是,所述第二n型功函数金属子层中al含量小于50%,以降低向下扩散的al扩散源。

24.进一步的改进是,mos晶体管包括pmos,所述pmos和所述nmos集成在同一半导体衬底上。

25.所述pmos的栅极结构为第二栅极结构,所述第二栅极结构形成在位于pmos形成区域的第二栅极凹槽中。

26.所述第二栅极结构包括所述栅介质层、p型功函数金属层和所述金属导电材料层。

27.进一步的改进是,在所述nmos形成区域中,未形成所述p型功函数金属层或者所述p型功函数金属层在形成之后被去除,所述第一栅极结构中不包括所述p型功函数金属层。

28.在所述pmos形成区域中,未形成所述n型功函数金属层或者所述n型功函数金属层在形成之后被去除,所述第二栅极结构中不包括所述n型功函数金属层;或者,在所述pmos形成区域中,形成有所述n型功函数金属层,所述第二栅极结构中包括所述n型功函数金属层,所述n型功函数金属层叠加在所述p型功函数金属层表面上。

29.进一步的改进是,所述第一栅极结构中,所述栅介质层中还包括位于所述高介电常数材料层和底部的半导体衬底表面之间的第二界面层以及位于所述高介电常数材料层顶部表面的第一覆盖层。

30.在所述第一覆盖层和所述n型功函数金属层之间还形成有第二覆盖层,所述第一覆盖层和所述第二覆盖层叠加形成底部阻障层。

31.在所述n型功函数金属层和所述金属导电材料层之间还形成有顶部阻障层,所述第一界面层和所述顶部阻障层一起实现阻挡所述金属导电材料层的金属向下扩散,通过所述第一界面层减少所述顶部阻障层所需厚度,以利于所述金属导电材料层在所述第一栅极凹槽中填充。

32.为解决上述技术问题,本发明提供的具有hkmg的mos晶体管的制造方法中,mos晶体管包括nmos,所述nmos的栅极结构为第一栅极结构,所述第一栅极结构的形成步骤包括:

33.步骤一、在nmos形成区域中形成第一栅极凹槽。

34.步骤二、形成栅介质层;所述栅介质层中包括高介电常数材料层。

35.步骤三、采用两步生长工艺形成n型功函数金属层,包括:

36.步骤31、形成第一n型功函数金属子层。

37.步骤32、形成第二n型功函数金属子层;所述n型功函数金属层由第一n型功函数金属子层和第二n型功函数金属子层叠加而成,所述第一n型功函数金属子层和所述第二n型功函数金属子层具有不同的晶格结构并在所述第一n型功函数金属子层和所述第二n型功函数金属子层接触面处形成晶格排列变化的第一界面层。

38.步骤四、形成金属导电材料层,所述第一栅极结构由形成于所述第一栅极凹槽中的栅介质层、n型功函数金属层和金属导电材料层叠加形成,利用所述第一界面层作为阻挡所述金属导电材料层的金属向下扩散的阻挡层。

39.进一步的改进是,所述第一n型功函数金属子层的材料包括tial;

40.所述第二n型功函数金属子层的材料包括tialc。

41.进一步的改进是,步骤31中,所述第一n型功函数金属子层采用pvd工艺沉积形成;

42.步骤32中,所述第二n型功函数金属子层采用ald工艺沉积形成。

43.进一步的改进是,所述金属导电材料层的材料包括al。

44.进一步的改进是,所述第二n型功函数金属子层中al含量小于50%,以降低向下扩散的al扩散源。

45.进一步的改进是,mos晶体管包括pmos,所述pmos和所述nmos集成在同一半导体衬底上。

46.所述pmos的栅极结构为第二栅极结构;所述第二栅极结构和所述第一栅极结构集成在一起制作,所述第二栅极结构的形成步骤包括:

47.在步骤一中同时在pmos形成区域中形成第二栅极凹槽。

48.步骤二中,所述栅介质层同时形成在所述pmos形成区域。

49.在步骤三之前,还包括在所述pmos形成区域形成p型功函数金属层,之后再进行步骤三和步骤四;

50.步骤四中所述金属导电材料层同时形成在所述pmos形成区域;所述第二栅极结构由形成于所述第二栅极凹槽中的栅介质层、p型功函数金属层和金属导电材料层叠加形成。

51.进一步的改进是,形成所述p型功函数金属层时,所述p型功函数金属层仅形成在所述pmos形成区域中;或者所述p型功函数金属层同时形成在所述nmos形成区域中,之后采用刻蚀工艺去除所述nmos形成区域中的所述p型功函数金属层。

52.步骤三中,所述n型功函数金属层仅形成在所述nmos形成区域中;或者所述n型功函数金属层同时形成在所述pmos形成区域中,之后所述pmos形成区域中的所述n型功函数金属层被刻蚀去除或保留;所述pmos形成区域中的所述n型功函数金属层保留时,所述第二栅极结构中包括所述n型功函数金属层,所述n型功函数金属层叠加在所述p型功函数金属层表面上。

53.进一步的改进是,步骤二中,在形成所述高介电常数材料层之前,还包括在半导体衬底表面形成第二界面层的步骤;在形成所述高介电常数材料层之后,还包括形成第一覆盖层的步骤。

54.步骤三中,在形成所述n型功函数金属层之前,还包括形成第二覆盖层的步骤,所述第一覆盖层和所述第二覆盖层叠加形成底部阻障层。

55.在步骤三完成后,还包括在所述n型功函数金属层的表面形成顶部阻障层的步骤,所述第一界面层和所述顶部阻障层一起实现阻挡所述金属导电材料层的金属向下扩散,通过所述第一界面层减少所述顶部阻障层所需厚度,以利于所述金属导电材料层在所述第一栅极凹槽中填充。

56.本发明对nmos的n型功函数金属层进行了特别设置,将n型功函数金属层设置为由两层晶格结构不同的第一n型功函数金属子层和第二n型功函数金属子层叠加而成,利用第一n型功函数金属子层和第二n型功函数金属子层的晶格结构不同,能形成晶格排列变化的第一界面层,而晶格排列变化的第一界面层则作为阻挡金属导电材料层的金属向下扩散的阻挡层,所以,本发明的阻挡金属导电材料层的金属向下扩散的阻挡层能采用n型功函数金属层实现,这样能减少额外形成的阻挡金属导电材料层的金属向下扩散的阻挡层如顶部阻障层的厚度或者直接取消额外形成的阻挡金属导电材料层的金属向下扩散的阻挡层,这样有利于金属导电材料层在较小尺寸的栅极凹槽如第一栅极凹槽中填充,有利于mos晶体管的尺寸进一步缩小。

57.另外,在栅极凹槽的尺寸不变的条件下,额外形成的阻挡金属导电材料层的金属向下扩散的阻挡层的厚度减小时,金属导电材料层在栅极凹槽中所填充区域的体积会增加,在有利于金属导电材料层填充的同时,填充后的金属导电材料层的体积也会增加,在金属导电材料层和顶部的接触插塞的接触电阻会降低,所以能提高器件的性能。

58.本发明的n型功函数金属层分成第一n型功函数金属子层和第二n型功函数金属子层后,第二n型功函数金属子层采用tialc时,相对于第一n型功函数金属子层采用的tial,第二n型功函数金属子层的al含量会降低,这样会降低al向下扩散的al扩散源,能进一步降

低金属向下扩散所带来的技术问题。

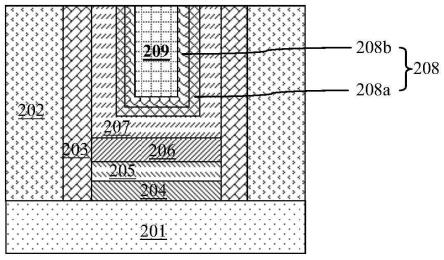

附图说明

59.下面结合附图和具体实施方式对本发明作进一步详细的说明:

60.图1是现有具有hkmg的nmos的结构图;

61.图2是本发明实施例具有hkmg的mos晶体管中的nmos的结构图;

62.图3是本发明实施例具有hkmg的mos晶体管的制造方法的流程图。

具体实施方式

63.如图2所示,是本发明实施例具有hkmg的mos晶体管中的nmos的结构图;本发明实施例具有hkmg的mos晶体管包括nmos,所述nmos的栅极结构为第一栅极结构,所述第一栅极结构形成在位于nmos形成区域的第一栅极凹槽中。图2中仅显示了nmos形成区域的结构。

64.所述第一栅极结构包括栅介质层、n型功函数金属层208和金属导电材料层209;所述栅介质层中包括高介电常数材料层205。

65.所述n型功函数金属层208由第一n型功函数金属子层208a和第二n型功函数金属子层208b叠加而成,所述第一n型功函数金属子层208a和所述第二n型功函数金属子层208b具有不同的晶格结构并在所述第一n型功函数金属子层208a和所述第二n型功函数金属子层208b接触面处形成晶格排列变化的第一界面层,利用所述第一界面层作为阻挡所述金属导电材料层209的金属向下扩散的阻挡层。

66.本发明实施例中,所述金属导电材料层209的材料包括al。

67.所述第一n型功函数金属子层208a的材料包括tial。所述第一n型功函数金属子层208a采用pvd工艺沉积形成。

68.所述第二n型功函数金属子层208b的材料包括tialc。

69.所述第二n型功函数金属子层208b采用ald工艺沉积形成。

70.所述第二n型功函数金属子层208b中al含量小于50%,以降低向下扩散的al扩散源。

71.mos晶体管还包括pmos,所述pmos和所述nmos集成在同一半导体衬底201上。pmos形成在pmos形成区域中。在所述半导体衬底201上形成有浅沟槽隔离(sti),以实现所述pmos和所述nmos之间的隔离。

72.所述pmos的栅极结构为第二栅极结构,所述第二栅极结构形成在位于pmos形成区域的第二栅极凹槽中。

73.所述第一栅极凹槽和所述第二栅极凹槽都是通过去除伪栅极结构之后形成。侧墙203自对准形成在伪栅极结构的侧面。第零层层间膜202的顶部表面和伪栅极结构的顶部表面相平之后,去除伪栅极结构即可形成栅极凹槽,其中位于nmos形成区域的栅极凹槽为所述第一栅极凹槽,位于pmos形成区域的栅极凹槽为所述第二栅极凹槽。

74.所述第二栅极结构包括所述栅介质层、p型功函数金属层和所述金属导电材料层209。

75.如图2所示,在所述nmos形成区域中,未形成所述p型功函数金属层或者所述p型功函数金属层在形成之后被去除,所述第一栅极结构中不包括所述p型功函数金属层。

76.在所述pmos形成区域中,未形成所述n型功函数金属层208或者所述n型功函数金属层208在形成之后被去除,所述第二栅极结构中不包括所述n型功函数金属层208;或者,在所述pmos形成区域中,形成有所述n型功函数金属层208,所述第二栅极结构中包括所述n型功函数金属层208,所述n型功函数金属层208叠加在所述p型功函数金属层表面上。

77.所述第一栅极结构中,所述栅介质层中还包括位于所述高介电常数材料层205和底部的半导体衬底201表面之间的第二界面层204以及位于所述高介电常数材料层205顶部表面的第一覆盖层206。

78.在所述第一覆盖层206和所述n型功函数金属层208之间还形成有第二覆盖层207,所述第一覆盖层206和所述第二覆盖层207叠加形成底部阻障层。在所述n型功函数金属层208和所述金属导电材料层209之间还形成有顶部阻障层,所述第一界面层和所述顶部阻障层一起实现阻挡所述金属导电材料层209的金属向下扩散,通过所述第一界面层减少所述顶部阻障层所需厚度,以利于所述金属导电材料层209在所述第一栅极凹槽中填充。

79.所述高介电常数层205的材料通常采用二氧化铪(hfo2),也能为:氮化硅(si3n4),三氧化二铝(al2o3),五氧化二钽(ta2o5),氧化钇(y2o3),硅酸铪氧化合物(hfsio4),氧化镧(la2o3),二氧化锆(zro2),钛酸锶(srtio3),硅酸锆氧化合物(zrsio4)等。

80.第二界面层204通常采用sio2。

81.所述第一覆盖层206采用氮化钛层,所述第二覆盖层207采用氮化钽层。

82.所述顶部阻障层的材料为tin或者为tin和ti的叠加层。

83.本发明实施例对nmos的n型功函数金属层208进行了特别设置,将n型功函数金属层208设置为由两层晶格结构不同的第一n型功函数金属子层208a和第二n型功函数金属子层208b叠加而成,利用第一n型功函数金属子层208a和第二n型功函数金属子层208b的晶格结构不同,能形成晶格排列变化的第一界面层,而晶格排列变化的第一界面层则作为阻挡金属导电材料层209的金属向下扩散的阻挡层,所以,本发明实施例的阻挡金属导电材料层209的金属向下扩散的阻挡层能采用n型功函数金属层208实现,这样能减少额外形成的阻挡金属导电材料层209的金属向下扩散的阻挡层如顶部阻障层的厚度或者直接取消额外形成的阻挡金属导电材料层209的金属向下扩散的阻挡层,这样有利于金属导电材料层209在较小尺寸的栅极凹槽如第一栅极凹槽中填充,有利于mos晶体管的尺寸进一步缩小。

84.另外,在栅极凹槽的尺寸不变的条件下,额外形成的阻挡金属导电材料层209的金属向下扩散的阻挡层的厚度减小时,金属导电材料层209在栅极凹槽中所填充区域的体积会增加,在有利于金属导电材料层209填充的同时,填充后的金属导电材料层209的体积也会增加,在金属导电材料层209和顶部的接触插塞的接触电阻会降低,所以能提高器件的性能。

85.本发明实施例的n型功函数金属层208分成第一n型功函数金属子层208a和第二n型功函数金属子层208b后,第二n型功函数金属子层208b采用tialc时,相对于第一n型功函数金属子层208a采用的tial,第二n型功函数金属子层208b的al含量会降低,这样会降低al向下扩散的al扩散源,能进一步降低金属向下扩散所带来的技术问题。

86.如图3所示,是本发明实施例具有hkmg的mos晶体管的制造方法的流程图;本发明实施例具有hkmg的mos晶体管的制造方法中,mos晶体管包括nmos和pmos,所述pmos和所述nmos集成在同一半导体衬底201上。所述nmos的栅极结构为第一栅极结构,所述pmos的栅极

结构为第二栅极结构,所述第一栅极结构和所述第二栅极结构的形成步骤包括:

87.步骤一、形成栅极凹槽。

88.栅极结构的形成工艺采用后栅极工艺。后栅极工艺中采用伪栅极结构,所述伪栅极结构形成于半导体衬底201表面;以所述伪栅极结构为自对准条件形成侧墙203;之后会以侧墙203为自对准条件在半导体衬底201中形成源区和漏区。之后形成第零层层间膜202。将第零层层间膜202的顶部表面研磨到和伪栅极结构的顶部表面相平,之后去除伪栅极结构形成栅极凹槽。其中,位于nmos形成区域的栅极凹槽为第一栅极凹槽,位于pmos形成区域的栅极凹槽为第二栅极凹槽。

89.在所述半导体衬底201上形成有浅沟槽隔离(sti),以实现所述pmos和所述nmos之间的隔离。

90.步骤二、形成栅介质层;所述栅介质层中包括高介电常数材料层205。

91.所述栅介质层在所述nmos形成区域和所述pmos形成区域同时形成。

92.在形成所述高介电常数材料层205之前,还包括在半导体衬底201表面形成第二界面层204的步骤。

93.在形成所述高介电常数材料层205之后,还包括形成第一覆盖层206的步骤。

94.形成所述第二界面层204、所述高介电常数材料层205和所述第一覆盖层206的步骤称为gox loop。

95.之后还包括形成第二覆盖层207。所述第一覆盖层206和所述第二覆盖层207叠加形成底部阻障层。在一些实施例中,所述pmos形成区域和所述nmos形成区域中的所述第二覆盖层207一起形成。在另一些实施例中,也能为:所述pmos形成区域和所述nmos形成区域中的所述第二覆盖层207分开形成;在形成所述p型功函数金属层之前,仅形成所述pmos形成区域中的所述第二覆盖层7。所述nmos形成区域中的所述第二覆盖层207在后续p型功函数金属层形成之后以及n型功函数金属层208形成之前形成。

96.还包括在所述pmos形成区域形成p型功函数金属层。在一些实施例中,形成所述p型功函数金属层时,所述p型功函数金属层仅形成在所述pmos形成区域中。在另一些实施例中也能为:所述p型功函数金属层同时形成在所述nmos形成区域中,之后采用刻蚀工艺去除所述nmos形成区域中的所述p型功函数金属层。

97.步骤三、采用两步生长工艺形成n型功函数金属层208,包括:

98.步骤31、形成第一n型功函数金属子层208a。

99.所述第一n型功函数金属子层208a的材料包括tial;

100.所述第一n型功函数金属子层208a采用pvd工艺沉积形成;

101.步骤32、形成第二n型功函数金属子层208b。

102.所述第二n型功函数金属子层208b的材料包括tialc。

103.所述第二n型功函数金属子层208b采用ald工艺沉积形成。

104.所述第二n型功函数金属子层208b中al含量小于50%,以降低向下扩散的al扩散源。

105.所述n型功函数金属层208由第一n型功函数金属子层208a和第二n型功函数金属子层208b叠加而成,所述第一n型功函数金属子层208a和所述第二n型功函数金属子层208b具有不同的晶格结构并在所述第一n型功函数金属子层208a和所述第二n型功函数金属子

层208b接触面处形成晶格排列变化的第一界面层。

106.在一些实施例中,所述n型功函数金属层208仅形成在所述nmos形成区域中。在另一些实施例中也能为:所述n型功函数金属层208同时形成在所述pmos形成区域中,之后所述pmos形成区域中的所述n型功函数金属层208被刻蚀去除或保留。所述pmos形成区域中的所述n型功函数金属层208保留时,所述第二栅极结构中包括所述n型功函数金属层208,所述n型功函数金属层208叠加在所述p型功函数金属层表面上。

107.在一些实施例中,在步骤三完成后,还包括在所述n型功函数金属层208的表面形成顶部阻障层的步骤,所述第一界面层和所述顶部阻障层一起实现阻挡金属导电材料层209的金属向下扩散,通过所述第一界面层减少所述顶部阻障层所需厚度,以利于所述金属导电材料层209在所述第一栅极凹槽中填充。

108.步骤四、形成金属导电材料层209,所述第一栅极结构由形成于所述第一栅极凹槽中的栅介质层、n型功函数金属层208和金属导电材料层209叠加形成,利用所述第一界面层作为阻挡所述金属导电材料层209的金属向下扩散的阻挡层。

109.所述金属导电材料层209的材料包括al。

110.所述第一栅极结构由形成于所述第一栅极凹槽中的栅介质层、n型功函数金属层208和金属导电材料层209叠加形成

111.步骤四中所述金属导电材料层209同时形成在所述pmos形成区域;所述第二栅极结构由形成于所述第二栅极凹槽中的栅介质层、p型功函数金属层和金属导电材料层209叠加形成。

112.以上通过具体实施例对本发明进行了详细的说明,但这些并非构成对本发明的限制。在不脱离本发明原理的情况下,本领域的技术人员还可做出许多变形和改进,这些也应视为本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。