半导体存储装置

1.[相关申请]

[0002]

本技术享有2020年12月25日提出申请的日本专利申请2020-217402号的优先权 权益,在本技术中援用该日本专利申请的全部内容。

技术领域

[0003]

本发明的实施方式涉及一种半导体存储装置。

背景技术:

[0004]

在半导体存储装置等半导体装置中,为了增大存储容量而采用三维构造。为了进一 步增大存储容量,形成于半导体晶圆等基板之上的薄膜的总膜厚进一步增大。在这种情 况下,由于基板及各种薄膜之间的例如热膨胀系数的差异,膜中产生之应力增大,有薄 膜因此而剥离等之忧。

技术实现要素:

[0005]

一实施方式提供一种能够减少薄膜剥离的半导体存储装置。

[0006]

根据一实施方式,提供一种半导体存储装置。半导体存储装置具备积层体、柱状体、 导电部件、板状部、及分断部。积层体中,多个导电层与多个绝缘层交替地逐层积层, 且在第1方向上的端部形成有由导电层产生的阶梯部。柱状体贯通积层体,且在与多个 导电层中的至少1层对向的部分处形成有存储单元。导电部件在积层体的下方与柱状体 电连接,并且沿着第1方向超出阶梯部延伸至积层体的侧方下部的区域。板状部在积层 体的侧方的区域内沿积层体的积层方向延伸且到达导电部件,并且沿与积层方向及第1 方向交叉的第2方向延伸。分断部配置于比板状部更靠阶梯部侧的导电部件内,将导电 部件部分地分断,且包含绝缘材料。

附图说明

[0007]

图1是实施方式的半导体存储装置的局部俯视图。

[0008]

图2是沿图1的l1-l1线的剖视图。

[0009]

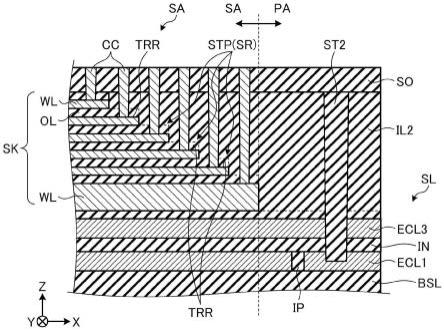

图3是沿图1的l2-l2线的剖视图。

[0010]

图4是表示实施方式的半导体存储装置中的分断部的俯视形状的局部俯视图。

[0011]

图5a~图5c是说明实施方式的半导体存储装置的单元阵列区域的形成方法的局部 剖视图。

[0012]

图6a~图6c是接着图5a~图5c之后说明实施方式的半导体存储装置的单元阵 列区域的形成方法的局部剖视图。

[0013]

图7a~图7f是说明实施方式的半导体存储装置的分断部的形成方法的局部剖视 图。

[0014]

图8是比较例的半导体存储装置的局部剖视图。

[0015]

图9a~图9c是表示实施方式的半导体存储装置的分断部的变化例的局部剖视图。

[0016]

图10a、图10b是表示实施方式的半导体存储装置的分断部的变化例的局部剖视 图。

[0017]

图11a~图11c是表示实施方式的半导体存储装置的分断部的变化例的局部俯视 图。

具体实施方式

[0018]

以下,参照附图,对本发明的非限定性例示实施方式进行说明。在所有附图中,针 对同一或对应的部件或零件,标注同一或对应的参照符号,省略重复说明。另外,附图 并非旨在示出部件或零件间、或者各种层的厚度之间的相对比,因此,可对照以下的非 限定性实施方式,由业者适当决定具体的厚度或尺寸。

[0019]

图1是实施方式的半导体存储装置的局部俯视图,图2是沿图1的l1-l1线的剖视 图,图3是沿图1的l2-l2线的剖视图。本实施方式的半导体存储装置1具有例如由硅 等半导体形成的大致矩形状基板、形成于基板上的周边电路部(在下文中进行叙述)、及 形成于周边电路部上的存储元件部。

[0020]

参照图1,半导体存储装置1在存储元件部中具有单元阵列区域ca及阶梯区域sa。 在单元阵列区域ca中设置有多个存储器柱mp,存储器柱mp在图中的xy面内以格子 状排列,分别沿图中的z方向延伸。阶梯区域sa包含阶梯部sr,如下所述,阶梯部sr 具有多个阶(在下文中进行叙述)。另外,在单元阵列区域ca及阶梯区域sa之上,设置 有包含上部配线及插塞等的上部配线层,但在图1中,省略了其图示。此外,有时将阶 梯区域sa与半导体存储装置1的端部1y之间的区域称为周边区域pa。

[0021]

另外,在半导体存储装置1中设置有将单元阵列区域ca及阶梯区域sa分割成多 个区块blk的多个第1板状部st1。各第1板状部st1沿x方向穿过单元阵列区域ca 及阶梯区域sa,终止于周边区域pa内。另外,第1板状部st1沿着图中的z方向延 伸,终止于下述源极线sl内。另外,半导体存储装置1在其周边区域pa中具有第2板 状部st2。第2板状部st2具有沿y方向及z方向延伸的板状形状。另外,在比第2板 状部st2更靠阶梯区域sa侧设置有与第2板状部st2大致平行地沿y方向延伸的分断 部ip。分断部ip如下文所说明的那样形成于源极线sl内。

[0022]

参照图2,在基板s的表层形成有被元件分离部sti分离的晶体管tr。在晶体管tr 及基板s之上,例如由氧化硅等绝缘材料形成有第1层间绝缘膜il1,在第1层间绝缘 膜il1内,设置有与晶体管tr的栅极电极等连接的通孔vg及配线ml。由这些晶体管 tr、及通孔vg、配线ml、第1层间绝缘膜il1构成控制下述存储单元之周边电路部 per。

[0023]

在第1层间绝缘膜il1之上设置有绝缘膜bsl。绝缘膜bsl例如可由氧化硅等绝 缘材料形成。此处,由于绝缘膜bsl由与第1层间绝缘膜il1相同的绝缘材料形成,因 此,绝缘膜bsl与第1层间绝缘膜il1实质上也可看作一个绝缘体部,将该绝缘体部作 为基底层,在其上方设置有存储元件部。具体而言,在绝缘膜bsl之上形成有源极线 sl。源极线sl具有第1导电层ecl1、第2导电层ecl2、及第3导电层ecl3,这些 导电层依序积层。第1导电层ecl1、第2导电层ecl2、及第3导电层ecl3例如由添 加了砷或锑等杂质的导电性多晶硅形成。

[0024]

在源极线sl上形成有积层体sk。在积层体sk中,多个绝缘层ol与多个导电层 wl交

替地逐层积层。绝缘层ol由绝缘材料,例如氧化硅形成,导电层wl由金属, 例如钨或钼等形成。

[0025]

如图所示,存储器柱mp沿着z方向(积层体sk的积层方向)贯通积层体sk、第3 导电层ecl3、及第2导电层ecl2,终止于第1导电层ecl1内。存储器柱mp具有有 底的大致圆筒状形状,具有从中心向外侧以同心圆状形成的核心层cor、通道层chn、 及存储器膜mem。此处,核心层cor例如可由氧化硅等形成,通道层chn例如可由 导电性多晶硅或非晶硅等形成。另外,如图2所示,存储器膜mem具有沿着从存储器 柱mp的中心朝向外侧的方向依序形成的隧道绝缘层tn、电荷累积层ct、及阻挡绝缘 层bk。隧道绝缘层tn及阻挡绝缘层bk例如可由氧化硅形成,电荷累积层ct例如可 由氮化硅形成。

[0026]

在积层体sk中的导电层wl与存储器柱mp的存储器膜mem对向的部分处形成 有存储单元mc。在此情况下,导电层wl作为字线发挥功能。其中,多个导电层wl 中的最上层及最下层的导电层wl与存储器柱mp对向的部分作为选择晶体管发挥功 能。即,积层体sk内的最上层的导电层wl相当于漏极侧选择栅极线,最下层的导电 层wl相当于源极侧选择栅极线。此外,例如也可使用导电性多晶硅层作为源极侧选择 栅极线。

[0027]

另外,在存储器柱mp中,存储器膜mem未设置于源极线sl的第2导电层ecl2 的下表面与上表面之间所对应之范围内。因此,在该范围内,通道层chn构成存储器 柱mp的外侧面。并且,该通道层chn与第2导电层ecl2接触。由此,通道层chn 与源极线sl电连接。即,源极线sl整体针对存储器柱mp中所形成的存储单元mc作 为其源极发挥功能。通道层chn以其外周面与第2导电层ecl2接触,所以能够增大 它们的接触面积,因此能够降低接触电阻。

[0028]

在积层体sk及存储器柱mp之上形成有绝缘膜so,与存储器柱mp的通道层chn 连接的插塞pg嵌埋至绝缘膜so中。另外,插塞pg与上部配线(未图示)连接,上部配 线和贯通积层体sk且与周边电路部per连接的贯通接点(未图示)连接。

[0029]

第1板状部st1从积层体sk的上表面起贯通积层体sk及第3导电层ecl3,终 止于第2导电层ecl2内。例如将氧化硅嵌埋至贯通积层体sk等的下述狭缝(参照图6c 的狭缝gp1)而形成第1板状部st1。其中,也可将钨或钼等金属嵌埋至其中来代替氧化 硅。在此情况下,第1板状部st1可作为与源极线sl电连接的源极线接点发挥功能。 另外,在此情况下,将金属嵌埋至狭缝之前,将由氧化硅等绝缘材料形成的衬垫层形成 于狭缝的内壁。

[0030]

图3是沿图1中的l2-l2线的剖视图,图示了阶梯区域sa及其下方的构造。其中, 在阶梯区域sa的下方也设置有周边电路部per,但它与单元阵列区域ca下方的周边 电路部per(图2)具有相同的构成,因此,在图3中省略了图示。

[0031]

阶梯部sr具有多个阶stp,在本实施方式中,各阶stp由一组导电层wl及绝缘 层ol所构成。在阶梯部sr的上方形成有第2层间绝缘膜il2。第2层间绝缘膜il2由 与绝缘层ol的绝缘材料(例如氧化硅)相同的绝缘材料形成,因此,绝缘层ol与第2层 间绝缘膜il2实质上被一体化。各导电层wl从单元阵列区域ca向阶梯区域sa沿x 方向延伸,越靠上方的导电层wl,即越远离源极线sl的导电层wl,其延伸长度越 短。由此,导电层wl成为阶stp的实质性阶面(踏面)trr。此外,最下层的导电层wl 的x方向上的端部相当于积层体sk的x方向端部,在本实施方式中,积层体sk的x 方向端部将阶梯区域sa与周边区域pa分开。此外,就下述应力缓和的观点而言,所述 第2板状部st2配置于沿x方向距离积层体sk的x方向端部5μm以内的位置,更优 选配置于距离积层体sk的x方向端部1μm以内的位置。

[0032]

在由导电层wl形成的阶面trr连接有贯通绝缘膜so及第2层间绝缘膜il2的接 点cc。接点cc例如可由钨或钼等金属形成。接点cc通过未图示的上部配线及贯通接 点与周边电路部per(图2)连接,从周边电路部per经由作为字线的导电层wl对存储 单元mc(图2)施加指定电压。此外,接点cc也可在阶梯部设置于单元阵列区域ca内 之后连接于作为该阶梯部的阶面的导电层wl。在此情况下,可省略阶梯部sr的接点 cc,由此,该阶梯部sr可为所谓虚设阶梯部。

[0033]

另外,在阶梯部sr及第2层间绝缘膜il2的下方,源极线sl的第3导电层ecl3 从单元阵列区域ca起延伸,在其下方设置有绝缘层in。绝缘层in在阶梯区域sa与 单元阵列区域ca之间的指定位置处与第2导电层ecl2相接。即,在单元阵列区域ca 中,在第3导电层ecl3的下方设置有第2导电层ecl2,另一方面,在阶梯区域sa 中,在第3导电层ecl3的下方设置有绝缘层in。

[0034]

在绝缘层in的下方,源极线sl的第1导电层ecl1从单元阵列区域ca起延伸。 另外,贯通第2层间绝缘膜il2、第3导电层ecl3、及绝缘层in的第2板状部st2终 止于第1导电层ecl1内。在本实施方式中,在与第1板状部st1形成用的狭缝相同的 步骤中形成狭缝,如下所述,将绝缘材料嵌埋至该狭缝中,从而形成第2板状部st2。 第2板状部st2、及第2板状部st2形成用的狭缝具有缓和单元阵列区域ca、及阶梯 区域sa、周边区域pa中可能产生的应力的功能。

[0035]

另外,在第1导电层ecl1中设置有将第1导电层ecl1部分地分断的分断部ip。 分断部ip可利用与构成绝缘层in之绝缘材料相同的材料形成。图4是表示分断部ip的 俯视形状的局部俯视图,具体而言,相当于第1导电层ecl1的局部俯视图。方便起见, 用虚线表示第1板状部st1的位置。如图所示,在本实施方式中,分断部ip在周边区 域pa中与第2板状部st2大致平行地沿y方向延伸,终止于第1导电层ecl1内。即, 分断部ip未将第1导电层ecl1完全分断。换言之,第1导电层ecl1通过分断部ip 的y方向端部的外侧的区域,在分断部ip的沿x方向的两侧连通,因此,在分断部ip 的两侧可实现电导通。

[0036]

以下,参照图5a~图5c及图6a~图6c,对单元阵列区域ca的形成方法进行说 明。图5a~图5c及图6a~图6c是按每个主要步骤对单元阵列区域ca的形成方法进 行说明的局部剖视图,相当于图2所示的局部剖视图。此外,在该形成方法之前,例如 在硅晶圆等半导体晶圆上形成有上文所述的周边电路部per(图2),在周边电路部per 的层间绝缘膜il1上形成有绝缘膜bsl。

[0037]

参照图5a,在绝缘膜bsl之上依序形成第1导电层ecl1、氧化硅膜ox1、牺牲膜 sc、氧化硅膜ox2、及第3导电层ecl3。此处,牺牲膜sc可由氮化硅形成。另外,在 第3导电层ecl3之上形成多个绝缘层ol与多个氮化硅层sn交替地逐层积层的积层 体tsk。此外,上文所说明的积层体sk是积层体tsk的氮化硅层sn被替换成导电层 wl而形成的。关于绝缘层ol,在积层体sk与积层体tsk中是相同的。

[0038]

接下来,如图5b所示,形成贯通积层体tsk的多个(在图示的例子中,为4个)存 储器柱mp。具体而言,通过形成贯通积层体tsk且终止于源极线sl的第1导电层 ecl1内的存储器孔,并在存储器孔的内表面依序形成存储器膜mem、通道层chn、 及核心层cor,而形成存储器柱mp。继而,如图5c所示,在4个存储器柱mp的两 侧形成狭缝gp1。这些狭缝gp1在这之后被绝缘材料嵌埋,而成为第1板状部st1,但 在此之前,其用于将氧化硅膜ox1、牺牲膜sc、

及氧化硅膜ox2替换成第2导电层 ecl2,进而用于将积层体tsk内的氮化硅层sn替换成导电层wl。

[0039]

在狭缝gp1的内侧面及底面形成衬垫层ll。衬垫层ll是为了在去除牺牲膜sc、 以及氧化硅膜ox1及ox2时保护积层体tsk内的绝缘层ol及氮化硅层sn而形成的。 作为衬垫层ll的材料,例如可例示多晶硅。通过各向异性蚀刻去除狭缝gp1的底面上 形成的衬垫层ll后,牺牲膜sc在狭缝gp1的底面上露出。继而,通过狭缝gp1依次 去除牺牲膜sc、以及氧化硅膜ox1及ox2后,如图6a所示,形成空间s1。另外,在 形成空间s1的同时,存储器柱mp的存储器膜mem也被去除,通道层chn在存储器 柱mp的侧面上露出。继而,如图6b所示,通过狭缝gp1将导电性多晶硅嵌埋至空间 s1内,由此形成第2导电层ecl2。由此,源极线sl与存储器柱mp的通道层chn电 连接。

[0040]

继而,当去除狭缝gp1内的衬垫层ll后,绝缘层ol及氮化硅层sn在狭缝gp1 的内侧面上露出。然后,通过狭缝gp1,将积层体tsk内的氮化硅层sn蚀刻去除。在 通过去除氮化硅层sn而产生的空间中嵌埋例如钨或钼等导电性材料,而形成作为字线 的导电层wl(图6c)。由此获得积层体sk。其后,将绝缘材料(例如氧化硅)嵌埋至狭缝 gp1中,在积层体sk上形成具有插塞pg的绝缘膜so后,获得单元阵列区域ca的构 造(图2)。

[0041]

此外,通过狭缝gp1去除了氮化硅层sn而产生的空间由上下相邻的2个绝缘层 ol界定,但也可通过狭缝gp1在这些绝缘层ol露出的面形成作为保护层的氧化铝膜。

[0042]

接下来,参照图7a~图7f,对第1导电层ecl1的分断部ip(图3)的形成方法进行 说明。图7a至图7f是说明分断部ip的形成方法的局部剖视图。此外,为了便于说明, 省略了比绝缘膜bsl更靠下方的构造。

[0043]

参照图7a,在绝缘膜bsl上的第1导电层ecl1之上形成氧化硅膜ox1,在其上 形成作为蚀刻掩模(硬质掩模)之氮化硅膜hm0。第1导电层ecl1及氧化硅膜ox1从单 元阵列区域ca起超出阶梯区域sa延伸至周边区域pa。即,第1导电层ecl1及氧化 硅膜ox1既形成于单元阵列区域ca中,也形成于阶梯区域sa及周边区域pa中,在 形成图5a所示的牺牲膜sc之前,在氧化硅膜ox1之上形成氮化硅膜hm0。

[0044]

接下来,如图7b所示,通过光刻步骤及蚀刻步骤在氮化硅膜hm0形成开口op1, 而获得硬质掩模hm。继而,通过使用硬质掩模hm的等离子体蚀刻法,例如反应性离 子蚀刻(rie)法等形成开口op2。开口op2贯通氧化硅膜ox1及第1导电层ecl1,终 止于绝缘膜bsl内。开口op2是应作为分断部ip的开口,如图4所示,沿y方向延 伸。

[0045]

参照图7c,在硬质掩模hm之上形成绝缘膜tso。绝缘膜tso例如由氧化硅等绝 缘材料形成,该绝缘材料嵌埋至开口op2中。接下来,通过等离子体蚀刻法去除绝缘膜 tso及硬质掩模hm。此时,如图7b所示,绝缘材料残留于第1导电层ecl1的开口 op2中,由此获得分断部ip。

[0046]

继而,如图7e所示,在氧化硅膜ox1之上形成例如氧化硅等的绝缘层in。此处, 在形成绝缘层in之前,如图5a所示在氧化硅膜ox1之上形成牺牲膜sc。该牺牲膜sc 不仅形成于单元阵列区域ca中,也形成于阶梯区域sa及周边区域pa中,因此,在阶 梯区域sa及周边区域pa中,通过光刻步骤及蚀刻步骤去除牺牲膜sc后,在氧化硅膜 ox1之上形成绝缘层in。然后,在绝缘层in之上形成氧化硅膜ox2。此时,绝缘层in 及氧化硅膜ox2实质上被一体化,在单元阵列区域ca中也形成在牺牲膜sc之上。这 些单元阵列区域ca的绝缘层in及氧化硅

膜ox2可保持原样地残留在牺牲膜sc之上, 也可通过例如化学机械研磨(cmp)法进行薄化。其后,在氧化硅膜ox2之上(阶梯区域 sa及周边区域pa中,与氧化硅膜ox1及ox2实质上一体化的绝缘层in之上)形成第 3导电层ecl3。

[0047]

继而,在第3导电层ecl之上形成多个绝缘层ol与多个氮化硅层sn交替地逐层 积层的积层体tsk。该积层体tsk与上文所说明的单元阵列区域ca中的积层体tsk(图 5a)连续。即,跨及单元阵列区域ca及阶梯区域sa而形成积层体tsk。继而,在积层 体tsk的上表面设置应该形成阶梯部sr的位置处具有开口的抗蚀剂掩模,继续进行例 如包含蚀刻、抗蚀剂掩模的细化、及再一次蚀刻的步骤,由此,如图7f所示,在积层体tsk的端部形成临时阶梯部tsr。

[0048]

其后,以覆盖临时阶梯部tsr的方式使例如氧化硅膜沉积。继而,利用例如cmp 法使该氧化硅膜平坦化后,获得第2层间绝缘膜il2。接下来,通过光刻步骤及蚀刻步 骤形成狭缝gp2。狭缝gp2贯通第2层间绝缘膜il2、第3导电层ecl3、及绝缘层in, 且终止于第1导电层ecl1内。狭缝gp2是为了形成第2板状部st2而设置的,如图4 所示,沿y方向延伸。

[0049]

此外,狭缝gp2可与狭缝gp1(图5c)同时形成。此处,如图7f所示,狭缝gp2延 伸至第1导电层ecl1,且终止于其内部,相对于此,图5c的狭缝gp1终止于牺牲膜 sc的上表面,未到达第1导电层ecl1。狭缝gp1是通过对由绝缘层ol及氮化硅层 sn所构成的积层体tsk进行蚀刻而形成的,另一方面,狭缝gp2主要是通过对由氧化 硅形成的第2层间绝缘膜il2进行蚀刻而形成的。因此,狭缝gp2是以比狭缝gp1快 的蚀刻速度形成的。由此,狭缝gp2的z方向上的长度(深度)变大。

[0050]

其后,通过狭缝gp1将图7f所示的积层体tsk的氮化硅层sn替换成导电层wl, 临时阶梯部tsr成为阶梯部sr(图3)。在参照图6c所说明的步骤中进行该替换。另外, 狭缝gp2被例如氧化硅等绝缘材料嵌埋,由此形成第2板状部st2。例如可利用等离子 体化学沉积(cvd)法将氧化硅嵌埋至狭缝gp2中。继而,在层间绝缘膜il2之上形成绝 缘膜so,形成与阶梯部sr的各阶面trr连接的接点cc后,获得图3所示的构造。

[0051]

此外,在利用cvd法形成第2板状部st2的情况下,氧化硅沉积于狭缝gp2的内 侧面及底面,内侧面上的厚度增大,在狭缝gp2的中央相互接合。以此方式将其嵌埋至 狭缝gp2中,而形成第2板状部st2。因此,沿z方向的接缝会残留于第2板状部st2 的中央。可通过这种接缝来掌握第2板状部st2的存在。

[0052]

另外,如上文所说明的那样,在通过去除氮化硅层sn而产生的空间中露出的上下 2个绝缘层ol形成作为保护层的氧化铝膜的情况下,氧化铝膜不仅可形成于狭缝gp1, 也可形成于第2板状部st2形成用的狭缝gp2的内侧面。这些内侧面的氧化铝膜在导 电性材料嵌埋至上文所述的空间中之后被去除,但也可残留于狭缝gp2的内侧面。在此 情况下,可通过残留的氧化铝,在由氧化硅形成的第2层间绝缘膜il2内界定同样由氧 化硅形成的第2板状部st2的轮廓。即,也可通过残留的氧化铝来掌握第2层间绝缘膜 il2内的第2板状部st2的存在。

[0053]

接下来,参照比较例对本实施方式的半导体存储装置1所取得的效果进行说明。图 8是比较例的半导体存储装置的局部剖视图,相当于关于实施方式的半导体存储装置1 的图7f所示的剖视图。如图所示,在比较例的半导体存储装置中,未设置分断部ip, 在绝缘膜bsl之上连续地形成有第1导电层ecl1。除了该方面以外,比较例的半导体 存储装置具有与

实施方式的半导体存储装置1相同的构成。

[0054]

在这种构成中,在例如第2板状部st2形成用的狭缝gp2形成之后进行退火等高 温步骤的情况下,有第1导电层ecl1从绝缘膜bsl剥离的风险。由至此为止的说明可 知,此时的半导体存储装置在基板s之上具有周边电路部per(图2),在其上介隔绝缘 膜bsl及源极线sl(包括绝缘层in)而形成有由绝缘层ol及氮化硅层sn形成的积层 体tsk。即,在基板s上,由各种材料形成有许多层,合计厚度相对较厚。在这种情况 下,如果在例如超过800℃的高温下进行处理,那么例如材料的热膨胀系数差异所引起 的相对较大的应力会作用于基板s及其它层之间。如此,认为在应力的作用下,例如从 第2板状部st2用的狭缝gp2的底部到第1导电层ecl1会产生龟裂,龟裂会传播到 第1导电层ecl1与绝缘膜bsl的交界,有引起两者之间的剥离pe的风险。

[0055]

另一方面,在实施方式的半导体存储装置1中,在第1导电层ecl1设置有分断部 ip。即使狭缝gp2下方的第1导电层ecl1因应力而产生龟裂,也可通过分断部ip阻 碍剥离向阶梯区域sa传播。尤其是,在本实施方式中,分断部ip是由与绝缘膜bsl相 同的绝缘材料(例如氧化硅)形成的,因此,分断部ip与绝缘膜bsl能够以较强结合力 密接。因此,能够有效地抑制第1导电层ecl1与绝缘膜bsl之间的剥离。

[0056]

另外,分断部ip并非将第1导电层ecl1完全分断,第1导电层ecl1在分断部ip 的沿x方向的两侧电连续。假如第1导电层ecl1被分断部ip完全分断,那么例如第1 导电层ecl中的比分断部ip更靠端部侧的部分被隔离,且电浮动。如此,在半导体存 储装置1的制造步骤中的例如等离子体工艺中,有该部分中产生电弧作用的风险。然而, 如上所述,在实施方式的半导体存储装置1中,第1导电层ecl1在分断部ip的沿x方 向的两侧电连续,第1导电层ecl1可通过其它电路元件接地,因此,能够抑制电弧作 用的产生。

[0057]

接下来,参照图9a~图9c及图10a~图10b对变化例进行说明。图9a~图9c 及图10a~图10b是表示分断部的变化例的局部剖视图。

[0058]

(变化例1)

[0059]

参照图9a,在第1导电层ecl1设置有分断部ip1,在第3导电层ecl3设置有分 断部ip2。在此情况下,分断部ip1、ip2可具有相同的俯视形状,可使一侧的宽度(x方 向上的长度)大于另一侧的宽度。另外,分断部ip1、ip2可皆由与绝缘层in相同的绝缘 材料形成。在此情况下,即使在第2板状部st2用的狭缝gp2的下方,第1导电层ecl1 与绝缘层bsl之间发生剥离,也可利用分断部ip1来抑制剥离的传播。另外,在分断部ip1、ip2具有相同的平面形状的情况下,在形成第3导电层ecl3后,不仅能够通过一 个光阻掩模在第1导电层ecl1形成作为分断部ip1的开口(相当于图7b的开口op2), 而且能够在第3导电层ecl3形成分断部ip2用的开口。因此,与仅在第1导电层ecl1 形成分断部ip的情况相比,能够减少步骤数。

[0060]

(变化例2)

[0061]

参照图9b,第1导电层ecl1在x方向上的延伸长度比第3导电层ecl3在x方向 上的延伸长度短,第1导电层ecl1的x方向端部与绝缘层inl相接。绝缘层inl可由 与绝缘层in及绝缘膜bsl相同的绝缘材料,例如氧化硅形成。另外,在第3导电层 ecl3设置有分断部ip3,在第3导电层ecl3中的比分断部ip3更靠x方向端部侧,第 2板状部st2终止于第3导电层ecl3内。在此情况下,有第3导电层ecl3与绝缘层 in之间发生剥离的风险,但是能够通过分断部ip3来抑制剥离的进展。

[0062]

此外,该变化例也同样地,第2板状部st2形成用的狭缝gp2可与第1板状部st1 形成用的狭缝gp1同时形成,例如,可通过在蚀刻条件下调整蚀刻速度,而使狭缝gp1 的底面位于牺牲膜sc的上表面(参照图5c),并且使狭缝gp2的底面位于第3导电层 ecl3内。另外,绝缘层inl可通过如下方式形成:例如在图7b中,将x方向上比开口 op1宽的开口设置于硬质掩模hm,使用该硬质掩模hm,通过蚀刻去除第1导电层 ecl1后,形成绝缘膜tso(图7c),对整个面进行回蚀。

[0063]

(变化例3)

[0064]

图9c中图示了上文所述的变化例2的进一步的变化例3。即,变化例3与变化例2 的不同之处在于,第2板状部st2贯通第3导电层ecl3且终止于绝缘层inl内,其它 方面相同。如上所述,绝缘层in、绝缘层inl、及绝缘膜bsl是利用相同的绝缘材料 一体形成的。因此,第2板状部st2形成用的狭缝gp2的底面不容易产生龟裂,倒是第 3导电层ecl3与绝缘层in的界面有可能发生剥离。然而,如本例所述,在第3导电层 ecl3设置有分断部ip3,因此,即使发生剥离,也能够抑制该剥离的传播。此外,延伸 至绝缘层inl的狭缝gp2可通过在与第1板状部st1用的狭缝gp1同时形成时调整蚀 刻速度来形成。

[0065]

(变化例4)

[0066]

参照图10a,不同于变化例2及变化例3,在变化例4中,第3导电层ecl3在x 方向上的延伸长度较短,第3导电层ecl3的x方向端部与第2板状部st2分离,与绝 缘层inu相接。绝缘层inu可由与绝缘层in及第2层间绝缘膜il2相同的绝缘材料, 例如氧化硅形成。第2板状部st2贯通第2层间绝缘膜il2、绝缘层inu、绝缘层in, 且终止于第1导电层ecl1内。分断部ip设置于第1导电层ecl1。因此,能够抑制第 1导电层ecl1与绝缘膜bsl的界面可能发生的剥离。此外,绝缘层inu可通过在形成 第3导电层ecl3后进行光刻步骤、蚀刻步骤、绝缘膜的沉积步骤、及平坦化步骤来形 成。

[0067]

另外,如图10b所示,不仅是第3导电层ecl3的x方向端部,第1导电层ecl1 的x方向端部也同样与第2板状部st分离。在此情况下,第2板状部st2贯通第2层 间绝缘膜il2、绝缘层inu、绝缘层in(第2层)、绝缘层inl,且终止于绝缘膜bsl内。 在本例中,分断部ip既未形成于第1导电层ecl1,也未形成于第3导电层ecl3。此 处,在第2板状部st2形成用的狭缝gp2(图7f)的侧面出现了绝缘层inl与绝缘膜bsl 的界面,也存在龟裂从该界面发展的可能性。然而,绝缘层inl与绝缘膜bsl可利用 相同的绝缘材料形成,因此,两者被牢固地连接,并且两者之间不存在热膨胀系数差, 因而不容易产生应力。因此,可防止这种龟裂沿着绝缘层inl与绝缘膜bsl的界面向 积层体sk侧传播。

[0068]

此外,第2板状部st2形成用的狭缝gp2可贯通绝缘膜bsl,且到达绝缘膜bsl 下方的周边电路部per的第1层间绝缘膜il1内,因此,第2板状部st2也可同样终 止于第1层间绝缘膜il1内。换言之,第2板状部st2只要与基板s及第1层间绝缘膜 il1内的通孔vg、配线ml(图2)等配线层分离,那么也可终止于绝缘膜bsl及第1层 间绝缘膜il1中的任一层内。即,这些层可利用相同的绝缘材料形成,因此,界面被牢 固地连接,并且不存在热膨胀系数差,不容易产生层间的应力,通过与材料不同于这些 层的基板s及配线层分离而使第2板状部st2终止,能够有效地抑制界面上的剥离的传 播。

[0069]

接下来,参照图11a~图11c对分断部的其它变化例进行说明。图11a~图11c是 表示分断部的局部俯视图。即,下述变化例中的分断部的俯视形状与上文所述的分断部 ip等

不同。

[0070]

(变化例5)

[0071]

如图11a所示,变化例5中的分断部ip4并非在y方向上连续,而是间断地延伸。 即使在这种情况下,也可以通过分断部ip4来抑制第1导电层ecl1与作为其基底层的 绝缘膜bsl之间可能发生的剥离。

[0072]

(变化例6)

[0073]

如图11b所示,变化例6中的分断部ip5是与变化例5的分断部ip4相同的俯视形 状沿x方向以2列配置而构成。并且,2列分断部ip5在列与列之间在y方向上彼此错 开配置。因此,能够通过分断部ip5更有效地抑制第1导电层ecl1与作为其基底层的 绝缘膜bsl之间可能发生的剥离。

[0074]

此外,如图11c所示,第2板状部st2可沿x方向排列且形成为2列,也可形成为 3列或4列以上。另外,图11c中图示了分断部ip4,但也可设置2列第2板状部st2、 及分断部ip、ip1~ip3、ip5中任一者。进而,分断部ip2及分断部ip3的俯视形状可与 分断部ip4相同,另外,分断部ip2及分断部ip3可沿x方向以2列排列。换言之,分 断部ip、ip1~ip3、ip5的俯视形状可与分断部ip4同样地间断地延伸,而非在y方向 上连续。另外,也可依照分断部ip5,将2列间断地延伸的分断部ip、ip1~ip3在y方 向上错开设置。

[0075]

已对本发明的若干个实施方式进行了说明,但这些实施方式是作为例子提出的,并 不意图限定发明的范围。这些新颖的实施方式可以其它各种方式实施,可在不脱离发明 主旨的范围内进行各种省略、替换、变更。这些实施方式及其变化包含在发明的范围及 主旨中,并且包含在权利要求书中记载的发明及其均等的范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。