1.本发明涉及半导体制造技术领域,尤其涉及一种半导体表面处理方法。

背景技术:

2.随着半导体制造技术的发展,半导体电子元件的应用越来越广泛。为适应半导体电子元件的不同需求,半导体电子元件的表面有各种的设计和改进。例如,一些半导体电子元件为迎合低摩擦力的需求而将表面设计成光滑平坦,一些半导体为适应形状或兼容性而将设计成弧形表面。

3.对于一些与外界媒介相配合的半导体元件,因其内的电子元件如传感器、磁性元件十分灵敏、脆弱,故此在其表面覆盖一层保护膜,以使其免受外界的干扰,如静电荷、外部磁场等,该保护膜通常是绝缘的含碳保护膜。但是,对于含碳保护膜来讲,硅原子尺寸越大,半导体表面产生的应力越大,并且其表面积累的能量越高,从而影响半导体性能。

技术实现要素:

4.本发明实施例所要解决的技术问题在于,提供一种半导体表面处理方法,能够有效降低半导体表面产生的应力,并且减少半导体表面聚集的能量,从而改善半导体的性能。

5.为了解决上述技术问题,本发明实施例提供了一种半导体表面处理方法,包括:

6.对半导体基底进行预清洗,并对预清洗后的半导体基底进行干燥处理;

7.将干燥后的半导体基底放入真空室中,抽真空并加热到温度稳定在200℃~250℃;

8.向真空室内通入氩气,并在真空室内的气压达到5pa~8pa时,对半导体基底施加-1000v的偏压,对半导体基底进行轰击清洗;其中,氩气的流量为10ml/min;

9.采用fcva法,以0度角度在轰击清洗后的半导体基底上沉积类金刚石膜,相应形成dlc层;其中,在沉积过程中所使用的标靶为碳靶;

10.采用ibe或ecr刻蚀法,以四氟化碳作为掺杂气体在dlc层上掺杂氟离子,相应形成氟离子掺杂层;其中,四氟化碳的流量为40sccm。

11.进一步地,所述对半导体基底进行预清洗,并对预清洗后的半导体基底进行干燥处理,具体包括:

12.对半导体基底进行第一次超声波清洗,并使用nmp浸泡以及使用ipa作为清洗溶液;其中,nmp的温度为20℃~40℃,浸泡时间为20min;

13.采用去离子水将第一次清洗后的半导体基底冲洗干净,并放入ipa溶液中进行第二次超声波清洗;其中,第二次清洗时间为30min;

14.对第二次清洗后的半导体基底进行干燥处理。

15.进一步地,所述对半导体基底进行轰击清洗,具体包括:

16.采用氩等离子体、氩氧混合气体、氩乙烷混合气体、氮气或氦气对半导体基底进行轰击清洗;其中,轰击清洗时间为30min。

17.进一步地,所述dlc层的厚度为12nm~30nm。

18.进一步地,在掺杂过程中所使用的电源功率为5kw,真空室内的气压为0.1pa~0.3pa,掺杂时间为80min~100min。

19.进一步地,所述氟离子掺杂层的厚度为2nm~6nm。

20.与现有技术相比,本发明实施例提供了一种半导体表面处理方法,首先对半导体基底进行预清洗,并对预清洗后的半导体基底进行干燥处理;接着将干燥后的半导体基底放入真空室中,抽真空并加热到温度稳定在200℃~250℃;向真空室内通入氩气,并在真空室内的气压达到5pa~8pa时,对半导体基底施加-1000v的偏压,对半导体基底进行轰击清洗;其中,氩气的流量为10ml/min;然后采用fcva法,以0度角度在轰击清洗后的半导体基底上沉积类金刚石膜,相应形成dlc层;其中,在沉积过程中所使用的标靶为碳靶;最后采用ibe或ecr刻蚀法,以四氟化碳作为掺杂气体在dlc层上掺杂氟离子,相应形成氟离子掺杂层;其中,四氟化碳的流量为40sccm;能够有效降低半导体表面产生的应力,并且减少半导体表面聚集的能量,从而改善半导体的性能。

附图说明

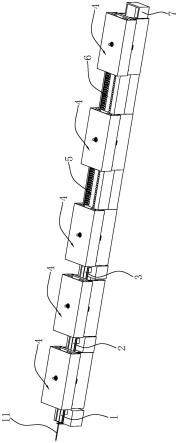

21.图1是本发明提供的一种半导体表面处理方法的一个优选实施例的流程图。

具体实施方式

22.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本技术领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

23.本发明实施例提供了一种半导体表面处理方法,参见图1所示,是本发明提供的一种半导体表面处理方法的一个优选实施例的流程图,所述方法包括步骤s11至步骤s15:

24.步骤s11、对半导体基底进行预清洗,并对预清洗后的半导体基底进行干燥处理;

25.步骤s12、将干燥后的半导体基底放入真空室中,抽真空并加热到温度稳定在200℃~250℃;

26.步骤s13、向真空室内通入氩气,并在真空室内的气压达到5pa~8pa时,对半导体基底施加-1000v的偏压,对半导体基底进行轰击清洗;其中,氩气的流量为10ml/min;

27.步骤s14、采用fcva法,以0度角度在轰击清洗后的半导体基底上沉积类金刚石膜,相应形成dlc层;其中,在沉积过程中所使用的标靶为碳靶;

28.步骤s15、采用ibe或ecr刻蚀法,以四氟化碳作为掺杂气体在dlc层上掺杂氟离子,相应形成氟离子掺杂层;其中,四氟化碳的流量为40sccm。

29.作为上述方案的改进,所述对半导体基底进行预清洗,并对预清洗后的半导体基底进行干燥处理,具体包括:

30.对半导体基底进行第一次超声波清洗,并使用nmp浸泡以及使用ipa作为清洗溶液;其中,nmp的温度为20℃~40℃,浸泡时间为20min;

31.采用去离子水将第一次清洗后的半导体基底冲洗干净,并放入ipa溶液中进行第二次超声波清洗;其中,第二次清洗时间为30min;

32.对第二次清洗后的半导体基底进行干燥处理。

33.作为上述方案的改进,所述对半导体基底进行轰击清洗,具体包括:

34.采用氩等离子体、氩氧混合气体、氩乙烷混合气体、氮气或氦气对半导体基底进行轰击清洗;其中,轰击清洗时间为30min。

35.作为上述方案的改进,所述dlc层的厚度为12nm~30nm。

36.作为上述方案的改进,在掺杂过程中所使用的电源功率为5kw,真空室内的气压为0.1pa~0.3pa,掺杂时间为80min~100min。

37.作为上述方案的改进,所述氟离子掺杂层的厚度为2nm~6nm。

38.结合上述实施例,在具体实施时,首先,采用超声波对半导体基底的表面进行预清洗,在第一次超声波清洗过程中,使用温度为20℃~40℃的nmp(n-甲基吡咯烷酮)溶剂浸泡半导体基底20分钟,并且使用ipa(异丙醇)溶剂作为清洗溶液,在第二次超声波清洗过程中,采用去离子水将第一次超声波清洗后的半导体基底冲洗干净,并放入ipa溶液中进行第二次超声波清洗,第二次超声波清洗持续时间为30分钟,之后对第二次超声波清洗后的半导体基底进行干燥处理(例如烘干或自然干燥处理);接着,将干燥处理后的半导体基底放入真空室中,对真空室进行抽真空并加热到真空室内的温度稳定在200℃~250℃,之后向真空室内通入流量为10ml/min的氩气(ar),当真空室内的气压达到5pa~8pa时,通过对设备参数进行设定来实现电压调节,以对半导体基底施加-1000v的偏压,对半导体基底进行轰击清洗,在轰击清洗过程中,通常采用氩等离子体、氩氧混合气体、氩乙烷混合气体、氮气、氦气中的任意一种对半导体基底表面进行轰击清洗,轰击清洗持续时间为30分钟;然后,采用fcva法(过滤阴极真空电弧法),以0度角度在轰击清洗后的半导体基底上沉积类金刚石膜,相应形成dlc层,在沉积dlc层的过程中,所使用的标靶是高纯度的碳靶,形成的dlc层的厚度为12纳米~30纳米;最后,采用ibe刻蚀法(离子束刻蚀法)或ecr刻蚀法(微波电子回旋共振等离子体刻蚀法),以流量为40sccm的四氟化碳(cf4)作为掺杂气体在dlc层上掺杂氟离子,相应形成氟离子掺杂层,在掺杂氟离子的过程中,所使用的电源功率为5kw,真空室内的温度为200℃~250℃,真空室内的气压为0.1pa~0.3pa,掺杂持续时间为80分钟~100分钟,形成的氟离子掺杂层的厚度为2纳米~6纳米。

39.需要说明的是,在dlc层表面掺杂氟离子时,氟离子会有一部分渗透到dlc层中,相应形成厚度为2nm~6nm的氟离子掺杂层,另外还有一部分氟离子会在氟离子掺杂层的表面相应形成氟离子层。

40.可以理解的,四氟化碳用于射频源产生等离子体,氟离子通过ibe或ecr掺杂到dlc层中,在dlc层上形成碳-氟键(c-f键),c-f键是很强的化学键,其具有良好的防水性能(疏水性),即使在半导体进行清洗工序(如水清洗或溶剂清洗)时,c-f键亦不会被破坏,从而很好地保护半导体的表面;正因为其良好的疏水性,通过水接触角测试可得知,含氟离子的半导体表面的表面张力大大下降,从而使半导体性能得到提高,在与媒介配合使用时,半导体的表面不会积聚溶剂而影响半导体和媒介的性能,在非干燥的工作环境下,半导体表面也不会积聚液体、油污等,因此不会影响半导体的内部元件的性能。

41.综上,本发明实施例所提供的一种半导体表面处理方法,首先对半导体基底进行预清洗,并对预清洗后的半导体基底进行干燥处理,接着将干燥后的半导体基底放入真空室中,抽真空并加热到温度稳定在200℃~250℃,向真空室内通入氩气,并在真空室内的气

压达到5pa~8pa时,对半导体基底施加-1000v的偏压,对半导体基底进行轰击清洗,然后采用fcva法,以0度角度在轰击清洗后的半导体基底上沉积类金刚石膜,相应形成dlc层,最后采用ibe或ecr刻蚀法,以四氟化碳作为掺杂气体在dlc层上掺杂氟离子,相应形成氟离子掺杂层,其中,沉积的dlc层和氟离子掺杂层的表面积蓄的能量比较低,并且具有较高的硬度和耐磨性,从而能够有效降低半导体表面产生的应力,减少半导体表面聚集的能量,进而改善半导体的性能。

42.以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明技术原理的前提下,还可以做出若干改进和变形,这些改进和变形也应视为本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。