1.本发明涉及晶圆重构技术的良率改进,该技术适用于需要使用与集成电路紧密共集成的化合物半导体制造的器件的任何应用。

背景技术:

2.利用化合物半导体的特定材料特性的应用可以是光发射应用(例如led显示器、vecsel阵列)、光敏应用(例如nir成像仪、uv成像仪);两者的组合(例如,用于光通信或神经刺激的发光和/或光电检测)或电气特性应用(用于功率和/或高频开关的晶体管和二极管)。

3.本发明的可能应用是用于增强现实应用的微型发光二极管显示器。对全高清(fhd)或更高分辨率显示器的需求已经增加。fhd显示器需要非常大的裸片大小和非常紧密的像素间距。

4.通过使用具有直接带隙iii-v、iii-n或iii-p材料的发光二极管(led)来实现显示器的组装技术例如从ep 3667 745 a1已知。该文献示出了在载体衬底上重构的发光二极管。一个或多个led器件作为化合物半导体堆叠体在载体衬底上重构。led器件可包括led阵列或微型led阵列。然而,外延晶圆上的缺陷可以显著影响由外延晶圆制成的显示器件。任何无法去除的缺陷或颗粒将导致良率损失。生产大裸片需要严格的良率控制。这又将推动成本并影响可制造性。此外,这是多维的工程挑战。

技术实现要素:

5.因此,本发明的目的是提供一种以高良率生产用于晶圆重构的裸片的方法、系统和晶圆,特别是通过解决上述限制而最大化由外延晶圆生产的可用裸片的数量。

6.该目的是通过根据本发明的方法、系统、以及使用该裸片生产的重构晶圆实现的。具体实施方式包含进一步的改进。

7.根据本发明的第一方面,一种方法生产用于晶圆重构的裸片。该方法包括检查外延晶圆(也称为epi晶圆)以检测一个或多个缺陷的步骤。该方法还包括在具有检测到的缺陷的外延晶圆上覆盖划片图式。此外,该方法包括将划片图式中的裸片分类为良裸片或坏裸片的步骤。此外,该方法包括将外延晶圆划片并将良裸片转移到目标晶圆或载体晶圆上的步骤。本发明旨在提高晶圆级外延层的质量。此外,本发明旨在增加来自每个外延晶圆的外延层或良裸片的数量。

8.因此,所提出的解决方案在晶圆级本身解决了该问题,并通过考虑外延晶圆上存在的缺陷来最大化外延晶圆的使用。

9.优选地,所述方法还包括关于缺陷调整划片图式以优化裸片相对于检测到的缺陷的位置,从而由外延晶圆产生最大数量的良裸片的步骤。划片图式可以战略性地定位,使得大多数缺陷位于裸片外部。优选地,缺陷定位在每个裸片的边缘上。从而增加每个外延晶圆可以获得的良裸片的数量。

10.有利地,所述方法还包括通过光学和/或电学技术检查外延晶圆的步骤。有利地,可以通过诸如光谱或显微技术的光学技术来检测缺陷。外延晶圆上的缺陷的映射图像也可以可选性地用于将来的参考。外延晶圆上的缺陷映射可优选地用于机器学习或用于缺陷确定和分类过程的自动化。

11.优选地,所述方法包括以下步骤:基于检测到的缺陷的密度和/或检测到的缺陷相对于划片图式的位置选择良裸片,和/或基于通过所有选择的裸片的光亮度或阴极亮度或其组合测量的裸片的光学特性选择良裸片,和/或基于膜粗糙度、膜厚度、膜化学组成或其组合选择良裸片。这些选择标准有助于提高良率。可以测量膜(外延层)的特性,诸如通过afm或干涉测量粗糙度,通过椭圆率计测量膜厚度,通过拉曼光谱或红外光谱测量化学组成。

12.优选地,对外延晶圆的检查可以在两个步骤中执行:一个步骤在原始接收的外延层上执行,以检测在后处理中可能不再可见的缺陷;第二个步骤在处理后执行,以检测接合层或组成上的缺陷。

13.有利地,所述方法还包括从非功能化晶圆或非结构化晶圆或空白外延晶圆开始的步骤。有利地,外延晶圆在衬底上具有iii-v、iii-n或iii-p材料的外延层。换句话说,外延晶圆上没有任何电路,仅具有外延层。通常,外延层也称为epi层。

14.外延层可以通过金属有机化学气相沉积(mocvd)、分子束外延(mbe)或任何合适的技术来生长。优选地,衬底可以是蓝宝石、gaa、ge,或者更优选是硅或任何其他合适的衬底。有利地,测量空白外延晶圆上的缺陷将允许表征已经在晶圆级的缺陷。因此,本发明的方法允许优化外延晶圆上关于检测到的缺陷的划片图式位置,以增加每晶圆的良裸片的数量。

15.有利地且优选地,所述方法包括通过诸如机械划片、等离子划片、激光划片、锯划片、刀片划片或隐形划片的技术将外延晶圆划片的步骤。这些划片技术允许在外延晶圆上应用的任何划片图式的划片。

16.有利地且优选地,所述方法还包括检测外延晶圆上的缺陷的步骤,所述缺陷例如外延层缺陷、外延凹坑、孔、滑移线、裂纹、颗粒、夹杂物、突起或其组合。

17.优选地,良裸片包括具有零缺陷容忍的中心区、具有高缺陷容忍的外围区、和/或具有低缺陷容忍的位于中心区和外围区之间的中间区,并且优选地,其中大于3μm的像素间距在高缺陷区中容忍的范围为500nm至5μm大小的缺陷,且在低缺陷容忍范围中容忍300nm至500nm的缺陷大小。

18.更有利的是,该方法还包括转移良裸片的步骤,可以(a)各个地转移到目标晶圆,或者(b)通过中间载体晶圆集体地转移。

19.根据本发明,载体晶圆是临时使用的,并且不是重构晶圆的一部分。载体晶圆仅用于将良裸片转移到目标晶圆。而目标晶圆形成重构晶圆的一部分。

20.优选地,所述方法(a)包括将各个良裸片转移到目标晶圆的步骤。转移方法可以是直接拾取和放置转移或任何其他合适的转移方法。其中,接合层优选为无机层,诸如sicn或sio2或任何已知接合材料。在转移期间,可以可选地在接合之前对各个外延裸片执行附加的清洁和检查步骤。

21.替选地,所述方法(b)包括通过载体晶圆集体转移外延裸片的步骤,包括通过临时接合层将良裸片转移到载体晶圆上。可选地,可以在接合之前执行各个裸片的清洁和/或检

查步骤。该方法(b)还包括通过接合层将良裸片从载体晶圆集体转移到目标晶圆的步骤。将载体晶圆解接合。良裸片分布在目标晶圆上,以形成重构晶圆。

22.有利地且优选地,所述方法还包括以下步骤:在不同阶段完全或部分移除良裸片的衬底(一个选项是当良裸片接合到目标晶圆时)以暴露无缺陷外延层、填充无缺陷外延层之间的间隙、以及平面化以形成分布在晶圆上的多个无缺陷外延裸片(或也称为epi裸片或裸片)。

23.优选地,该方法还包括以下步骤:在重构晶圆上并且通过重构晶圆到另一晶圆上的晶圆间(w2w)接合从而形成显示器件。

24.所述另一晶圆包括电子器件(尤其是晶体管、优选cmos晶体管),用于驱动和/或控制通过构造外延晶圆而制成的电致发光二极管。所述另一晶圆有利地可以是cmos晶圆。

25.有利地且优选地,可以优化划片图式,使得产生对于中心区具有零缺陷的良裸片,而根据缺陷率标准,外围区和/或中间区仍然具有有限的缺陷。

26.有利地且优选地,所述方法还包括在外延晶圆上覆盖划片图式的步骤。划片图式可以是规则矩形网格或不规则图式。为了提高良裸片的数量,使用检测到的缺陷的位置和大小来优化划片图式。这可导致不规则的划片图式,因为裸片放置在检测到的缺陷周围,以产生更多的良裸片。每个裸片(基于将用于的应用)以不与任何检测到的缺陷重叠或仅在裸片边缘与检测到的缺陷重叠的方式定位。基于缺陷率标准,定制的划片图式可产生具有零缺陷的良裸片和具有可接受缺陷的良裸片的组合。优选地,图式的定制可以从外延晶圆的具有最少缺陷的部分开始,其中可以在规则图式中放置更多的裸片作为起始点。更优选地,为了从起始点构建划片图式,在遇到检测到的缺陷时,可以移动裸片以避免覆盖或仅在裸片边缘覆盖。裸片可以在任何方向上侧向移动,以产生更多数量的良裸片。裸片可以在包括最大数量的良裸片的外延层上形成连续图式或不连续图式。因此,逐裸片定制将显著提高良裸片的良率。

27.选择或定制合适的划片图式,使得优化为大多数缺陷位于裸片外部。通过这样做,每晶圆的裸片良率将显著提高。

28.根据本发明的第二方面,提供了一种生产用于晶圆重构的裸片的系统。该系统包括被配置为检查外延晶圆以检测一个或多个缺陷的处理装置。该处理装置还配置为在外延晶圆的测量的缺陷上覆盖划片图式。在该情况中,处理装置被配置为将裸片分类为良裸片或坏裸片,并且该处理装置还被配置为使用划片装置将外延晶圆划片。优选地,处理装置还被配置为自动执行这些步骤。更优选地,处理装置可以自学习以改进对外延晶圆的缺陷的检查、划片图式的定位、对良裸片或坏裸片分类、将外延晶圆划片以获得良裸片。可选地,在通过进一步检查来划片后,可以进一步选择良裸片。由此,通过自学习,随着时间的推移,可以自动化和改进良裸片的生产。

29.优选地,划片装置可以是锯、激光器、等离子体等。

30.有利地,处理装置被配置为映射外延晶圆上检测到的缺陷。此外,处理装置被配置为测试使用良裸片制造的显示器件的特性,并将缺陷映射与显示器件的特性进行比较。有利地,可以确定该过程期间使用的缺陷或缺陷率标准是否导致不令人满意的显示特性。由此,可以进一步优化良裸片的选择标准。此外,处理装置可以使用该信息来自学习和改进良裸片的选择标准。换句话说,如果作为良裸片通过的所有裸片在显示器件中也表现良好,则

处理装置可以自学习。在显示器件的特性不符合预期标准的情况下,可以检查与使用的良裸片对应的缺陷映射,以便调整选择标准以提高良率。

31.根据本发明的第三方面,重构晶圆包括良裸片和目标晶圆。从外延晶圆中选择良裸片,并且多个良裸片固定在目标晶圆上以形成重构晶圆。优选地,良裸片和/或目标晶圆具有sicn层或其他接合材料以将它们接合在一起。

32.因此,根据本发明制造的由良率改进的良裸片形成的重构晶圆是有成本效益的。

33.优选地,重构晶圆包括由外延晶圆产生并固定在目标晶圆上的良裸片。外延晶圆包括衬底上的外延层。外延层为iii-v、iii-n或iii-p层材料。此外,目标晶圆是硅晶圆或其他合适的材料。此外,外延晶圆的衬底可以是蓝宝石、硅或任何其他合适的材料。

34.有利地,重构晶圆适合于与另一晶圆的晶圆间混合接合以形成显示器件。优选地,接合为阳极接合或熔合接合、或优选是金属间接合或任何可用的晶圆间接合。由此可以实现具有紧密像素间距范围的大裸片面积。优选地,使用晶圆间混合接合制造显示器件能够实现低于3μm的像素间距范围。因此,根据本发明的重构晶圆满足用于制造fhd显示器的要求。

附图说明

35.本发明的示例性实施方式现在仅通过示例而非限制性地参考附图进一步解释。在附图中:

36.图1示出了将led与cmos晶圆集成的可能路径的流程图;

37.图2示出了(a)蓝宝石晶圆、(b)硅晶圆上的gan-led外延层的颗粒水平的示例和(c)蓝宝石和硅的颗粒计数图;

38.图3示出了在gan led外延层顶部上的生长缺陷的sem图像的示例:(a)外延凹坑、(b)滑移线、(c)颗粒和(d)夹杂物;

39.图4示出了通过(a)光亮度和(b)阴极亮度技术而实现的外延晶圆的亮度图像的示例;

40.图5示出了标准cmos、si上的gan(a 和bb)、gaas上的allngap、和蓝宝石上的gan的iii-v外延层片上良率与裸片大小的图的示例;

41.图6示出了生产用于晶圆重构的良裸片并使用重构晶圆制造装置的流程图的示例性实施方式;

42.图7示出了硅晶圆上的gan的缺陷检查的示例性实施方式:(a)缺陷检查图和不同类别的缺陷分类、(b)硅晶圆上的gan的覆盖划片图式、以及(c)将坏裸片标记为x;

43.图8示出了覆盖cmos晶圆的裸片和良外延裸片的示例性实施方式;

44.图9示出了划片图式的示例性实施方式:(a)标准矩形网格、(b)优化的矩形网格、和(c)不规则划片图式;

45.图10示出了用于生产用于晶圆重构的裸片的系统;

46.图11示出了使用载体晶圆或直接在目标晶圆上产生晶圆重构的流程图的示例性实施方式;

47.图12示出了用于晶圆重构的方法的示例性实施方式:(a)将外延裸片接合在载体衬底上,(b)填充裸片之间的间隙并平面化,以及(c)重构晶圆;以及

48.图13示出了集成示意图的示例性实施方式,该集成示意图从外延晶圆和载体晶圆开始,直到使用晶圆间接合的微型led显示器。

具体实施方式

49.现在将详细参考本发明的其示例在附图中示出的实施方式。然而,可以对本发明的以下实施方式进行各种修改,并且本发明的范围不受以下实施方式的限制。

50.在本发明中,参考了此处定义的不同类型的晶圆。外延晶圆是指具有覆盖膜的晶圆或非功能化晶圆。外延晶圆可以称为epi晶圆。载体晶圆是指用于将良裸片(或epi裸片)转移到目标晶圆上的晶圆。载体晶圆是在可选的过程步骤中使用的临时晶圆。载体晶圆不形成重构晶圆的一部分。目标晶圆是良裸片转移到其上并接合的最终晶圆。目标晶圆是重构晶圆的一部分。另一晶圆包括电子装置、尤其是晶体管、优选用于驱动和/或控制电致发光二极管的cmos晶体管。在图1中,示出了将微型led与另一晶圆100集成的可能路径,其中,另一晶圆包括电子装置、尤其是晶体管、优选为cmos晶圆。

51.微型led显示器的下一代应用需要非常紧凑的3μm或更小的像素间距以及非常大的阵列以实现1920

×

1280个像素的全高清(fhd)。图1示出了在cmos101上实现微型led的可能路径。通过裸片到晶圆转移102,可以实现超过10μm的像素间距,其中每像素103具有带rgb裸片的一个裸片,每显示器104具有带b rg下转换或通过单独的裸片和组合器实现的rgb的一个裸片。然而,fhd显示器需要更小的像素间距范围。小于10μm的像素间距可通过全晶圆单片集成105实现。

52.例如,fhd显示器所需的像素数量将自动转换为面积为6mm

×

4mm(具有3μm的间距)的非常大的裸片大小。这又将导致严格的良率要求。因此,当使用全晶圆单片集成时,晶圆间106是一种有前途的方法。这允许在大的裸片大小(优选3μm或更小)上实现紧密的像素间距。

53.在外延晶圆制备期间面临的挑战可以是由于多种原因造成的,例如生长条件、生长方法、生长温度或温度梯度。这些导致外延晶圆具有不可避免的缺陷。

54.用于led的化合物半导体通常通过在晶格匹配紧密的外来衬底(异质外延)上的外延工艺来生长。生长技术可以是分子束外延(mbe)或更常见的金属有机化学气相沉积(mocvd)。本发明的外延晶圆例如可以是iii-v、iii-n或iii-p外延led层。外延层的缺陷率水平明显高于硅cmos晶圆。由于外延晶圆中的缺陷是不可避免的,因此需要方法来解决缺陷以提高良率。

55.讨论了外延晶圆上的缺陷的一些原因。缺陷的第一个原因是使用了较不完美的衬底。蓝宝石是优选的,因为它提供了良好的晶格匹配,但导致大量缺陷。图2(a)和(b)分别示出了150mm蓝宝石晶圆201和200mm硅晶圆202上的gan led外延层的缺陷水平。蓝宝石衬底比硅衬底产生更高的缺陷计数。图2(c)示出了蓝宝石204和硅晶圆205的颗粒计数图203。蓝宝石204的颗粒计数例如为1784,而对于相同大小的硅205,其颗粒计数仅约为29。因此,使用蓝宝石外延晶圆的挑战是提高良率,从而使选择更具成本效益。

56.缺陷的第二个原因可能是外延层的生长技术,尤其是mocvd。mocvd通常仍然使用通常在洁净室之外的手动晶圆装载技术。此外,mocvd室通常不针对缺陷率而针对生产量进行优化。为了提高生产量,mocvd具有多晶圆沉积室、不锈钢生长室,并且室清洁工艺或清洁

气体远没有先进的硅cmos cvd室复杂。由于在700℃到900℃的温度下沉积几微米厚的膜需要很长的沉积时间和几小时的热升温时间的驱动,这使得单晶圆沉积室不经济,因此需要多晶圆沉积。因此,外延晶圆上的生长缺陷变得不可避免。此外,在生长过程期间,晶格失配(例如外延凹坑或滑移线)也可以导致生长缺陷出现。图3示出了在gan led外延层顶部上的生长缺陷的一些实例。图3(a)至(d)中的sem图像分别为外延凹坑301、滑移线302、颗粒303和夹杂物304。

57.第三个可能的原因与外延层沉积均匀性有关,这尤其影响最终的显示特性。外延层均匀性可以在峰值波长、内部量子效率(iqe)和/或局部均匀性方面影响显示器件的整体均匀性。图4(a)至(b)分别通过(a)光亮度401和(b)阴极亮度403示出了外延层的均匀性测量图。光亮度图401示出了来自外延层的特征发射。从亮度图可以很容易地识别外延晶圆上的均匀性。此外,与光亮度图401相对应的强度分布图402也反映层的均匀性。这些亮度方法可以用于探索散射、材料的电子结构,例如带隙、缺陷、共振现象等。在该情况中,阴极亮度图403还反映外延层的缺陷。

58.低良率的第四个原因可以通过用于将cmos晶圆与外延晶圆接合的接合方法来解释。如果cmos晶圆通过晶圆间转移与外延led晶圆接合,则可以根据标准缺陷密度为0.1cm-2

的裸片大小假设cmos晶圆具有非常高的良率。然而,外延晶圆的缺陷密度为标准值的10倍至100倍高,这意味着iii-v外延层将显著限制制造期间的良率。

59.在图5中,绘制了iii-v外延层片上良率中的高缺陷密度相对裸片大小的影响500。这里假设任何颗粒或外延缺陷大于0.3μm将创建非工作像素。当然,对于最终产品,像素水平的可接受缺陷率可能有所不同。手机的标准缺陷率水平是每显示器零缺陷,而在监控器或电视中,通常每一百万像素可以接受3个至6个不亮且不聚集在一起的非工作像素。对于图5,使用手机缺陷水平。

60.在图5中,相对于cmos,即使是最好的硅外延晶圆上的gan也显示出显著的良率损失。对于fhd显示器,裸片面积显著更大,因此,裸片良率显著下降,如图所示。事实上,缺陷率甚至更差,这是因为标准晶圆检查数据排除了靠近边缘的缺陷(边缘排除为2mm至10mm),在边缘处由于晶圆斜面产生的滑移线而存在特别高的缺陷计数。这些与各个裸片良率无关,但可以在晶圆间接合过程中导致完全失败。

61.影响良率的第五个原因是iii-v晶圆由于固有应力而产生的高晶圆弯曲。iii-v材料通过在非常高的温度下生长而晶格匹配,并且当晶圆冷却时,外延层的膨胀系数不同于衬底而导致晶圆弯曲。为了减少晶圆弯曲,衬底晶圆所在的热卡盘不是平坦的,而是预成形的,以反向补偿(over-compensate)应力引起的弯曲。这项技术对硅晶圆上的gan非常有效,但对蓝宝石晶圆不是很有效。

62.由于结构尺寸不是很关键,因此led行业已经学会处理高晶圆弯曲。然而,如果iii-v外延晶圆需要在cmos制造设施中加工,则这是一个重大问题,在cmos制造设施中,工具不接受晶圆弯曲大于45μm的晶圆。如果临界尺寸变得小得多,则晶圆弯曲标准会变得更严格,这是因为晶圆弯曲可以影响诸如光刻、cmp、干蚀刻的工艺步骤的均匀性。这意味着,iii-v外延晶圆需要预先选择,并且只有一定百分比的所选晶圆可以用于进一步加工。因此,良率受晶圆弯曲的影响。

63.本发明提供了一种通过克服所有缺点来生产用于晶圆重构的裸片的方法和系统,

并提供了高良率。

64.根据本发明,图6中用示例性流程图600示出了根据第一方面的方法的第一示例性实施方式。该流程图示出了生产良裸片以提高良率所涉及的步骤。从没有任何电功能性结构的空白外延晶圆开始对于实现高良率是高度有利的601。该方法包括检查外延晶圆以检测一个或多个缺陷的步骤602。该方法还包括在具有检测到的缺陷的外延晶圆上覆盖划片图式的步骤603。该方法还包括将覆盖划片图式的裸片分类为良裸片或坏裸片的步骤604。该方法还包括将外延晶圆划片并将良裸片直接转移到目标晶圆上或将良裸片转移到载体晶圆上,然后最终转移到目标晶圆上从而制造重构晶圆的步骤605。因此,本发明提供了一种在晶圆水平应对外延晶圆的缺陷的方法,以提高用于晶圆重构的良裸片的良率。

65.例如,硅衬底用于所提供的目标晶圆。优选地,可将sicn层施加到目标晶圆上以创建接合表面。更优选地,所选择的良裸片也可以用sicn层覆盖。有利地,sicn在良裸片与目标晶圆之间提供了高接合强度。此外,为了提高接合强度,可以执行接合之后的退火工艺。因此,可以拾取良裸片并将其放置在目标晶圆上,并通过sicn层接合。可选地,可以提供一个或多个sin层或替选的介电层作为目标晶圆表面与sicn层之间的中间层。此外,可选地,可以通过抛光这些中间层来改善平整度和粗糙度。

66.除了上述步骤之外,图6还示出了使用根据本发明的方法制成的重构晶圆制造器件结构的步骤606。在本发明的第一方面的示例性实施方式中,对作为具有外延层的外延晶圆的非功能化晶圆、非结构化晶圆(意味着空白晶圆)进行检查。因此,在制造过程开始时已经可以提高显示器件的良率。

67.图7示出了外延晶圆的缺陷检查图701,将划片图式覆盖在外延晶圆上,并对良裸片709分类。外延晶圆701、704上可能的缺陷703、706可以通过检查来确定。例如,可以通过显微镜或光谱技术进行检查。在检查期间可以确定数个缺陷703、706,例如裂纹、滑移线、外延凹坑或凸起。替选地或附加地,也可以使用非破坏性电气技术。

68.作为示例,图7(a)示出了由kla circl检查工具执行的200mm的硅晶圆上的gan的缺陷检查图701。缺陷703被分类为不同类别702。为了确定良裸片709,如图7(b)中所示,将划片图式705覆盖在具有检测到的缺陷706的外延晶圆704上。作为示例,划片图式705是覆盖硅晶圆的矩形网格。在图7(c)中,划片网格705的直接位于缺陷703、706上方的部分被分类为坏裸片708,在该示例中被标记为“x”。没有“x”标记的正方形是良裸片709的位置。

69.在图8中,示出了根据本发明的第一方面的方法的另一示例性实施方式。进一步提高良裸片的良率的方法包括调整关于缺陷的划片图式以优化相对于检测到的缺陷的裸片位置从而从每个外延晶圆中产生最大数量的良裸片的步骤。换句话说,考虑外延晶圆上缺陷相对于划片图式的每个正方形或矩形的大小和位置。

70.图8示出了cmos晶圆的裸片和良外延裸片的覆盖。iii-v外延裸片区域(也称为外延裸片)的缺陷率标准在图8中用不同的区示出。裸片的质量将直接影响用其制造的器件结构,例如微型led显示器。一般而言,对于接合到cmos晶圆的重构晶圆,有源cmos区域801将大于外延裸片802以及外延裸片803和804的发射区域。801和802之间的区域考虑了所需的io以及额外的控制和计算。对于大多数应用,应避免非常大的缺陷,因为它将影响总体良率,尤其是在将重构晶圆接合到cmos晶圆期间。然而,根据应用,缺陷率标准可有所不同(例如,对于区域802、803和804不同)。

71.基于应用,可通过考虑缺陷对良率的影响将iii-v材料占据的区域(即良裸片)分段。图8中示出了iii-v外延裸片区域802的每个段的缺陷率标准。外延裸片可具有如图8的(b)所示的三个段。这些段是中心区803、中间区804和外围区805。iii-v外延裸片区域的中心区803必须具有零缺陷。围绕中心区803的中间区804可具有少量缺陷,尤其是对于近眼显示。这是因为眼睛的分辨率在中心处更好,并朝视野外下降。

72.最后,围绕中间区的外围区805是非发射排除区,与中间区804相比,其可以容忍更大数量的缺陷。因此,任何可接受的不均匀性或具有微小缺陷的可接受良裸片都可以远离发射区域(中心区和中间区)放置。因此,缺陷率标准允许具有零缺陷的良裸片以及另外的一些良裸片包含可接受的缺陷。覆盖划片图式使得可以获得零缺陷的良裸片、缺陷在300nm至500nm范围内的良裸片、缺陷在500nm至5μm范围内的良裸片。尽管优选具有零缺陷的良裸片,但具有可接受缺陷的良裸片仍可以用于外延裸片区域。由于缺陷率标准为缺陷留出了空间,因此可以优化良裸片相对于检测到的缺陷的位置,以从外延晶圆产生最大数量的良裸片。因此,使用较不完美的衬底(例如蓝宝石)仍然会是经济的。

73.在图9中,示出了根据本发明的第一方面的方法的第三示例性实施方式。作为示例,分别在图9(a)至(c)中示出了覆盖在外延晶圆901上的不同划片图式902、905、908。

74.图9(a)示出了具有规则矩形网格902的标准非优化划片图式902。覆盖检测到的缺陷的裸片标记有“x”904。优化划片图式可以提高良裸片的良率。例如,图9(a)示出了三个坏裸片。

75.优选地,缺陷率标准可用于优化划片图式。图9(b)示出了通过满足缺陷率标准将缺陷放置在裸片的边缘906处的方式优化的矩形划片网格。在图9(b)中,尽管裸片906覆盖两个缺陷,但仍然可以将其归类为良裸片,这是因为缺陷将位于可以容忍更高缺陷的外围区805上。这导致图9(b)中只有一个坏裸片904,而对于相似的矩形网格,标准方法将产生三个坏裸片。即使不允许有缺陷,图9(b)也只有两个坏裸片,仍然比图9(a)中使用的划片图式更好。因此,优化划片图式提高良裸片的良率,甚至对于相同图式也是如此。

76.此外,任何已知的划片技术(例如,锯、高功率激光器或等离子体)可以用于将图9(a)和图9(b)的矩形划片网格划片。由于锯划片非常经济,因此这种简单的方法有一些优点。

77.作为增加良裸片903的数量的另一实施方式,关于缺陷906定制划片图式908,以优化裸片相对于检测到的缺陷的位置,从而从外延晶圆901产生最大数量的良裸片903。这必然导致不规则的划片图式。不规则划片图式908优选地如图9(c)中所示逐裸片数字地定义。有利地,在定制划片图式的同时考虑缺陷率标准。

78.用于任何不规则图式的划片技术优选为等离子划片或激光划片。不规则图式的优点是可以避免裸片上的缺陷,但良率仍然是足够的。

79.根据本发明的第二方面,提供了一种生产用于晶圆重构的裸片的系统。这如图10所示。系统1001包括使用检查装置1003的处理装置1002,该处理装置1002被配置为使用检查装置1003检查外延晶圆1004以检测一个或多个缺陷1005。处理装置1002还被配置为在外延晶圆1004的检测到的缺陷1005上覆盖划片图式1012。在该情况中,处理装置1002被配置为将裸片分类为良裸片1009或坏裸片1008。处理装置1002还被配置为通过划片装置1006将良裸片划片。良裸片1009通过操作装置1010转移到载体晶圆1013或目标晶圆,以形成重构

晶圆1100。可选地,在划片后,可以重复良裸片验证。

80.优选地,处理装置1002还被配置为自学习以检测缺陷1005,覆盖合适的划片图式,将裸片分类为良裸片1009或坏裸片1008,和/或将良裸片1009划片。由此,良裸片1009的生产可以自动化。

81.作为本发明的第二方面的另一实施方式,处理装置1002被配置为将缺陷率图存储在存储器1007中。当最终显示器件在颜色、纹理、分辨率、发射率、使用寿命等方面不满足标准要求时,保存的缺陷率图可以用于识别外延晶圆1004上的任何缺陷是否作为可接受而通过了、但随后显著影响显示。由此,处理装置1002可以自学习以改进缺陷检测和/或良裸片1009和/或坏裸片1008的选择。因此,处理装置1002可以自学习以分类也能够在显示器件中表现良好的良裸片。

82.根据本发明第三方面的示例性实施方式在图11中示出。在对外延晶圆上的划片图式优化之后,将外延晶圆划片以获得良裸片1101。这里讨论了两种不同的方法来将良裸片转移到(最终)目标晶圆。

83.根据第一种方法,将良裸片转移到临时载体晶圆上,并通过临时接合方法接合1102。载体晶圆可以具有与外延晶圆不同的晶圆大小。许多不同的集成方法可以用于载体晶圆,例如拾取良裸片并将其放置在载体晶圆上。良裸片通过临时接合而接合到载体晶圆。临时接合材料将良裸片保持在载体晶圆上。将载体晶圆上的所有裸片集体转移到目标(最终)晶圆1103。如步骤1104中所述,将所有良裸片通过诸如sicn、sio2的接合膜永久性地接合到目标晶圆。将载体晶圆解接合1105。良裸片与目标晶圆的永久性接合可以是熔合接合、阳极接合、介电接合、金属接合或混合接合。

84.根据第二种方法,将良裸片直接转移到目标晶圆1106。将良裸片通过方法(a)中的任何永久性接合方法接合到目标晶圆1107。

85.根据这些方法中的任一者,全部或部分地移除外延晶圆的衬底材料1108。外延晶圆的衬底材料的移除可以在不同阶段进行,例如在划片之前、划片期间、当裸片在载体晶圆上时、或当裸片在目标晶圆上时。衬底移除方法可以是机械研磨、湿法蚀刻、干法蚀刻或其组合。最后,在通过上述形成重构晶圆的方法中的任何一者将良裸片置于目标晶圆上之后,填充良裸片之间的间隙并将其平面化1109。该重构晶圆可以随后接合到另一晶圆,例如cmos晶圆。

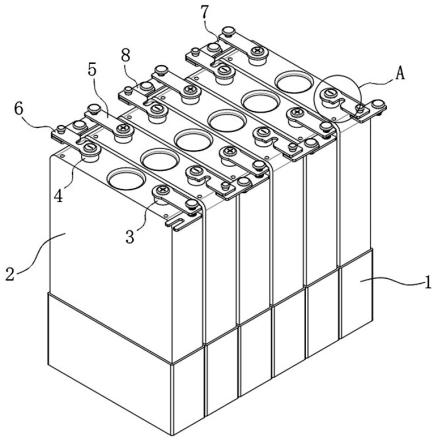

86.根据本发明的第三方面的示例性实施方式在图12中示出。示出了使用目标晶圆生产重构晶圆的方法路径。重构晶圆1200包括由外延晶圆1004(如图10所示)形成并通过图10所示的操作装置1010转移到目标晶圆1205的良裸片1201。因此,通过图10中所示的接合装置1011将良裸片1201通过接合层1204接合到目标晶圆1205。例如,接合层1204可以是良裸片1201和/或目标晶圆1205上的sicn层或sio2层。

87.图12(a)示出了具有两个选择的良裸片1201的目标晶圆1205。良裸片1201的衬底1202通过适当的方法被移除以在该阶段暴露外延层,或者可以在不同阶段被移除。图12(b)示出了用填料1206填充并平面化以形成分布在目标晶圆上的多个无缺陷外延层的这些良裸片1201之间的间隙的示意图。图12(c)示出了平面化的重构晶圆1207。因此,平面化的重构晶圆1207具有分布在目标晶圆1205上的准备与另一晶圆(例如cmos晶圆)一起使用的无缺陷良裸片1201。

88.例如,外延晶圆是150mm至200mm的硅晶圆或蓝宝石晶圆,目标晶圆是300mm的硅晶圆。优选地,填充间隙的填料为sio2或任何其他合适的介电材料。

89.在图13中,示出了从外延晶圆开始形成微型led显示器的集成技术的概述。该概述示出了根据本发明的重构晶圆的制造、通过晶圆间转移将重构晶圆转移到cmos晶圆上、以及制造微型led显示器。

90.图13(a)示出了外延晶圆1004和载体晶圆1205。通过本发明的方法,由外延晶圆1004产生最大数量的良裸片。这些良裸片被转移到目标晶圆1205上。如图13(b)所示,良裸片布置在目标晶圆1205上。填充并平面化良裸片之间的间隙,以提供如图13(c)所示的平面化的重构晶圆1207。

91.图13(d)至(f)中显示的进一步的方法步骤示出了使用本发明的平面化的重构晶圆1207制造微型led显示器。

92.有利地,平面化的重构晶圆1207允许使用晶圆间的混合接合。晶圆间的接合所需的精度可以通过本发明的重构晶圆1207实现。如图13(d)所示,将重构晶圆1207接合到cmos晶圆1301。例如,cmos晶圆1301是300mm的cmos晶圆。此外,优选地,接合是介电接合或金属间接合或混合接合。图13(e)中示出了在cmos晶圆上的具有晶圆间接合的led阵列的微型led显示器1302。最后,执行划片、包装和测试的步骤以实现如图13(f)所示的显示器件1303。

93.尽管已经关于一个或多个实现方式对本发明进行了说明和描述,但是在阅读和理解本说明书和附图之后,本领域的其他技术人员将想到等效的改变和修改。此外,虽然本发明的特定特征可能关于多个实现方式中的仅一者公开,但该特征可以与其他实现方式的一个或多个其他特征组合,这对于任何给定的或特定的应用是期望的和有利的。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。