1.本发明涉及直写光刻机领域,具体涉及一种用于直写光刻机的纠偏对位方法。

背景技术:

2.随着半导体芯片尺寸缩小,半导体显示miniled向microled的技术发展,由于功能密度提升以及互联长度缩短,对芯片封装贴片精度要求越来越高,当前最高仅3~5um。如果对贴片精度的要求过高,会导致产能的减少;如果贴片精度过低,则会导致功能失效。

3.本发明提供一种用于直写光刻机的纠偏对位方法,解决芯片贴片精度和产能的难以兼容以及贴片精度瓶颈问题。

技术实现要素:

4.为解决上述技术问题,本发明提供一种用于直写光刻机的纠偏对位方法。

5.为解决上述技术问题,本发明采用如下技术方案:

6.一种用于直写光刻机曝光工序的纠偏对位方法,

7.其中曝光工序包括第一曝光工序和第二曝光工序;在第一曝光工序中介质层与芯片层对准,需要满足条件一:介质层图案与芯片层图案的最大套刻圆心距d1<je1;在第二曝光工序中线路层与介质层对准,需要满足条件二:线路层图案与介质层图案的最大套刻圆心距d2<je2;第二曝光工序中,线路层图案仅发生刚性变换;je1、je2均为设定的阈值;{die1,die2,

…

dien}为n个需要互联的芯片,每个芯片上存在m个对位点;

8.纠偏对位方法包括以下步骤:

9.步骤一:测量每个芯片上m个对位点的坐标,计算得到各芯片的中心坐标以及贴片导致的角度误差;

10.步骤二:对各芯片对应的介质层进行分区刚性变换:根据各芯片的中心坐标以及角度误差,计算各芯片对应的介质层分区刚性变换参数,介质层分区刚性变换参数包括旋转角度、平移向量;

11.步骤三:持续修正各芯片对应介质层分区刚性变换参数,直至在第一曝光工序中满足条件一;

12.步骤四:对各芯片对应的线路层进行全局刚性变换:计算线路层全局刚性变换参数,如果线路层全局刚性变换参数能够使第二曝光工序满足条件二,则完成介质层纠偏,对介质层进行曝光;线路层全局刚性变换参数包括旋转角度、平移向量。

13.其中,对介质层进行分区刚性变换是指各芯片对应的介质层采用各自独立的刚性变换参数;对线路层进行全局刚性变换是指各芯片对应的线路层采用相同的刚性变换参数。

14.具体地,本发明中需要互联的芯片共有两个,每个芯片上存在四个对位点,对位点的坐标即对位点实际chuck(控制移动载台)坐标。

15.具体地,阈值je1根据介质层图案的套刻精度设置;阈值je2根据线路层的套刻精

度设置。

16.与现有技术相比,本发明的有益技术效果是:

17.在传统掩膜光刻机制程中,掩膜板图形结构一旦确定便不能够再实时调整更改,应用本纠偏算法的直写光刻机发挥出了一定的优势,可以降低贴片精度的方式提高产能,通过介质层对芯片贴片时产生的偏移量进行纠偏,对芯片贴片精度的要求更宽,同时不影响生产良率,确保芯片功能正常,可解决高精度贴片机产能的问题。

附图说明

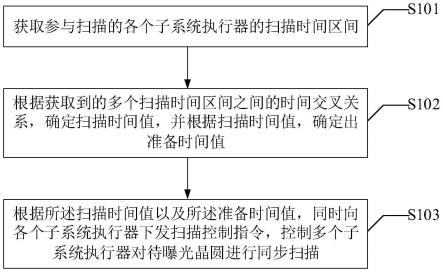

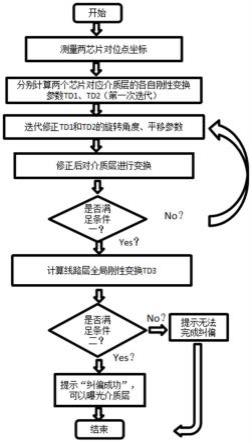

18.图1为本发明纠偏对位方法的流程图;

19.图2为本发明实施例中两个芯片的二维纠偏示意图;

20.图3为曝光工序中介质层图案与芯片层图案套刻圆心距、介质层图案与线路层图案套刻圆心距的示意图;

21.图4为本发明实施例中的容忍度制约曲线图;

22.图5为本发明两个芯片的理论相对位置示意图;

23.图6为本发明两个芯片贴片后的实际相对位置示意图;

24.图7为本发明第一次迭代后介质层的理论相对位置示意图;

25.图8为本发明介质层纠偏迭代的示意图。

具体实施方式

26.下面结合附图对本发明的一种优选实施方式作详细的说明。

27.如图3所示,在micro led封装工艺过程中,会在贴片完成后,使用光刻机曝光介质层,经过一系列工艺过程后,继续曝光线路层。在两次曝光工序中,需要满足的基本条件通常为:

28.1)条件一:第一曝光工序中,介质层与芯片层对准,需满足介质层图案与芯片层图案套刻足够精确,最差情况为相切,则经过第一曝光工序后,介质层图案与芯片层图案最大套刻圆心距d1需小于阈值je1。

29.2)条件二:第二曝光工序:线路层与介质层对准,同样需要满足线路层图案与介质层图案套刻精度要求,最差情况为相切,则经过第二曝光工序后,线路层图案与介质层图案最大套刻圆心距d2需小于阈值je2。

30.3)条件三:线路层图案在第二曝光工序过程中,不能发生涨缩,必须为刚性变换(即只能进行旋转、平移)。

31.本发明提及的刚性变换的具体表达形式使用如下矩阵运算表示:

[0032][0033]

其中,x’、y’为变换后的chuck坐标,x、y为图形资料理论坐标,θ为旋转角度,tx、ty为平移。

[0034]

本发明中的纠偏对位方法通过介质层的纠偏,使上述三个条件同时满足。

[0035]

本发明中,如果各芯片对应的各层资料(介质层、线路层)采用相同的变换参数,则定义为全局变换;如果各芯片对应的各层资料采用各自独立的变换参数,则定义为分区变

换。

[0036]

以两个需要互联的芯片举例,介绍本发明中纠偏对位方法的原理,两个芯片分别为die1、die2,

[0037]

假设die1和die2在x方向的理论距离为l0,在y方向距离为0。相对位置关系示意如图5。

[0038]

由于贴片误差,导致两die实际相对位置关系偏离理论,实际的贴片情况可能会如图6。由于贴片误差,die1实际角度相对于理论位置逆时针旋转eθ1,die2实际角度相对于理论位置顺时针旋转eθ2。图中轴aa’所示方向为两芯片角度均值方向(注:不是坐标系中的y方向)。l为两个芯片中心点连线长度,其在均值角度方向的投影长度为lh,在与均值角度方向垂直的方向上的投影长度为lw。

[0039]

在传统掩膜光刻机曝光工序中,由于上述贴片误差,导致套刻结果超出指标,芯片功能失效。在直写光刻机中,介质层通过纠偏可完美解决该问题。

[0040]

根据上述已知量,可求出两芯片介质层理论图形资料(gds坐标)各自的初始刚性变换参数(分区变换,仅包含旋转和平移)。变换输入为介质层理论gds坐标,变换输出为两个芯片介质层需要曝光的理论chuck(控制移动载台)坐标。初次迭代应将两芯片介质层曝光至理论相对位置关系上,如图7。第一次迭代后的理论介质层chuck坐标应满足理想的相对位置关系。具体地角度方面,两个芯片介质层图案此时平行,且沿两芯片贴片角度误差均值方向(aa’,并不是y方向)。距离方面,两图案在aa’方向上相距0,在与aa’垂直方向上相距l0。

[0041]

显然,如果经过第一次迭代后即满足条件一,则在第二曝光工序(线路层对介质层,全局变换)中,由于介质层图案为理想的位置关系,第二曝光工序将会完美套刻(不考虑平台自身套刻误差)。然而,实际生产过程中,第一次迭代通常会使条件一不满足。为此,该专利提及的纠偏对位方法提供一种迭代方法,该迭代方法使当条件一成立时,条件二所述的理论套刻误差一定最小。如果此时条件二不成立,则表示无法完成纠偏操作。反之,则纠偏成功。第二曝光工序中应使用全局刚性变换以确保线路层图案不会发生涨缩变形。两曝光工序的理论精度限制由阈值条件je1及je2决定。图8展示了介质层纠偏过程中第一次迭代后位置、迭代完成后最终位置、芯片实际贴片位置。

[0042]

下面阐述迭代方法。

[0043]

当第一次迭代后条件一不成立时,则将第一次迭代后两个介质层图案分别向die1、die2的实际贴片位置上逼近。通过逐次逼近,一定存在某次迭代后可使介质层图案与芯片层套刻结果恰好满足条件一。首先设置角度迭代步长δθ,可计算出介质层图案由理论位置关系迭代至实际贴片位置关系时所需迭代次数n,

[0044]

n=θ0/δθ;

[0045]

θ0为角度迭代总量。根据该迭代次数进一步计算lw及lh的迭代步长

[0046]

δlw=(lw-l0)/n;

[0047]

δlh=lh/n;

[0048]

当角度位移迭代满足上述关系时,可保证该纠偏对位方法一定有解。需要特别注意的是,介质层图案迭代(介质层进行分区刚性变换)时,两个芯片对应的介质层图形部分朝着实际贴片位置关系方向迭代(迭代量符号相反,大小相等)。另外,在每次迭代计算介质

层理论chuck坐标时,先计算角度,然后计算位移(矢量)。

[0049]

本实施例中,每个芯片具有4个对位点,图2中只画出了die1的某个对位点的纠偏状态。如图1所示,纠偏对位方法的实现步骤详细描述如下:

[0050]

1)首先测量die1及die2的8个对位点的实际chuck(控制移动载台)坐标;

[0051]

2)计算得到两个芯片的中心坐标,以及各自因贴片导致的角度误差;

[0052]

3)根据上述参数,初始化两个芯片的介质层分区刚性变换参数(td1、td2):旋转角度、x向和y向的位移;

[0053]

4)不断迭代两个芯片对应介质层的分区刚性变换参数,以满足条件一;

[0054]

5)当满足条件一时,计算线路层全局刚性变换参数td3,判断线路层理论曝光结果是否满足条件二;

[0055]

6)当条件二不满足时,提示“介质层纠偏失败”,否则,提示“介质层纠偏成功”,并可以曝光介质层。

[0056]

实际纠偏时,视介质层与线路层的套刻精度要求,合理设置阈值je1、je2。

[0057]

下表为两个芯片的实际贴片误差:

[0058]

误差项die1die2x方向误差ex/um9.521.8y方向误差ey/um-1-18角度误差eth/度0.01430.0215

[0059]

设置阈值je1=je2=7.5um,应用本发明中的纠偏对位方法后,介质层最大套刻误差为7.48um,线路层最大套刻误差为6.74um,此处忽略机台自身套刻误差。可见,使用本发明中的纠偏对位方法后,对贴片误差的容忍度大幅度提高。

[0060]

当给定角度误差时,ex及ey的容忍度相互制约,图4给出了两个芯片角度误差分别为0.03度和-0.03度时,x向和y向的位移误差的容忍度制约曲线。

[0061]

对于本领域技术人员而言,显然本发明不限于上述示范性实施例的细节,而且在不背离本发明的精神或基本特征的情况下,能够以其他的具体形式实现本发明。因此无论从哪一点来看,均应将实施例看作是示范性的,而且是非限制性的,本发明的范围由所附权利要求而不是上述说明限定,因此旨在将落在权利要求的等同要件的含义和范围内的所有变化囊括在本发明内,不应将权利要求中的任何附图标记视为限制所涉及的权利要求。

[0062]

此外,应当理解,虽然本说明书按照实施方式加以描述,但并非每个实施方式仅包含一个独立技术方案,说明书的这种叙述方式仅仅是为了清楚起见,本领域技术人员应当将说明书作为一个整体,各实施例中的技术方案也可以经适当组合,形成本领域技术人员可以理解的其他实施方式。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。