1.本技术涉及半导体制造领域,具体涉及一种形成图案的方法。

背景技术:

2.随着半导体存储器上目标图案变得越来越小,euv光刻技术和侧墙辅助图案(spacer assisted patterning)技术越来越被应用到半导体装置的制造领域,但是考虑到euv光刻技术的设备价格以及工艺不够成熟的问题,通常采用侧墙辅助自对准双重图案(spacer assisted double patterning,简称sadp)、四重图案技术(quadruplepatterning),具体的来说,sadp工艺一般包括曝光-刻蚀-侧墙沉积-去除心轴层-刻蚀(litho-etch-spacer depo-mandrel removal-etch)的步骤,这样可以在晶圆上做出更小的图案。随着图形尺寸的进一步减小,双重图形已经无法满足需求,出现了四重图案技术(quad patterning),但其制造工艺难度较高。

技术实现要素:

3.本技术至少在一定程度上解决相关技术中的上述技术问题。为此,本技术提出一种形成图案的方法,以制造出尺寸更小的图案。

4.为了实现上述目的,本技术第一方面提供了一种形成图案的方法,包括以下步骤:

5.在半导体衬底上依次形成目标层、转印层以及第一引导图案;

6.使用定向自组装工艺在所述第一引导图案上形成沿水平方向或者垂直方向排布的第一刻蚀图案,以所述第一刻蚀图案为掩模,刻蚀转印层,以形成第一转印图案;

7.形成与所述第一转印图案垂直相交的第二转印图案;

8.以所述第一转印图案、第二转印图案为掩模,刻蚀目标层以形成目标图案。

附图说明

9.通过阅读下文优选实施方式的详细描述,各种其他的优点和益处对于本领域普通技术人员将变得清楚明了。附图仅用于示出优选实施方式的目的,而并不认为是对本技术的限制。而且在整个附图中,用相同的参考符号表示相同的部件。在附图中:

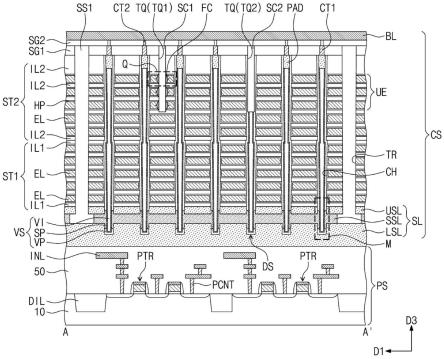

10.图1示出了在半导体衬底的目标层上沉积形成第一引导图案后的结构示意图;

11.图2示出了在图1沉积形成定向自组装材料层后的结构示意图;

12.图3示出了在图2上去除不需要的线状图案后的结构示意图;

13.图4示出了在图3上形成一种第一转印图案、第二转印图案后的结构示意图;

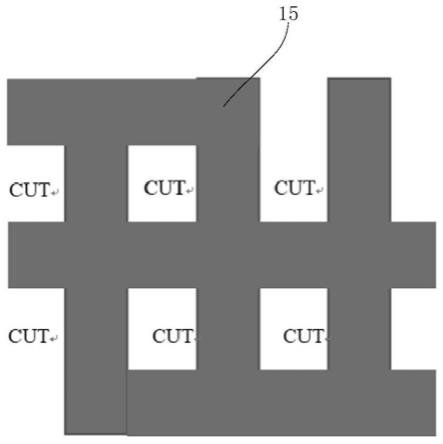

14.图5示出了在图4的基础上,形成目标图案后的结构示意图;

15.图6示出了在图3上形成另外一种第一转印图案、第二转印图案后的结构示意图;

16.图7示出了在图6的基础上,形成目标图案后的结构示意图。

具体实施方式

17.以下,将参照附图来描述本公开的实施例。但是应该理解,这些描述只是示例性的,而并非要限制本公开的范围。此外,在以下说明中,省略了对公知结构和技术的描述,以避免不必要地混淆本公开的概念。

18.在附图中示出了根据本公开实施例的各种结构示意图。这些图并非是按比例绘制的,其中为了清楚表达的目的,放大了某些细节,并且可能省略了某些细节。图中所示出的各种区域、层的形状以及它们之间的相对大小、位置关系仅是示例性的,实际中可能由于制造公差或技术限制而有所偏差,并且本领域技术人员根据实际所需可以另外设计具有不同形状、大小、相对位置的区域/层。

19.在本公开的上下文中,当将一层/元件称作位于另一层/元件“上”时,该层/元件可以直接位于该另一层/元件上,或者它们之间可以存在居中层/元件。另外,如果在一种朝向中一层/元件位于另一层/元件“上”,那么当调转朝向时,该层/元件可以位于该另一层/元件“下”。

20.本技术的实施例提供了一种形成图案的方法,具体包括以下步骤:

21.如图1所示,通过现有的侧墙辅助自对准双重图案(spacer assisted double patterning,简称sadp)工艺在半导体衬底形成氮化硅目标层以及氧化硅转印层10,然后在转印层10上采用正显影技术(positive tone development,简称ptd)形成第一引导图案11,具体地,第一引导图案11沿着水平方向进行排布,其中,第一引导图案11包括间隔设置的钉扎区域110(pinning stripe)以及中性区域111(neutral stripe),其中,钉扎区域110的宽度为30nm,中性区域111的宽度为90nm。

22.如图2所示,在第一引导图案11上形成定向自组装材料层(directed self-assembly of block copolymer lithography,简称dsa),对其进行加热后,定向自组装材料层进行自组装以形成重复排列的嵌段共聚物图案12,具体地,嵌段共聚物图案12包括若干个彼此平行的线状图案,每个线状图案的宽度为30nm;

23.如图3所示,去除不需要的线状图案(selective removal),形成沿水平方向排布的第一刻蚀图案120,保留后的线状图案彼此之间具有间隙,其中,间隙的宽度为30nm;

24.接着,以第一刻蚀图案120为掩模,刻蚀转印层10(imaging etch),以形成沿水平方形排布的第一转印图案13,去除掉第一刻蚀图案120以及第一引导图案11;

25.接着,如图4所示,在浸液式光刻工艺(arfimm)中采用负显影技术(negative tone development,简称ntd)形成与第一转印图案13垂直相交的第二转印图案14,其中,第二转印图案14包括矩形图案,其中,至少一个矩形图案的长度为30nm,宽度为90nm;

26.接着,如图5所示,以第一转印图案13、第二转印图案14为掩模,选择性刻蚀氮化硅目标层以形成目标图案15,最后去除掉光刻胶以及第一转印图案13、第二转印图案14,即得到如图5所示的目标图案15。

27.值得一提的是,目标图案15的间隙小于40nm,优选地,目标图案15的间隙小于30nm。

28.需要说明的是,形成第二转印图案14的方法不仅局限于上述步骤,还可以包括以下步骤:采用正显影技术ptd形成第二引导图案,使用定向自组装工艺以及负显影技术形成第二转印图案14,该步骤中的第二引导图案以及定向组装工艺可以参照前述步骤,如图6-7

所示,通过该方法形成的目标图案15可以包括若干个方形(square type)间隙,其中,该方形间隙的长度、宽度为30nm。

29.与现有技术相比,本技术实施例将dsa、ptd以及ntd技术进行结合应用到图像形成过程中,使得形成的图像尺寸更小,且减少了工艺步骤,提高了工艺效率。

30.本实施例中形成的图像可应用到诸如dram装置、sram装置的易失性存储器装置或者诸如flash装置、pram装置、mram装置、rram装置的非易失性存储器装置等。

31.进一步地,具有上述半导体装置可以用于各种电子设备中,具体地,该电子设备可以是智能电话、计算机、平板电脑、可穿戴智能设备、人工智能设备、移动电源等。

32.在以上的描述中,对于各层的构图、刻蚀等技术细节并没有做出详细的说明。但是本领域技术人员应当理解,可以通过各种技术手段,来形成所需形状的层、区域等。另外,为了形成同一结构,本领域技术人员还可以设计出与以上描述的方法并不完全相同的方法。另外,尽管在以上分别描述了各实施例,但是这并不意味着各个实施例中的措施不能有利地结合使用。

33.以上对本公开的实施例进行了描述。但是,这些实施例仅仅是为了说明的目的,而并非为了限制本公开的范围。本公开的范围由所附权利要求及其等价物限定。不脱离本公开的范围,本领域技术人员可以做出多种替代和修改,这些替代和修改都应落在本公开的范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。