利用划割道图案来减少缺陷的集成电路

背景技术:

1.半导体集成电路(ic)是使用光刻技术在通常称为晶片的薄半导体圆盘上制作。其中形成大部分电路的晶片的一侧通常称为装置侧或顶部侧,且相对侧通常称为背侧或底部侧。当在半导体晶片上形成集成电路时,集成电路之间的空间将ic分隔成若干个别单元或裸片。那些空间称作晶片划割道。在于半导体晶片上制作集成电路期间执行的光刻技术使用形成于玻璃或通常称为光掩模(或掩模,或者光罩)的其它透明板上的光刻图案。

2.在光刻处理中,在半导体晶片上方形成光致抗蚀剂层。此层是由光敏材料形成,这意味着光致抗蚀剂层在被特定光波长(例如,190nm)照射时改变其特性。光致抗蚀剂层用于控制经受例如蚀刻、植入或氧化物形成等的后续步骤的特定晶片区域。然后定位光掩模,且使用光来将光掩模的图案转印到光致抗蚀剂上。然后对经曝光的光致抗蚀剂(取决于化学组成,光致抗蚀剂可为正性或负性抗蚀剂)进行化学显影,且取决于光掩模的图案而移除或不移除光致抗蚀剂的区域。

技术实现要素:

3.在实例中,一种制造集成电路的方法包括将光掩模定位于光源与半导体晶片之间,所述半导体晶片在所述晶片的晶片划割道中具有光致抗蚀剂层,其中所述光掩模包括:第一掩模划割道图案;第二掩模划割道图案,其匹配所述第一掩模划割道图案;及所述集成电路的至少一个电路图案,其位于所述第一与第二掩模划割道图案之间。所述方法进一步包含照明所述光掩模以在所述晶片划割道的所述光致抗蚀剂层中产生对应于所述第二掩模划割道图案的第一经曝光部分;将所述第一掩模划割道图案定位于所述光源与所述第一经曝光部分之间;及照明所述光掩模,其中所述第一掩模划割道图案大体上屏蔽所述晶片划割道的所述光致抗蚀剂层的未曝光部分以免于曝光。

4.在实例中,一种集成电路包括:多个虚拟金属结构,每一虚拟金属结构位于同一二维网格的晶格点处周围;及裸片,其上在电路区域中形成有电路,所述电路区域位于所述二维网格内,使得所述电路区域在第一侧上由包含所述虚拟金属结构的第一子组的第一晶片划割道部分定界,且所述电路区域在第二侧上由包含所述虚拟金属结构的第二子组的第二晶片划割道部分定界。

附图说明

5.为详细说明各种实例,现在将参考附图,其中:

6.图1描绘在一些实例中说明性半导体晶片的俯视图。

7.图2描绘在一些实例中半导体晶片的一对曝光区(shot)的俯视图。

8.图3描绘在一些实例中光掩模的俯视图。

9.图4描绘在一些实例中半导体晶片的一对曝光区的俯视图。

10.图5描绘在一些实例中半导体晶片的一对曝光区的俯视图。

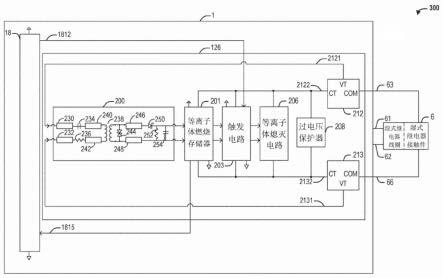

11.图6描绘在一些实例中使用本文中所描述的技术制造的集成电路封装。

12.图7描绘在一些实例中使用本文中所描述的技术制造的集成电路封装。

13.图8及9描绘在一些实例中用于制造集成电路封装的方法的流程图。

具体实施方式

14.在光掩模图案与晶片图案之间具有一一对应性的标准1:1掩模对准器已被使用减缩光学技术的步进器及扫描仪取代。在步进器及扫描仪中,将光掩模图案投影到存在于晶片表面上的光致抗蚀剂上且按例如四倍或五倍的减缩因数缩小。在步进器中使半导体晶片重复地从位置向位置“步进”直到达成半导体晶片的最大表面覆盖。在每一步进实例处,使晶片的不同曝光区(即,裸片群组)与掩模对准且曝光。以此方式重复地使晶片曝光且利用具有不同掩模图案的掩模来处理,从而在晶片的每一裸片上形成电路系统的多个层。在芯片中的每一者中制作各种组件通常以特定次序使用多于十二个掩模,每一掩模含有被转印到光致抗蚀剂的图案,光致抗蚀剂经显影以在晶片上形成所要图案序列。

15.在形成所要电路图案之后,将晶片分隔(或单片化)成若干个别硅裸片。分隔成若干个别硅裸片通常是通过经由使用机械或激光设备穿过晶片划割道锯割半导体晶片而实现。由于半导体晶片在制作过程完成之后被分隔成若干个别硅裸片,因此晶片划割道可包含在单片化之前可具有一些瞬时益处的结构。举例来说,晶片划割道可包含用以在半导体晶片被锯割之前评估在所述晶片中/上制作的电路特征的运行状况的测试位点(例如,电功能测试垫、框架单元)。测试垫用于探测在晶片上制作的电子元件中的缺陷。框架单元用于线内监测,例如不同层之间的叠覆(例如对准)的线内监测及正制作的电子元件的尺寸的线内监测。

16.在一些情形中,晶片划割道还可包含非电功能但可赋予制造过程一些益处的其它结构,例如虚拟金属结构(也称作虚拟填充)。虚拟金属结构可为通过对存在于光致抗蚀剂下面的金属层(例如,金属互连层、顶部层级钝化层或者金属互连层或顶部层级钝化层上方另外沉积的金属层)进行图案化而形成的任意形状的金属结构。虚拟金属结构满足可改善半导体晶片中的特定区域的平面化的金属密度规范。虚拟金属结构还可帮助防止在锯割过程期间裂缝的扩展。作为术语,掩模上用于在划割道中形成例如虚拟填充等的结构的指定区域在本文中称为“掩模划割道”,且其中实际上形成结构(及用于形成结构的光致抗蚀剂曝光)的晶片的划割道在本文中称为“晶片划割道”。

17.如上文所述,掩模可包含用于同时使多个裸片上的光致抗蚀剂曝光的多个电路图案(如上文所述,多个裸片的每一此类群组称为一曝光区)。在掩模上,一或多个电路图案的群组可在第一侧上由具有与上文所描述的非功能结构(例如,虚拟填充)中的一者相关的第一图案的第一掩模划割道定界,且同一群组的电路图案可由包含覆盖图案的第二掩模划割道(与第一掩模划割道相对)定界。可为称作虚拟覆盖的长的连续区域的覆盖图案防止已经曝光的晶片划割道在晶片步进时被二次曝光。(双曝光可损坏或完全移除光致抗蚀剂或导致不可预测曝光。)在一些实例中,覆盖图案为保护经曝光第一图案免于在后续曝光中被双曝光的大的矩形金属(例如,铬)块。

18.举例来说,由于掩模的第一曝光,一或多个电路图案及存在于掩模划割道中的图案在光致抗蚀剂上留下其印痕。在第一曝光之后,步进器使晶片步进到邻近位置以进行第二曝光。步进器使晶片步进,使得掩模的覆盖图案与其中第一图案被压印/曝光的晶片划割

道对准(重叠)以防止所述晶片划割道被再次曝光,借此防止光致抗蚀剂的经曝光区域被损坏。换句话说,第二掩模划割道中的覆盖图案在第二曝光期间覆盖并保护先前曝光的图案免于在第二曝光期间被再次曝光。

19.在其中掩模位于半导体晶片的边缘附近或所述边缘处的情形中,覆盖图案可保护未曝光晶片划割道使得所述晶片划割道中的光致抗蚀剂根本不被曝光。此类情境可在晶片划割道中导致未图案化的金属层。晶片划割道中未图案化的金属层的存在可在划割/锯割晶片过程期间为破坏性的,这是因为穿过未图案化的金属层进行锯割可引起例如芯片脱落及脱层等问题。邻近于具有未图案化的金属层的划割道的裸片可被损坏且在锯割后检验期间不合格。那些裸片被认为不适合于运送到顾客,因此导致合格率损失。因此,需要克服此合格率损失问题的制作方法及装置。

20.因此,本说明描述使用减轻合格率损失问题的掩模设计制作集成电路的方法。具体来说,本说明描述使用具有以下各项的掩模:第一掩模划割道,其具有用于以特定方式使晶片划割道曝光的图案;及第二掩模划割道,其与所述第一掩模划割道相对且包括覆盖图案,例如虚拟金属特征,所述覆盖图案大体上类似于所述第一掩模划割道中的所述图案。使用此掩模设计确保第二掩模划割道中的覆盖图案的每一组件充当对由第一掩模划割道中的图案在先前曝光区曝光期间产生的光致抗蚀剂印痕的完全(或几乎完全)覆盖。使用此掩模设计在技术上是有利的,至少因为其可提高总的合格率。为了简单起见,本说明的其余部分假设半导体晶片的晶片划割道仅包含虚拟金属结构(即,虚拟填充)。在其它实例中,晶片划割道可包含不同类型的非功能位点。如此,在那些实例中,第一及第二图案两者将包含相同非功能位点的图案,使得第二掩模划割道中的覆盖图案充当对由第一掩模划割道中的图案在邻近曝光区曝光期间形成的结构的覆盖。

21.本说明中所描述的实例可在各种各样的上下文中应用。本文中所描述的特定实例是说明性的且不限制本说明的范围。

22.图1描绘在一些实例中说明性半导体晶片100的俯视图。晶片100包含在一些实例中可为硅衬底的半导体衬底。替代地,半导体衬底可包括锗、硅锗、iii-v化合物半导体材料等等。晶片100包含多个曝光区102及将曝光区102彼此分隔开的多个晶片划割道104。曝光区102中的每一者包括单个裸片,或更常见地包括裸片群组(图1中未明确描绘)。举例来说,单个曝光区102可包含2x2或3x3裸片阵列。每一曝光区102中的裸片中的每一者可具有在其上通过使用一或多个掩模执行一系列光刻及蚀刻过程形成的电路。在一些实例中,相同电路形成于曝光区102中的多个裸片中的一些或全部上,且在一些此类实例中,相同电路形成于整个晶片100上的多个裸片中的一些或全部上。(为了清晰起见,图1中未描绘形成于晶片100上的电路图案,也未描绘可存在于晶片划割道104中的任何结构元件。然而,图2中更详细地展示晶片划割道104。)如所展示,曝光区102中的一些或全部由多个晶片划割道104外接。举例来说,曝光区102可具有四个侧,四个侧中的每一者邻接不同晶片划割道104。另外,当每一曝光区102自身含有多个裸片时,这些裸片中的每一者由一组晶片划割道104外接。图1中未展示外接晶片100的所有裸片的所有晶片划割道104。而是,图1中仅展示外接曝光区102的那些晶片划割道104。因此,举例来说,从图1省略通过曝光区102(水平地或垂直地)而不外接曝光区102的晶片划割道104,以提高清晰度且促进理解。尽管晶片100的所有晶片划割道是以编号104标记,但晶片划割道104中的一些更特别地标记为104a到104e且下文参

考图2来描述。

23.图2描绘一对邻近曝光区102的详细视图。在此实例中,这些邻近曝光区标记为102a及102b。如还展示,曝光区102a、102b中的每一者含有裸片200的2x2阵列(尽管在其它实例中,可使用其它裸片阵列,例如3x3、4x4、5x5及10x10阵列)。裸片200中的每一者由多个晶片划割道104外接。图2中所展示的所有晶片划割道是以编号104标记,但外接曝光区102a、102b的晶片划割道104更特别地标记为104a到104e。

24.如上文所描述,使晶片100与掩模(展示于图3中)对准以同时使掩模上单个曝光区中的所有裸片曝光且同时使外接所述曝光区的晶片划割道曝光。然后,使晶片100步进使得掩模与邻近的曝光区(例如,紧邻的曝光区)对准且重复所述过程。图3描绘此掩模(或光罩)300。掩模300包括框架302及由多个掩模划割道304、306、308、310、312及314外接的多个裸片板311。在一些实例中,裸片板311的数目匹配每一曝光区102中的裸片200(图2)的数目。

25.掩模300包含可在每一侧上为大约15cm到20cm的玻璃(或石英)板。裸片板311及掩模划割道304、306、308、310、312及314涂覆有可具有大约100nm的厚度的薄金属层(举例来说,铬)。图案形成于所述金属层中,使得所述图案包含金属区及透明玻璃区两者。所述图案的透明玻璃区允许来自步进器/扫描仪的光通过。所述图案的金属区阻挡光透射。以此方式,使用光来将所述图案投影到裸片200及晶片划割道104(图2)上。省略裸片板311上的图案以便于解释,但展示掩模划割道中的说明性图案。具体来说,掩模300包含掩模划割道304中的图案特征316、318及320;掩模划割道306中的图案特征322及324;掩模划割道308中的图案特征326、328及330;掩模划割道310中的图案特征332及334;掩模划割道312中的图案特征318、328、336及338;以及掩模划割道314中的图案特征340及342。在一些实例中,图案特征316、318及320分别与图案特征330、328及326相同或标称上相同。类似地,图案特征332、334分别与图案特征340、342相同到标称上相同。在一些实例中,掩模划割道中的各种图案特征中的一些或全部形成虚拟填充图案。在一些实例中,图案特征远比图3中所展示更多(例如,数千个、成千上万个或数百万个)。在一些实例中,使用其它量的其它类型的图案特征。在一些实例中,掩模划割道中的图案特征中的一些或全部是相同或标称上相同的(例如,标称上相同的几何形状及/或大小,例如正方形、圆形、六边形、三角形或测量为大约0.4微米

×

2.5微米的矩形;还可使用更复杂形状,例如蝴蝶结形及人字形,且说明的范围涵盖任何及所有可能形状)。说明的范围不限于任何特定类型的掩模划割道图案特征或图案。

26.现在参考图2及3,在制造过程中,步进器/扫描仪使掩模300与晶片100的曝光区102(例如图2的曝光区102a)对准。步进器/扫描仪然后发射光,所述光通过掩模300的透明部分且到达曝光区102a上的对应光致抗蚀剂部分上。举例来说,形成于裸片板311中的每一者上的图案致使光根据所述图案使曝光区102a的对应裸片200上的光致抗蚀剂曝光。类似地,由掩模划割道304、306、308、310、312及314中的图案特征形成的图案(例如,虚拟填充图案)致使光与掩模划割道中的图案一致的使对应晶片划割道104中的光致抗蚀剂曝光。例如,与由图案特征316、318及320形成的图案一致地使晶片划割道104a中的光致抗蚀剂曝光。举例来说,以下情况也是如此:图案特征326、328及330相对于晶片划割道104b;图案特征332、334相对于晶片划割道104d;图案特征340、342相对于晶片划割道104e;以此类推。

27.图4中描绘晶片划割道104a、104b、104d及104e中的光致抗蚀剂的所产生经曝光区域。图4类似于图2,但其中虚线指示为了清晰而移除的曝光区102a、102b,且晶片划割道

104a、104b、104d及104e中的光致抗蚀剂的经曝光区域由编号400指示。图4展示在无隐含限制的情况下其中使掩模300相对于晶片表面从左向右及从上到下步进的实例。因此,已经曝光的裸片200的实例展示为具有实线,而尚待曝光的实例的位置展示为具有虚线。如所展示,划割道104中的数个划割道中的光致抗蚀剂未被曝光。举例来说,晶片划割道104c中的光致抗蚀剂未被曝光,晶片划割道104d及104e中的光致抗蚀剂的部分也未被曝光。这些光致抗蚀剂区域因掩模300与曝光区102a对准且尚未与曝光区102b(图2)对准而未被曝光。

28.在图4中所展示的晶片划割道中使光致抗蚀剂区域曝光之后,使晶片100步进使得掩模300与曝光区102b(图2)对准。举例来说,使掩模划割道304中的图案特征316、318及320分别与晶片划割道104b中的经曝光光致抗蚀剂区域406、404及402对准;使图案特征326、328及330定位于晶片划割道104c中的未曝光光致抗蚀剂上方。然后,使光通过掩模300的透明区域。因掩模划割道304中的图案特征316、318及320与经曝光光致抗蚀剂区域402、404及406对准且进一步因图案特征316、318及320与分别形成了经曝光光致抗蚀剂区域406、404及402的图案特征330、328及326(分别)相同或标称上相同,因此当在掩模300与曝光区102b对准期间使光通过所述掩模时,除了已经曝光的区域402、404及406,晶片划割道104b中的光致抗蚀剂的区域不被曝光。另外,各种晶片划割道104中的其它光致抗蚀剂区域被曝光。

29.图5展示在曝光区102b曝光之后晶片的经曝光区域。在划割道104b中,先前曝光的区域402、404及406利用相应图案特征320、318及316再次曝光且因此标记为402 412、404 410及406 408。图5还描绘形成于例如晶片划割道104c、104d及104e中的新曝光的区域500。在一些实例中,因区域402 412、404 410及406 408被双曝光,这些区域可由于就每次曝光来说掩模与晶片的对准变化而相比于区域402、412及406为不同大小(例如,更小)。在一些实例中,经双曝光区域可比经单曝光的类似区域400、500在面积上小约0.16平方微米,这反映沿垂直及水平方向

±

0.2微米的对准公差。然而,差异是,大小预期为可变的且可平均为零。

30.在晶片100上使光致抗蚀剂曝光、使晶片100步进、再次使光致抗蚀剂曝光、再次使晶片100步进以此类推的此过程继续直到到达晶片的端部。例如,当掩模300在到达晶片100的边缘之前与最后曝光区102对准时,图案特征326、328及330(图3)定位于邻近于晶片100的圆周的最后晶片划割道(例如,图1中的晶片划割道104c)中的光致抗蚀剂上方,且图案特征314、316及318与第三到最后晶片划割道中的已经曝光的光致抗蚀剂区域对准。在此对准就位的情况下,使光通过掩模300,从而使最后晶片划割道中对应于图案特征326、328及330的光致抗蚀剂区域曝光。另外,第三到最后晶片划割道中无新的光致抗蚀剂区域被曝光,这是因为图案特征316、318及320与第三到最后晶片划割道中的已经曝光的光致抗蚀剂区域对准,且因为第三到最后晶片划割道中的已经曝光的光致抗蚀剂区域是由分别与图案特征320、318及316相同或标称上相同的图案特征326、328及330形成。当曝光完成时,不进一步使最后晶片划割道曝光(例如,通过另一掩模划割道,例如图1中的掩模划割道104a)。本说明的范围不限于使晶片沿任何特定方向步进。可使晶片从左向右或从右向左、从上到下或从下到上、随机地或使用任何其它技术来步进。无论所使用的步进技术如何,本文中所描述的技术均适用。

31.由于使用此技术,晶片100上的晶片划割道中的许多晶片划割道被双曝光(其中第二曝光是以与第一曝光相同或几乎相同的方式)。这是因为每当晶片100在曝光区曝光之间

移位时,掩模划割道中的一者就用于使在最近晶片移位之前已经曝光的晶片划割道中的光致抗蚀剂二次曝光。外接曝光区102中的每一者的各种晶片划割道104(图1)均如此,除了晶片100的最外部晶片划割道104。此双曝光不会损害光致抗蚀剂或以其它方式不利地影响光刻过程,这是因为两次曝光是使用相同或标称上相同的掩模图案以相同或标称上相同的方式执行。

32.本说明的大部分假设晶片100是从右向左步进。然而,本文中所描述的掩模及技术还可适于在晶片100从左向右步进时使用。类似地,本文中所描述的掩模及技术可适于在晶片100垂直地从较低位置向较高位置或从较高位置向较低位置步进时使用。所述掩模及技术可适于在晶片沿多个(水平及垂直)方向步进时使用。

33.图6描绘使用本文中所描述的技术以及可为适合的任何额外步骤(例如,蚀刻步骤)制造的实例集成电路裸片600的内容。裸片600包括内部区602,其上形成有电路604。裸片600进一步包含邻接内部区602且包括第一多个虚拟金属结构608的第一晶片划割道部分606(例如,单片化后晶片划割道)。裸片600还包括与第一晶片划割道部分606相对的第二晶片划割道部分610,第二晶片划割道部分610邻接内部区602且包括第二多个虚拟金属结构612。第一多个虚拟金属结构608中的每一者可相比于第二多个虚拟金属结构612中的对应结构为不同大小(例如,更小)(尽管这些对应结构的形状可为相同或标称上相同的)。然而,本说明的范围包含其中虚拟金属结构608与612在测量精度内为基本上相同的大小的实例。另外,第一多个虚拟金属结构608中的每一者具有与第二多个虚拟金属结构612中的对应结构标称上相同的形状。包含于本说明的范围中的形状是无限制的,且可包含仅作为实例的正方形、矩形、三角形、人字形、蝴蝶结形、圆形等。第一多个虚拟金属结构608中的结构可与第二多个虚拟金属结构612中的对应结构为不同大小,因为第一多个虚拟金属结构608中的结构是通过双曝光形成,如上文详细地描述。曝光区之间的不对准可为例如沿垂直及水平方向

±

0.2微米。因此双曝光可致使结构大小减小例如在长度及宽度上0.4微米,因此导致说明性的大约0.16平方微米的面积减小。相比来说,第二多个虚拟金属结构612中的结构是通过单曝光例如通过使用掩模划割道306(图3)中的图案而形成。类似虚拟金属结构可在正交于晶片划割道部分606及610的晶片划割道部分中形成,如所展示。

34.图7描绘使用本文中所描述的技术以及可为适合的任何其它步骤(例如蚀刻步骤)制造的另一实例集成电路裸片700。裸片700包含内部区702,其上形成有一或多个电路704。所述一或多个电路位于裸片的电路区域中,所述电路区域排除裸片的划割道部分及可位于划割道部分中的任何测试模块或类似电路。裸片700进一步包含邻接内部区702且包括第一多个虚拟金属结构708的第一晶片划割道部分706。裸片700还包括与第一晶片划割道部分706相对的第二晶片划割道部分710,第二晶片划割道部分710邻接内部区702且包括第二多个虚拟金属结构712。裸片700进一步包含邻接内部区702且包括第三多个虚拟金属结构716的第三晶片划割道部分714。裸片700进一步包括邻接内部区702且包括第四多个虚拟金属结构720的第四晶片划割道部分718。晶片划割道部分706与710大致彼此平行,且晶片划割道部分714与718大致彼此平行。晶片划割道部分706大致正交于晶片划割道部分714及718,且晶片划割道部分710也大致正交于晶片划割道部分714及718。

35.如所展示,虚拟金属结构708、712、716及720位于二维网格722的晶格点或网格点上或周围。(网格722是用于说明性目的且除了通过虚拟填充结构708、712、716及720相对于

彼此的位置,自身未在裸片700中物理上表现。)网格722具有在裸片700区域内的起点,例如展示为左上拐角。网格722可在一或多个裸片及掩模300的划割道上方均匀地延伸。因此,至少掩模300上的周界掩模划割道304、308、310及314中的虚拟填充结构可位于同一均匀网格的晶格点处。任选地,不在周界掩模划割道中的虚拟填充结构(例如图案特征322、324、336及338)也可位于均匀网格的晶格点处。裸片700在从其晶片单片化之前可能位于邻接其中发生双曝光的晶片划割道之处,如上文详细地描述。此外,尽管网格722被描绘为矩形网格,但请考虑其它网格类型且其属于本说明的范围内,包含正方形网格、六边形网格及偏斜网格(其中所述点位于平行四边形的阵列的顶点处的网格)。此外,在一些实例中,虚拟金属结构708、712、716及720经布置使得在第一子组的虚拟金属结构沿着裸片的轴线(例如,轴线724)平移时,第一子组中的每一虚拟金属结构上覆于第二子组的对应虚拟金属结构正上方。

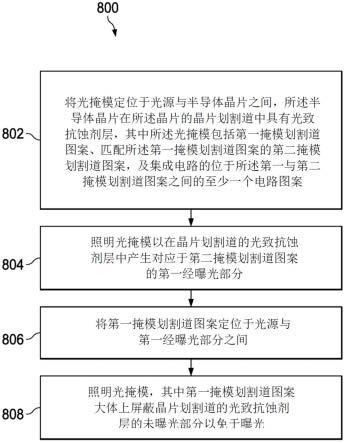

36.图8及9描绘在一些实例中用于制造集成电路裸片的方法的流程图。参考图8,方法800以将光掩模定位于光源与半导体晶片之间开始,所述半导体晶片在所述晶片的晶片划割道中具有光致抗蚀剂层(802)。所述光掩模包括第一掩模划割道图案、匹配所述第一掩模划割道图案的第二掩模划割道图案,及集成电路的位于所述第一与第二掩模划割道图案之间的至少一个电路图案。(术语“匹配”在本文中应用于掩模划割道图案时表示多个掩模划割道,所述掩模划割道中的每一者包含一或多个图案特征,所述一或多个图案特征在其余掩模划割道中存在标称上相同的大小、形状及位置的对应图案特征,其中所述位置是在叠覆多个掩模划割道的二维网格的网格点处,如本文中其它处所描述。匹配的掩模划割道图案不排除在所述掩模划割道中的一或多者中存在可屏蔽其它非虚拟填充结构以免于双曝光的特征,例如参数测试模块、对准标志等。因此,匹配的掩模划割道图案的仅部分具有彼此对应的特征是可能的。)方法800还包括照明光掩模以在晶片划割道的光致抗蚀剂层中产生对应于第二掩模划割道图案的第一经曝光部分(804)。方法800进一步包括将第一掩模划割道图案定位于光源与第一经曝光部分之间(806)。方法800还包括照明光掩模,其中第一掩模划割道图案屏蔽晶片划割道的光致抗蚀剂层的未曝光部分以免于曝光(808)。关于步骤808的动作使用的术语“大体上屏蔽”意指晶片划割道上的光致抗蚀剂层的未曝光部分的小部分区域(例如少于30%)可被曝光,例如归因于因步进机器产生的光掩模与晶片之间的不对准。通过使用术语“大体上屏蔽”而预期并计及此些小变化。

37.现在参考图9,方法900以在第一曝光期间利用第一掩模划割道图案使第一晶片划割道中的第一光致抗蚀剂部分曝光开始(902)。方法900进一步包括在第一曝光期间利用第二掩模划割道图案使第二晶片划割道中的第二光致抗蚀剂部分曝光(904)。方法900还包括在第一曝光期间利用掩模电路图案使第三光致抗蚀剂部分曝光,所述第三光致抗蚀剂部分位于第一与第二光致抗蚀剂部分之间(906)。方法900进一步包括在第二曝光期间利用第一掩模划割道图案使第二光致抗蚀剂部分曝光,使得第二光致抗蚀剂部分的在第一曝光期间曝光的区域被二次曝光且使得第二光致抗蚀剂部分的在第一曝光期间受保护而免于曝光的区域不被第二曝光曝光(908)。

38.在前述说明中及权利要求书中,术语“包含(including)”及“包括(comprising)”是以开放式方式使用,且因此意指“包含但不限于

…”

。除非另有陈述,否则数值前面的“约”、“大约”或“大体上”意指所述值的 /-10%。当两个组件“标称上相同”时,两个组件之

间的差异是可忽略的,使得所属领域的普通技术人员认为两个组件实际上相同。

39.以上说明意在说明本说明的原理及各种实施例。一旦完全了解所述说明,所属领域的技术人员便将明了众多变化及修改。所附权利要求书囊括所有此类变化及修改。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。