在凹陷特征中自底向上金属化的方法

1.通过引用并入

2.本公开内容要求于2019年9月16日提交的美国临时申请第62/900,794号的权益,该美国临时申请通过引用整体并入本文中。

技术领域

3.本公开内容涉及半导体器件的设计和微制造。

背景技术:

4.在半导体器件的制造(尤其是在微观尺度上)中,执行各种制造处理,例如成膜沉积、蚀刻掩模创建、图案化、材料蚀刻和移除以及掺杂处理。重复执行这些处理以在衬底上形成所需的半导体器件元件。从历史上看,利用微制造,已经在一个平面中创建了晶体管,其中布线/金属化形成在有源器件平面上方,因此所述晶体管已经被表征为二维(2d)电路或2d制造。缩放工作已经极大地增加了2d电路中每单位面积的晶体管的数目,但是随着缩放进入个位数纳米半导体器件制造节点,缩放工作正遇到更大的挑战。半导体器件制造商已经表达了对三维(3d)半导体电路的需求,在所述三维(3d)半导体电路中,晶体管堆叠在彼此的顶部。

技术实现要素:

5.本公开内容涉及在凹陷结构中自底向上金属化。

6.第一方面是一种金属化的方法,该方法包括:接收在其中形成有凹陷的衬底,该凹陷具有底部和侧壁;以及在凹陷的底部和侧壁上沉积共形衬里。从凹陷的上部去除共形衬里以露出凹陷的上侧壁,同时留下凹陷的下部中的共形衬里,从而覆盖凹陷的底部和下侧壁。在凹陷的下部中选择性地沉积金属以形成金属化特征,该金属化特征包括凹陷的下部中的共形衬里和金属。

7.根据第一方面,可以通过以下操作来去除共形衬里:沉积材料以覆盖凹陷的下部中的共形衬里,并且相对于覆盖凹陷的下部中的共形衬里的材料,从凹陷的上部选择性地蚀刻共形衬里。然后,沉积材料可以是:在凹陷的下部中将形成金属化特征的一部分的金属,或者在凹陷的下部中沉积将不会形成金属化特征的一部分的阻挡材料。第一方面还可以包括:利用自对准单层来表面处理凹陷的露出的上侧壁,以促进金属相对于露出的侧壁的选择性沉积。

8.根据另一方面,公开了一种处理衬底的方法,在该方法中,可以接收具有限定凹陷特征的图案化的第一层的衬底,该凹陷特征限定底部和侧壁。衬底还可以包括在第一层下方的第二层,并且第一层可以具有延伸至第二层中的凹陷特征。第二层可以是任何半导体材料例如硅,并且第一层可以是介电材料例如氧化硅。

9.该方法还可以包括:在衬底上沉积衬里膜以共形地衬在未被覆盖的表面上;执行初始金属沉积处理,该初始金属沉积处理在凹陷特征的侧壁的下部上比在凹陷特征的侧壁

的上部上沉积相对更多的金属;使初始金属沉积凹陷到凹陷特征内的预定深度,从而产生凹陷的金属沉积;以及从衬底去除衬里膜的未被覆盖的部分。

10.随后,可以在凹陷的金属沉积上选择性地沉积相同的金属材料。选择性金属沉积可以填充凹陷的金属沉积中的间隙。选择性金属沉积处理还可以通过减小凹陷的金属沉积的截面轮廓的凹度来改变截面轮廓。在一些实施方式中,减少第一层上的金属成核的自组装单层可以沉积在第一层的未被覆盖的部分上,之后是金属沉积处理,在该金属沉积处理中,金属材料可以选择性地沉积在凹陷的金属沉积上。在替选实施方式中,用作金属成核的前体的自组装单层可以沉积在凹陷的金属沉积上方,之后是金属沉积处理,在该金属沉积处理中,金属材料可以选择性地沉积在凹陷的金属沉积上。

11.此外,该方法可以包括:清洁衬底以去除非选择性地沉积在第一层的未被覆盖的部分上的金属。

12.根据第二方面,公开了一种处理衬底的方法,在该方法中,可以接收具有限定凹陷特征的图案化的第一层的衬底,该凹陷特征限定底部和侧壁。衬底还可以包括在第一层下方的第二层,并且第一层可以具有延伸至第二层中的凹陷特征。第二层可以是任何半导体材料例如硅,并且第一层可以是介电材料例如氧化硅。

13.该方法还可以包括:在衬底上沉积衬里膜以共形地衬在未被覆盖的表面上;利用填充材料填充凹陷特征;使填充材料凹陷到预定深度,其中其余填充材料覆盖衬里膜的一部分;以及从衬底去除衬里膜的未被覆盖的部分,使得其余衬里膜衬在凹陷特征的底部和侧壁的部分上。然后,可以去除其余填充材料,以使其余衬里膜未被覆盖。

14.随后,可以在其余衬里膜上方选择性地沉积金属材料。在一些实施方式中,减少第一层上的金属成核的自组装单层可以沉积在第一层的未被覆盖的部分上,之后是金属沉积处理,在该金属沉积处理中,金属材料可以选择性地沉积在其余衬里膜上。在替选实施方式中,用作金属成核的前体的自组装单层可以沉积在其余衬里膜上方,之后是金属沉积处理,在该金属沉积处理中,金属材料可以选择性地沉积在其余衬里膜上。

15.此外,该方法可以包括:清洁衬底以去除非选择性地沉积在第一层的未被覆盖的部分上的金属。

16.当然,为了清楚起见,已经呈现了如本文中所述的不同步骤的讨论顺序。通常,这些步骤可以以任何合适的顺序被执行。另外,尽管可以在本公开内容的不同位置处讨论本文中的不同特征、技术、配置等中的每一个,但是概念中的每一个旨在可以彼此独立地被执行或彼此组合地被执行。因此,本发明可以以许多不同的方式被体现和被考虑。

17.注意,本发明内容部分没有指定本公开内容或要求保护的发明的每个实施方式和/或递增的新颖性方面。相反,本发明内容仅提供了对不同实施方式的初步讨论和相对于常规技术的新颖性的相应点。对于本发明和实施方式的其他细节和/或可能的观点,读者被引导至如下面进一步讨论的本公开内容的具体实施方式部分和相应的图。

附图说明

18.当与附图一起阅读时,从以下具体实施方式最佳地理解本公开内容的各方面。应当注意的是,根据行业中的标准做法,各种特征没有按比例绘制。实际上,为了讨论的清楚,可以增加或减小各种特征的尺寸。

19.图1是根据本公开内容的实施方式的自底向上金属化过程的流程图。

20.图2a和图2b分别是根据本公开内容的示例性实施方式的具有弯月面和没有弯月面的轨道轮廓的图像。

21.图3是根据本公开内容的示例实施方式的自底向上金属化过程的流程图。

22.图4a至图4f是根据图3的示例过程的在制造的各个中间步骤处的半导体器件的示意性截面。

23.图5a、图5b和图5c是根据本公开内容的示例性实施方式的轨道轮廓随着选择性沉积时间的变化的示意性表示。

24.图6a、图6b和图6c是根据图3的示例过程形成的半导体器件的中间结构的截面图像。

25.图7是根据本公开内容的另一示例实施方式的自底向上金属化过程的流程图。

26.图8a至图8g是根据图7的示例过程的在制造的各个中间步骤处的半导体器件的示意性截面。

27.图9是作为本公开内容的示例性应用的半导体器件中的示例埋入式电源轨道的截面视图。

28.图10a、图10b和图10c是在传统轨道金属化过程的各个中间步骤处的半导体器件的截面视图。

具体实施方式

29.以下公开内容提供了用于实现所提供的主题的不同特征的许多不同实施方式或示例。下面描述了部件和布置的具体示例以简化本公开内容。当然,这些仅仅是示例,并不旨在是限制性的。例如,在以下的描述中,在第二特征上方或第二特征上形成第一特征可以包括直接接触地形成第一特征和第二特征的实施方式,并且还可以包括以下实施方式:可以在第一特征与第二特征之间形成附加特征,使得第一特征和第二特征可以不直接接触。另外,本公开内容可能在各种示例中重复附图标记和/或字母。这种重复是出于简单和清楚的目的,并且其本身不指示所讨论的各种实施方式和/或配置之间的关系。此外,为了便于描述,空间相对术语例如“顶部”、“底部”、“下”、“下面”、“下方”、“上面”、“上方”等可以在本文中用来描述如图中示出的一个要素或特征与另外的要素或特征的关系。除了图中描绘的取向之外,空间相对术语旨在包含设备在使用或操作中的不同取向。装置可以以其他方式被定向(被旋转90度或在其他取向上),并且本文中使用的空间相对描述符同样可以相应地被解释。

30.为了清楚起见,已经呈现了如本文中所述的不同步骤的讨论的顺序。通常,这些步骤可以以任何合适的顺序被执行。另外,尽管可以在本公开内容的不同位置讨论本文中的不同特征、技术、配置等中的每一个,但是概念中的每一个旨在可以彼此独立地被执行或彼此组合地被执行。因此,可以以许多不同的方式体现和考虑本发明。

31.如背景技术中所述,半导体器件制造商已经表达了对三维(3d)半导体电路的需求,在所述三维(3d)半导体电路中,晶体管堆叠在彼此的顶部。3d集成——即多个器件的竖直堆叠——旨在通过增加体积而不是面积中的晶体管密度来克服平面器件中所经历的缩放限制。虽然通过采用3d nand,已经由闪速存储器行业成功地证明和实现了器件堆叠,但

是应用于随机逻辑设计基本上更加困难。正在追求逻辑芯片(cpu(中央处理单元)、gpu(图形处理单元)、fpga(现场可编程门阵列)、soc(芯片上系统))的3d集成。

32.特别地,埋入式电源轨道是支持互补场效应晶体管(cfet)器件的启用的缩放助推器。cfet器件是三维堆叠的逻辑标准单元,在该逻辑标准单元中,nmos或pmos位于其互补物之上。埋入式电源轨道是位于晶体管平面下方的用于晶体管单元的电源轨道,而常规的电源轨道形成在fet上方以连接至标准单元。图9是作为本公开内容的示例性应用的半导体器件900中的示例埋入式电源轨道的截面视图。该视图示出了通过上晶体管的源极/漏极区域的截面以及通过下晶体管的栅极区域的截面(在不同的竖直平面中)。器件900可以用作一种新的aoi cfet标准单元。器件900可以具有多个源极/漏极区域901、栅极区域902、金属填充区域903和埋入式电源轨道905。金属填充区域903可以将源极/漏极区域901电连接至埋入式电源轨道905。通过在器件的体硅中埋入电源轨道,通过轨道高度减小实现了显著的面积缩放效益。本公开内容涉及半导体器件特征的自底向上的金属化方法,该方法可以用于制造埋入式电源轨道。

33.形成埋入式电源轨道的一种技术是在沟槽中沉积衬里并用金属覆盖层完全填充沟槽。然后,使用化学机械抛光处理来去除金属覆盖层。然后,可以执行反应离子蚀刻处理以使沟槽中的金属凹陷到所需深度。图10a、图10b和图10c是在传统轨道金属化过程的各个中间步骤处的半导体器件1000的截面视图。如图10a中所示,器件1000包括图案化的第一层1001和在图案化的第一层1001下方的第二层1002。图案化的第一层1001具有延伸至第二层1002中并限定底部1007和两个侧壁1009的凹陷特征。器件1000还可以具有衬在所有表面的衬里膜,所述所有表面包括凹陷特征的底部1007和侧壁1009以及第一层1001的顶表面1001’(由于缩放而不可见)。器件1000还包括在衬里膜上方的金属膜1005。金属膜1005可以具有一定厚度,使得金属膜1005完全填充凹陷特征的间隙并且使得金属膜1005的顶表面1005’在第一层1001的顶表面1001’之上。第二层1002是硅(并且可以是硅块体材料),并且第一层1001是硅氧化物。可以通过使用蚀刻掩模限定要蚀刻的区域的方向性蚀刻来形成凹陷特征。在所示的示例中,金属膜1005是钌,并且通过化学气相沉积或原子层沉积来沉积金属膜1005。

34.图10b示出了在化学机械平坦化(cmp)处理之后的图10a的器件1000。如所看到的,金属膜1005被平坦化成使得金属膜1005的顶表面1005’在与第一层1001的顶表面1001’相同的水平上。

35.图10c示出了在反应离子蚀刻(rie)处理之后的图10b中的器件1000。金属膜1005被蚀刻成使得金属膜1005的顶表面1005’在第一层1001的顶表面1001’下方。因此,其余的金属膜1005可以覆盖凹陷特征的底部1007和侧壁1009的部分。

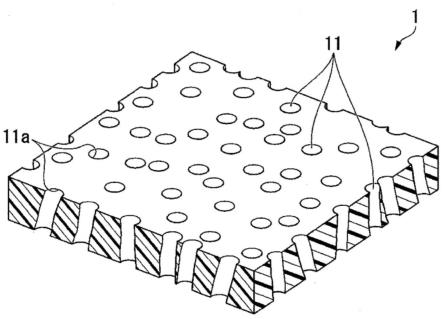

36.本发明人认识到,图10a、图10b和图10c的传统金属化过程不是优选的。例如,cmp处理可能是昂贵的并且rie蚀刻钌可能是缓慢的。本发明人进一步认识到,一种消除对cmp和长时间蚀刻的需要的方法是在自底向上的进展中使轨道金属化。特别地,本发明人认识到,自底向上沉积的优点可以解决根据如上所述的传统cmp处理的埋入式电源轨道形成中遇到的挑战中的一些。例如,形成埋入式电源轨道(或其他沟槽金属化)可能导致从轨道到轨道的高度可变性。此外,对金属轨道的顶部的轮廓控制是具有挑战性的。不能有效地解决这两个挑战可能对相应器件的电性能具有不利影响。例如,高度可变性造成电源轨道与悬

垂触点之间的变化电容,这可能破坏或延迟器件性能。此外,期望轨道的顶部具有平坦的外形。相反,如果轨道具有弯月面,则结果将是峰值处的高电场,这可能会通过静电放电(esd)而导致器件故障。另外,弯月面轮廓会加剧轨道的顶部与上方金属化层之间的距离的可变性。

37.本文中的技术提供了一种使用选择性沉积进行自底向上填充金属化的方法。本文中的技术包括去除在金属化期间沉积的衬里。通过去除衬里,然后可以在自底向上的进程中沉积金属。本文中公开的一些示例技术提供了图案化和形成埋入式电源轨道的方法,这些方法可以包括:在没有化学机械抛光的情况下沉积可以相对于介电材料被蚀刻的金属,例如钌或钴。在示例性实施方式中,底部沉重金属沉积可以凹陷,然后经由选择性沉积来完成。在一个示例实施方式中,涂覆介电材料并代替衬里材料的自组装单层将金属沉积集中在沟槽的底部和侧壁的部分内。在替选实施方式中,可以选择性地去除共形地衬在衬底上的衬里膜,以仅覆盖沟槽的底部和侧壁的部分。随后,可以执行金属沉积以在衬里材料上选择性地沉积金属。

38.图1是根据本公开内容的实施方式的自底向上金属化过程的流程图。如所看到的,方法包括以下步骤101:接收在其中形成有凹陷的衬底,该凹陷具有底部和侧壁。在步骤103中,在凹陷的底部和侧壁上沉积共形衬里。在步骤105中,从凹陷的上部去除共形衬里以露出凹陷的上侧壁,同时留下凹陷的下部中的共形衬里,从而覆盖凹陷的底部和下侧壁。根据本公开内容的实施方式,可以在沉积金属之前或之后去除共形层的部分,如下面进一步讨论的。在步骤107中,在凹陷的下部中选择性地沉积金属以形成金属化特征,该金属化特征包括在凹陷的下部中的共形衬里和金属。还如下面进一步讨论的,根据本公开内容的实施方式,可以在使用或不使用自组装单层的情况下选择性地沉积金属。

39.与需要自顶向下的蚀刻处理形成轨道的相关示例相比,可以在没有cmp的情况下执行本文中的自底向上金属化,并且本文中的自底向上金属化可以提供对金属轨道的顶部的轮廓控制并减小从轨道到轨道的高度变化。特别地,本文中的自底向上金属化可以使金属轨道的顶部平坦化以减轻与弯月面轮廓相关联的问题。

40.图2a和图2b是示出了不同的轨道轮廓的放大(tem)截面图像。如所看到的,图2a示出了在器件200a中具有弯月面的轨道轮廓,而图2b示出了在器件200b中没有弯月面的轨道轮廓。需要没有弯月面的轨道。在图2a中,器件200a可以具有图案化的第一层201和在第一层201下方的第二层202。第一层201可以具有延伸至第二层202中并限定底部207和两个侧壁209的凹陷特征。器件200a还可以包括凹陷特征中的金属膜205a,其中金属膜205a的顶表面205a’在第一层201的顶表面201’下方。金属膜205a可以覆盖凹陷特征的底部207和侧壁209的部分。在一些实施方式中,器件200a还可以在第一层301内具有第三层203。

41.由于图2b的示例实施方式类似于图2a的示例实施方式,因此将强调不同之处来给出解释。与可以具有弯月面且是凹形的图2a中的金属膜205a不同,图2b中的金属膜205b’可以具有平坦的顶表面205b’。注意,金属膜205a和205b可以用作如图9中所示的埋入式电源轨道。对于埋入式电源轨道应用,期望轨道的顶部具有平坦的外形。如所述地,相反,如果轨道具有弯月面,则结果将是峰值处的高电场,这可能通过静电放电而导致器件故障。另外,弯月面可以加剧轨道的顶部与上方金属化层之间的距离的可变性。因此,金属膜205b’对于埋入式电源轨道应用可能是所期望的。最后,应该理解的是,可以调整金属膜的顶表面

205b’的高度以满足特定的设计要求。

42.图3是根据本公开内容的实施方式的用于制造示例性半导体器件的示例性过程300的流程图。过程300开始于步骤s301,在步骤s301处,可以接收具有图案化的第一层和在第一层下方的第二层的衬底。第一层可以具有延伸至第二层中并限定底部和两个侧壁的凹陷特征。在一些实施方式中,衬底可以具有第一层以及限定底部和两个侧壁的在第一层内的凹陷特征,而没有在第一层下方的第二层。然后,过程300继续进行到步骤s302,在步骤s302处,衬里膜可以共形地沉积在衬底的未被覆盖的表面上,所述衬底的未被覆盖的表面包括凹陷特征的底部和侧壁以及第一层的顶表面。在步骤s303处,可以执行初始金属沉积,以与凹陷特征的侧壁的上部相比,在凹陷特征的侧壁的下部上沉积相对更多的金属。因此,凹陷特征的底部可以填充有金属。然后,在步骤s304处,初始金属沉积可以凹陷到凹陷特征内的预定深度,从而导致凹陷的金属沉积。因此,可以去除凹陷的侧壁的上部和第一层的顶表面处的初始金属沉积。其余的金属膜可以覆盖凹陷的底部和侧壁的下部。在步骤s305处,可以从衬底去除衬里膜的未被覆盖的部分。在步骤s306处,可以在凹陷的金属沉积上选择性地沉积相同的金属材料。可以在有或没有sam的情况下完成金属材料的选择性沉积,并且金属材料的选择性沉积还可以包括清洁步骤以去除非选择性沉积的金属。此外,可以通过调整选择性沉积时间来控制金属膜的顶表面的凹度。

43.图4a至图4f是根据图3的示例过程形成的半导体器件的中间结构的截面示意图。图4a示出了示例性半导体器件400的截面视图。器件400可以具有图案化的第一层401和在第一层401下方的第二层402。第一层401可以具有延伸至第二层402中并限定底部407和两个侧壁409的凹陷特征。第二层402可以由任何半导体材料例如硅制成,并且可以是块体硅材料。第一层401可以是介电材料,例如硅氧化物。可以通过使用蚀刻掩模限定要蚀刻的区域的方向性蚀刻来形成凹陷特征。

44.在图4b中,然后,可以在器件400中的未被覆盖的表面上共形地沉积衬里膜404,使得衬里膜404覆盖第一层401的顶表面401’、凹陷特征的底部407和侧壁409。衬里膜404可以用于成核促进/粘附,并且还可以用作材料迁移的屏障。衬里膜404可以由与第一层401不同的介电材料例如钽氮化物、钛氮化物、硅氧化物、硅氮化物和硅氮氧化物制成,并且可以通过任何技术例如原子层沉积或化学气相沉积而被沉积。

45.在图4c中,可以在一定程度上共形地在衬里膜404上初始沉积金属膜405,并且金属膜405填充凹陷特征的底部407,从而导致在凹陷的底部407和侧壁409的下部处的相对较厚的沉积以及在凹陷的侧壁409的上部和第一层401的顶表面401’处的相对较薄的沉积。例如,金属膜405可以是钌或钴,并且可以通过化学气相沉积或原子层沉积而被沉积。

46.在图4d中,然后,可以使金属膜405凹陷,从而使得去除凹陷的侧壁409的上部和第一层401的顶表面401’处的初始金属沉积。因此,其余的金属膜405可以覆盖凹陷的底部407和侧壁409的下部。此外,其余的金属膜405可以具有凹形的顶表面405’。在该示例中,金属膜405的顶表面405’可以低于第二层402的顶表面402’。当然,金属膜405的顶表面405’可以被调整成满足特定的设计要求。金属去除可以通过干法或湿法蚀刻处理来完成。例如,可以选择蚀刻剂,使得蚀刻剂仅蚀刻金属层405并且不蚀刻衬里膜404。例如,蚀刻剂可以是蚀刻钌而不蚀刻氮化硅的含有盐酸和硝酸的热溶液。替选地,基于氧气/氯气/氩气的反应离子蚀刻可以用于钌去除。在衬里膜404由氮化钛制成的实施方式中,基于氧气/氮气的反应离

子蚀刻可能导致更好的选择性。

47.在图4e中,可以通过诸如干法蚀刻或湿法蚀刻的任何技术去除衬里膜404的未被覆盖的部分。可以选择蚀刻剂,使得蚀刻剂仅蚀刻衬里膜404并且不蚀刻金属层405或第一层401。例如,蚀刻剂可以是蚀刻氮化硅但不蚀刻钌或氧化硅的热浓正磷酸溶液。在衬里膜404由氮化钛制成的上述实施方式中,可以使用sc1湿法蚀刻,上述sc1是氢氧化铵、过氧化氢和水的混合物。在衬里膜404是氮化钽的另一个实施方式中,这在钌的干法蚀刻(o2/cl2/ar)期间部分地发生,该干法蚀刻之后可以是湿法蚀刻步骤以去除任何残留物。

48.在图4f中,相同金属材料可以选择性地沉积在图4e中的其余金属膜405上,使得可以使金属膜405的顶表面405’平坦化。在一些实施方式中,通过使用自组装单层(sam)来阻挡金属沉积,可以实现金属材料的选择性沉积。可以在第一层401的未被覆盖的部分上选择性地沉积sam,使得sam可以减少或消除金属成核(未示出)。随后,可以执行金属沉积处理以在其余的金属膜405上选择性地沉积相同的金属。例如,十八烷基三氯硅烷(odts)sam可以选择性地沉积在氮化硅或氧化硅上并防止金属成核。其他常见的表面改性剂包括但不限于:烷硫醇(例如,ddt:十二烷硫醇)、烷基硅烷(例如,odts:十八烷基三氯硅烷)、烷基膦酸(例如,odpa:十八烷基膦酸)、碳氟化合物(例如,pfots:全氟辛基三氯硅烷)和硅氮烷(例如,hmds:六甲基二硅氮烷和tmsdma:三甲基硅烷二甲胺)。

49.图5a、图5b和图5c示出了根据本公开内容的示例性实施方式的轨道轮廓随着选择性沉积时间的变化。图5a示出了与图4e和图4f之间的中间状态相对应的示例性器件500的截面视图。器件500可以具有第一层501以及限定了底部507和两个侧壁509的在第一层501中的凹陷。器件500还可以具有涂覆凹陷的底部507和侧壁509的部分的衬里膜504。器件500还可以包括覆盖衬里膜504的金属膜505。金属膜505可以具有第一层501的顶表面501’下方的凹形顶表面505’。第一层501可以是氧化硅,并且金属膜505可以是钌或钴。虽然在该示例中,第一层501被示出为单个层,但是在一些实施方式中,第一层501可以是由硅上方的氧化硅制成的双层结构,类似于图4e和图4f。

50.图5b示出了在增加选择性沉积时间之后图5a中的器件500。因此,器件500可以具有平坦的顶表面505’,类似于图4f。

51.图5c示出了在进一步增加选择性沉积时间之后图5b中的器件500。因此,可以使金属膜505的顶表面505’呈现凸起。因此,可以通过调整选择性沉积时间来控制金属膜505的顶表面505’的凹度。随着沉积时间的增加,凹形表面可以发展为平坦表面,然后发展为凸起表面。

52.图6a、图6b和图6c是根据图3的示例过程形成的半导体器件的截面图像。图6a示出了示例性器件600的截面视图。器件600具有第一层601以及限定底部607和两个侧壁609的在第一层601中的凹陷。器件600还具有共形地涂覆第一层601的衬里膜(由于缩放而不可见)。器件600还包括金属膜605,该金属膜605在一定程度上共形地沉积在衬里膜上并填充凹陷的底部607。金属膜605在凹陷的底部607和侧壁609的下部处比在凹陷的侧壁609的上部和第一层601的顶表面601’处相对更厚。在所示的示例实施方式中,第一层601是氧化硅,并且金属膜605是钌。虽然在该示例中,第一层601被示出为单个层,但是在一些实施方式中,第一层601可以是由硅上方的氧化硅制成的双层结构,类似于图4c。

53.图6b示出了在使金属膜605凹陷之后图6a中的器件600。去除在凹陷的侧壁609的

上部和第一层601的顶表面601’处的金属膜605。因此,其余的金属膜605覆盖凹陷的底部607和侧壁609的下部。此外,其余的金属膜605具有凹形的顶表面605’。可以通过rie或湿法蚀刻处理来完成使金属膜605凹陷。例如,蚀刻剂可以是蚀刻钌但不蚀刻氮化硅或氧化硅的含有盐酸(hcl)和硝酸(hno3)的热溶液。替选地,基于氧气/氯气/氩气的rie可以去除钌,而对介电材料601没有损伤或损伤最小。

54.图6c示出了在去除衬里膜的未被覆盖的部分并在其余的金属膜605上方选择性地沉积相同金属之后图6b的器件600。可以通过诸如干法蚀刻或湿法蚀刻的任何技术来去除衬里膜的未被覆盖的部分(未示出)。例如,热浓正磷酸可以蚀刻氮化硅并且不蚀刻钌。在衬里膜404由氮化钛制成的上述实施方式中,可以使用sc1湿法蚀刻,上述sc1是氢氧化铵、过氧化氢和水的混合物。在衬里膜404是氮化钽的另一个实施方式中,这在钌的干法蚀刻(o2/cl2/ar)期间部分地发生,该干法蚀刻之后可以是湿法蚀刻步骤以去除任何残留物。可以使用或不使用sam完成选择性沉积,类似于图4f。因此,可以减少金属膜605的顶表面605’的凹度。此外,可以通过调整选择性沉积时间来控制金属膜605的顶表面605’的凹度。

55.在替选实施方式中,可以通过使用sam促进或诱导金属沉积来实现金属材料的选择性沉积。sam可以选择性地沉积在金属层405的顶表面405’上,使得sam可以用作金属沉积的前体(未示出)。随后,可以执行金属沉积处理以在其余的金属膜405上选择性地沉积相同的金属。此外,在一些实施方式中,可以在不使用sam的情况下实现金属材料的选择性沉积。可以执行对其余的金属膜405具有固有的选择性的金属沉积处理。

56.注意,在选择性沉积期间可以在一定程度上在非预期表面上非选择性地沉积一些金属材料(未示出)。因此,可以在金属沉积之后执行清洁处理以去除非选择性地沉积在第一层401的未被覆盖的部分上的金属。另外,在图4f示例中,金属膜405的顶表面405’可以与第二层402的顶表面402’处于同一水平。应当理解,可以调整金属膜405的顶表面405’以满足特定的设计要求。

57.图7是用于制造示例性半导体器件的替选过程700的流程图,该替选过程700对应于图7a至图7g中所示的过程。过程700开始于步骤s701,在步骤s701处,可以接收具有图案化的第一层和在第一层下方的第二层的衬底。第一层可以具有延伸至第二层中并限定底部和两个侧壁的凹陷特征。在一些实施方式中,衬底可以具有第一层以及限定底部和两个侧壁的第一层内的凹陷特征,而没有第一层下方的第二层。然后,过程800继续进行到步骤s702,在步骤s702处,可以在衬底的未被覆盖的表面上共形地沉积衬里膜,所述未被覆盖的表面包括凹陷特征的底部和侧壁以及第一层的顶表面。在步骤s703处,凹陷特征可以填充有填充材料,然后填充材料可以凹陷到预定深度,使得其余的填充材料覆盖衬里膜的一部分。在步骤s704处,可以从衬底去除衬里膜的未被覆盖的部分,使得其余的衬里膜衬在凹陷特征的底部和侧壁的部分上。在步骤s705处,可以去除其余的填充材料以使其余的衬里膜未被覆盖。在步骤s706处,可以在其余的衬里膜上选择性地沉积相同的金属材料。可以在有或没有sam的情况下完成金属材料的选择性沉积,并且金属材料的选择性沉积还可以包括清洁步骤以去除非选择性沉积的金属。此外,可以通过调整选择性沉积时间来控制金属膜的顶表面的凹度。

58.图8a至图8g是根据图7的示例过程形成的半导体器件的中间结构的截面示意图。图4a至图4f示出了当在金属凹陷之后但在选择性金属沉积之前去除衬里膜时的处理流程。

图8a至图8g中的替选实施方式示出了在任何金属沉积之前可以去除衬里膜的处理流程。

59.图8a示出了类似于图4a中的器件400的半导体器件800的截面视图。器件800可以具有图案化的第一层801和在第一层801下方的第二层802。第一层801可以具有延伸至第二层802中并限定底部807和两个侧壁809的凹陷特征。第二层802可以由任何半导体材料例如硅制成。第一层801可以是介电材料,例如氧化硅。可以通过使用蚀刻掩模限定要蚀刻的区域的方向性蚀刻来形成凹陷特征。

60.图8b示出了类似于图4b中的器件400的在衬里沉积之后的图8a中的器件800。衬里膜804可以共形地沉积在器件800中的未被覆盖的表面上,使得衬里膜804覆盖第一层801的顶表面801’、凹陷特征的底部807和侧壁809。衬里膜804可以提供电隔离并用作材料迁移的屏障。衬里膜804可以由介电材料例如氮化硅制成,并且可以通过任何技术例如原子层沉积或化学气相沉积而被沉积。

61.图8c示出了与图4c中所示的器件不同的在沉积填充材料806之后的图8b中的器件800。在该示例中,填充材料806可以完全填充凹陷特征并具有在第一层801的顶表面801’上方的顶表面806’。在替选实施方式中,填充材料806可以完全填充凹陷特征并具有在与第一层801的顶表面801’相同水平上的顶表面806’。在一些实施方式中,填充材料806可以部分地填充凹陷特征并具有在第一层801的顶表面801’下方的顶表面806’。填充材料806可以是与衬里膜804和第一层801不同的任何材料,并且可以通过任何技术被沉积。例如,填充材料806可以是通过化学气相沉积而沉积的多晶硅。另外,化学机械平坦化处理可以用于使填充材料806的顶表面806’平坦。

62.图8d示出了在使填充材料806凹陷到预定深度之后的图8c中的器件800。因此,其余的填充材料806可以覆盖凹陷特征的底部807和侧壁809的部分。在该示例中,其余填充材料806的顶表面806’可以在第二层802的顶表面802’上方。在一些实施方式中,其余填充材料806的顶表面806’可以在与第二层802的顶表面802’相同的水平上或者在第二层802的顶表面802’下方。注意,可以调整其余填充材料806的顶表面806’以满足特定的设计要求。例如,其余填充材料806的顶表面806’可以是电源轨道的期望顶表面或者在氧化硅与硅之间的界面处。另外,使填充材料806凹陷可以通过诸如干法蚀刻或湿法蚀刻的任何技术来完成。可以选择蚀刻剂,使得蚀刻剂蚀刻填充材料806但不蚀刻衬里膜804。例如,蚀刻剂可以是蚀刻多晶硅但不蚀刻氮化硅的含有四甲基氢氧化铵(tetramethylammonium hydroxide)的溶液。在填充材料806是旋涂碳型膜的实施方式中,然后,基于o2/co2/he的干法蚀刻可以用于该材料的选择性回蚀。

63.图8e示出了在去除衬里膜804的未被覆盖的部分之后的图8d中的器件800。其余的衬里膜804可以覆盖凹陷特征的底部807和侧壁809的部分。去除衬里膜804的未被覆盖的部分可以通过诸如湿法蚀刻的任何技术来完成。可以选择蚀刻剂,使得蚀刻剂蚀刻衬里膜804但不蚀刻第一层801或填充材料806。例如,蚀刻剂可以是蚀刻氮化硅但不蚀刻氧化硅或多晶硅的热浓正磷酸溶液。

64.图8f示出了在去除其余的填充材料806以便使其余的衬里膜804未被覆盖之后的图8e中的器件800。填充材料806的去除可以通过诸如湿法蚀刻的任何技术来完成。可以选择蚀刻剂,使得蚀刻剂蚀刻填充材料806但不蚀刻衬里膜804或第一层801。例如,蚀刻剂可以是蚀刻多晶硅但不蚀刻氮化硅或氧化硅的含有四甲基氢氧化铵的溶液。

65.图8g示出了在其余衬里膜804上选择性沉积金属之后的图8f中的器件800。类似于图4f,可以在有或没有sam的情况下实现选择性沉积,并且可以在选择性沉积之后执行后续清洁处理以去除非选择性金属沉积。因此,将强调不同之处来给出解释。在该示例中,金属膜805的顶表面805’可以在第二层802的顶表面802’上方。在一些实施方式中,金属膜805的顶表面805’可以在与第二层802的顶表面802’相同的水平上或者在第二层802的顶表面802’下方。可以调整金属膜805的顶表面805’以满足特定的设计要求。此外,可以通过调整选择性沉积时间来控制金属膜805的顶表面805’的凹度,如图6a、图6b和图6c中所示。

66.本文中描述的各种实施方式提供了优于相关制造过程的几个优点。例如,自底向上金属化可以大大缩短所需的金属凹陷时间并消除对化学机械平坦化步骤的需求。所公开的过程还可以提供对金属轨道的顶部的轮廓控制,并减小从轨道到轨道的高度变化。

67.在前面的描述中,已经阐述了具体细节,例如处理系统的特定几何形状以及对在其中使用的各种部件和过程的描述。然而,应该理解,可以在脱离这些具体细节的其他实施方式中实践本文中的技术,并且这些细节出于说明而非限制的目的。已经参照附图描述了本文中公开的实施方式。类似地,出于说明的目的,已经阐述了具体的数目、材料和配置,以便提供全面的理解。然而,可以在没有这样的具体细节的情况下实践实施方式。用相同的附图标记来表示具有基本上相同的功能结构的部件,因此可以省略任何冗余描述。

68.各种技术已经被描述为多个离散操作以帮助理解各种实施方式。描述的顺序不应被解释为暗示这些操作必须依赖于顺序。实际上,这些操作不需要以呈现的顺序被执行。可以以与所描述的实施方式不同的顺序执行所描述的操作。在其他实施方式中,可以执行各种附加操作以及/或者可以省略描述的操作。

69.如本文中所用的“衬底”或“目标衬底”通常是指根据本发明正被处理的对象。衬底可以包括器件特别是半导体或其他电子器件的任何材料部分或结构,并且衬底可以例如是基础衬底结构,比如半导体薄片、标线片或者在基础衬底结构上或覆盖基础衬底结构的层,例如薄膜。因此,衬底不限于任何特定的基础结构、下层或覆盖层、图案化或未图案化,而是预期包括任何这样的层或基础结构以及层和/或基础结构的任何组合。描述可能涉及特定类型的衬底,但这仅用于说明目的。

70.本领域技术人员还将理解,可能存在针对上面说明的技术的操作做出的许多变化,但是仍然能实现本发明的相同目标。这些变化旨在由本公开内容的范围涵盖。因此,本发明的实施方式的前述描述不旨在进行限制。而是,在所附权利要求中呈现了对本发明的实施方式的任何限制。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。