1.本发明涉及一种半导体管芯以及半导体装置的制作方法,尤其是涉及一种具有多个切割步骤的半导体装置的制作方法以及以此制作方法形成的半导体管芯。

背景技术:

2.在现在社会中,由集成电路(integrated circuit,ic)构成的微处理系统早已被普遍运用于生活的各个层面,例如家电用品、移动通讯设备、个人计算机等,都有集成电路的使用。一般所称集成电路,是通过半导体制作工艺中所生产的管芯(die)而形成。制造管芯的过程,是由生产一晶片(wafer)开始:首先,在一片晶片上区分出多个区域,并在每个区域上,通过各种半导体制作工艺如沉积、光刻、蚀刻或平坦化制作工艺,以形成各种所需的电路路线。然后,对晶片上的各个区域进行切割而成各个管芯,而管芯可通过封装或/及与其他集成电路结构连接而形成所需的半导体装置。因此,上述切割步骤的制作工艺良率将直接影响到产品的制作成本,且在晶片上对应切割步骤的切割道所占面积也直接影响到晶片面积使用率。

技术实现要素:

3.本发明提供了一种半导体管芯以及半导体装置的制作方法,利用对半导体晶片进行第一切割步骤、第二切割步骤以及在第一切割步骤与第二切割步骤之间的薄化步骤,由此达到提升制作工艺良率或/及提升晶片面积使用率的效果。

4.本发明的一实施例提供一种半导体管芯,其包括两个第一侧表面彼此分离以及两个第二侧表面彼此分离。两个第一侧表面于一第一方向上彼此相对,两个第二侧表面于一第二方向上彼此相对,第二方向垂直于第一方向,且各第一侧表面的粗糙度不同于各第二侧表面的粗糙度。

5.本发明的一实施例提供一种半导体装置的制作方法,包括下列步骤。提供一半导体晶片,半导体晶片具有多个管芯区以及一切割道区,且切割道区围绕各管芯区。对半导体晶片进行一分离制作工艺(singulation process),用以形成多个互相分离的半导体管芯,且各半导体管芯形成于多个管芯区中的一个之内。分离制作工艺包括一第一切割步骤、一薄化步骤以及一第二切割步骤。第一切割步骤对半导体晶片进行蚀刻而于半导体晶片中形成多个第一开口。各第一开口形成于切割道区中,且半导体晶片的一部分在半导体晶片的一厚度方向上位于各第一开口与半导体晶片的一背表面之间。在第一切割步骤之后对半导体晶片进行的薄化步骤,位于各第一开口与半导体晶片的背表面之间的半导体晶片的部分被薄化步骤移除,且各第一开口于薄化步骤之后贯穿半导体晶片。

6.在薄化步骤之后进行第二切割步骤,用以形成多个第二开口。各第二开口贯穿半导体晶片而将多个半导体管芯互相分离。

附图说明

7.图1至图9为本发明第一实施例的半导体装置的制作方法示意图,其中

8.图2为图1之后的状况示意图;

9.图3a为沿图2中a-a’剖线所绘示的剖视图;

10.图3b为沿图2中b-b’剖线所绘示的剖视图;

11.图4a为图3a之后的状况示意图;

12.图4b为图3b之后的状况示意图;

13.图5a为图4a之后的状况示意图;

14.图5b为图4b之后的状况示意图;

15.图6a为图5a之后的状况示意图;

16.图6b为图5b之后的状况示意图;

17.图7为图6b之后的状况示意图;

18.图8为图7的状况的对应上视示意图;

19.图9为图7之后的状况示意图;

20.图10为本发明一实施例的半导体管芯的上视示意图;

21.图11为本发明另一实施例的半导体管芯的上视示意图;

22.图12为本发明第二实施例的半导体装置的制作方法示意图;

23.图13至图19为本发明第三实施例的半导体装置的制作方法示意图,其中

24.图14为图13之后的状况示意图;

25.图15a为沿图14中c-c’剖线所绘示的剖视图或沿图14中d-d’剖线所绘示的剖视图;

26.图15b为沿图14中e-e’剖线所绘示的剖视图;

27.图16为图15a之后的状况示意图;

28.图17a为图16之后的状况示意图;

29.图17b为图17a的状况下沿另一方向的部分剖面示意图;

30.图18为图17b之后的状况示意图;

31.图19为图18的状况的对应上视示意图;

32.图20为本发明第四实施例的半导体装置的制作方法示意图。

33.主要元件符号说明

34.10

ꢀꢀ

第一半导体晶片

35.11

ꢀꢀ

第一基底

36.11a 第一表面

37.11b 第二表面

38.12

ꢀꢀ

第一主动装置层

39.13

ꢀꢀ

第一互连层

40.14

ꢀꢀ

第一钝化层

41.15

ꢀꢀ

第一接触垫

42.20

ꢀꢀ

第二半导体晶片

43.21

ꢀꢀ

第二基底

44.22

ꢀꢀ

第二主动装置层

45.23

ꢀꢀ

第二互连层

46.24

ꢀꢀ

第二钝化层

47.25

ꢀꢀ

第二接触垫

48.31

ꢀꢀ

保护膜

49.32

ꢀꢀ

支撑基底

50.81

ꢀꢀ

第一图案化掩模层

51.82

ꢀꢀ

第二图案化掩模层

52.90

ꢀꢀ

分离制作工艺

53.91

ꢀꢀ

第一切割步骤

54.92

ꢀꢀ

薄化步骤

55.93

ꢀꢀ

第二切割步骤

56.100 半导体装置

57.bs

ꢀꢀ

背表面

58.d1

ꢀꢀ

第一方向

59.d2

ꢀꢀ

第二方向

60.d3

ꢀꢀ

第三方向

61.d4

ꢀꢀ

第四方向

62.f1

ꢀꢀ

第一侧表面

63.f2

ꢀꢀ

第二侧表面

64.f3

ꢀꢀ

角落侧表面

65.fs

ꢀꢀ

前表面

66.op1 第一开口

67.op2 第二开口

68.r1

ꢀꢀ

管芯区

69.r2

ꢀꢀ

切割道区

70.s1

ꢀꢀ

第一部分

71.s2

ꢀꢀ

第二部分

72.s3

ꢀꢀ

角落部分

73.sd

ꢀꢀ

半导体管芯

74.w1

ꢀꢀ

宽度

75.w2

ꢀꢀ

宽度

具体实施方式

76.以下本发明的详细描述已披露足够的细节以使本领域的技术人员能够实践本发明。以下阐述的实施例应被认为是说明性的而非限制性的。对于本领域的一般技术人员而言显而易见的是,在不脱离本发明的精神和范围的情况下,可以进行形式及细节上的各种改变与修改。

77.在进一步的描述各实施例之前,以下先针对全文中使用的特定用语进行说明。

78.用语“在

…

上”、“在

…

上方”和“在

…

之上”的含义应当以最宽方式被解读,以使得“在

…

上”不仅表示“直接在”某物上而且还包括在某物上且其间有其他居间特征或层的含义,并且“在

…

上方”或“在

…

之上”不仅表示在某物“上方”或“之上”的含义,而且还可以包括其在某物“上方”或“之上”且其间没有其他居间特征或层(即,直接在某物上)的含义。

79.说明书与权利要求中所使用的序数例如“第一”、“第二”等用词,是用以修饰权利要求的元件,除非特别说明,其本身并不意含及代表该请求元件有任何之前的序数,也不代表某一请求元件与另一请求元件的顺序、或是制造方法上的顺序,该些序数的使用仅用来使具有某命名的一请求元件得以和另一具有相同命名的请求元件能作出清楚区分。

80.用语“蚀刻”在本文中通常用来描述用以图案化材料的制作工艺,使得在蚀刻完成后的材料的至少一部分能被留下。当“蚀刻”一材料时,该材料的至少一部分在蚀刻结束后可被保留。与此相反的是,当“移除”材料时,基本上所有的材料可在过程中被除去。然而,在一些实施例中,“移除”可被认为是一个广义的用语而包括蚀刻。

81.在下文中使用术语“形成”或“设置”来描述将材料层施加到基底的行为。这些术语旨在描述任何可行的层形成技术,包括但不限于热生长、溅射、蒸发、化学气相沉积、外延生长、电镀等。

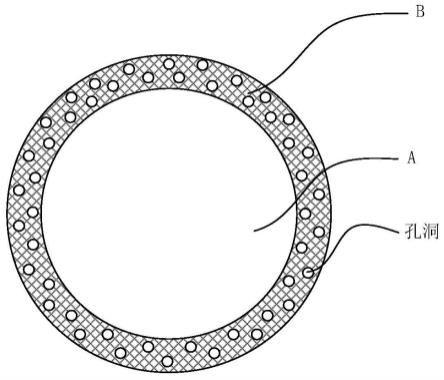

82.请参阅图1至图9。图1至图9为本发明第一实施例的半导体装置的制作方法示意图,其中图2绘示了图1之后的状况示意图,图3a为沿图2中a-a’剖线所绘示的剖视图,图3b为沿图2中b-b’剖线所绘示的剖视图,图4a绘示了图3a之后的状况示意图,图4b绘示了图3b之后的状况示意图,图5a绘示了图4a之后的状况示意图,图5b绘示了图4b之后的状况示意图,图6a绘示了图5a之后的状况示意图,图6b绘示了图5b之后的状况示意图,图7绘示了图6b之后的状况示意图,图8绘示了图7的状况的对应上视示意图,而图9绘示了图7之后的状况示意图。本实施例提供一种半导体装置的制作方法,包括下列步骤。首先,如图1所示,提供一半导体晶片(例如第一半导体晶片10),第一半导体晶片10具有多个管芯区r1以及一切割道(scribe line)区r2,且切割道区r2围绕各管芯区r1。在一些实施例中,切割道区r2可包括多个第一部分s1以及多个第二部分s2,各第一部分s1可沿一第一方向d1延伸,而各第二部分s2可沿一第二方向d2延伸,且第二方向d2可大体上垂直于第一方向d1,但并不以此为限。在一些实施例中,切割道区r2的第一部分s1与第二部分s2可互相交错而围绕各管芯区r1。

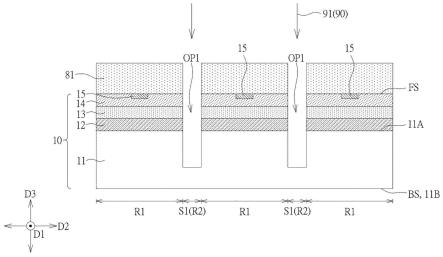

83.然后,如图2至图8所示,对第一半导体晶片10进行一分离制作工艺(singulation process)90,用以形成多个互相分离的半导体管芯sd,且各半导体管芯sd形成于多个管芯区r1中的一个之内。在一些实施例中,分离制作工艺90可包括一第一切割步骤(例如图3a所示的一第一切割步骤91)、一薄化步骤(例如图4a与图4b所示的一薄化步骤92)以及一第二切割步骤(例如图6b所示的第二切割步骤93)。如图2、图3a以及图3b所示,第一切割步骤91可对第一半导体晶片10进行蚀刻而于第一半导体晶片10中形成多个第一开口op1。各第一开口op1形成于切割道区r2中,且在第一切割步骤91之后,第一半导体晶片10的一部分在第一半导体晶片10的一厚度方向(例如图2、图3a以及图3b中所示的一第三方向d3)上位于各第一开口op1与第一半导体晶片10的一背表面bs之间。之后,如图3a至与图5b所示,在第一切割步骤91之后对第一半导体晶片10进行的薄化步骤92,位于各第一开口op1与第一半导体晶片10的背表面bs之间的第一半导体晶片10的部分被薄化步骤92移除,使得各第一开口

op1于薄化步骤92之后可于第三方向d3上贯穿第一半导体晶片10。然后,如图5a至图7所示,在薄化步骤92之后进行第二切割步骤93,用以形成多个第二开口op2。各第二开口op2可于第三方向d3上贯穿第一半导体晶片10而形成多个半导体管芯sd且将多个半导体管芯sd互相分离。

84.进一步说明,本实施例的制作方法可包括但并不限于下列步骤。如图2、图3a以及图3b所示,在一些实施例中,各第一开口op1可分别沿第一方向d1延伸且彼此互相平行,而各第一开口op1可形成于切割道区r2的多个第一部分s1中的一个之内。值得说明的是,各第一开口op1可分别延第一方向d1延伸但未延伸至第一半导体晶片10的边缘,由此加强第一半导体晶片10在后续进行薄化步骤时的强度,避免于薄化步骤时即发生第一半导体晶片10中部分区域分离的现象,进而可提升薄化步骤的制作工艺良率,但并不以此为限。

85.在一些实施例中,第一半导体晶片10可包括一第一基底11、一第一主动装置层12、一第一互连层13、一第一钝化层14以及至少一第一接触垫15于第三方向d3上堆叠设置。第一基底11可具有一第一表面11a以及一第二表面11b,第一表面11a与第二表面11b可于第一半导体晶片10的厚度方向(例如第三方向d3)上彼此相对,而第一表面11a与第二表面11b可分别为第一基底11在第三方向d3上相反的上表面与下表面,但并不以此为限。在一些实施例中,第一主动装置层12、第一互连层13、第一钝化层14以及第一接触垫15可设置于第一基底11的第一表面11a上,第一基底11的第二表面11b可被视为第一半导体晶片10的背表面bs,而与背表面bs在第三方向d3上相反的第一半导体晶片10的前表面fs可为第一钝化层14或/及第一接触垫15的一表面,但并不以此为限。值得说明的是,本发明的第一半导体晶片10的结构并不以上述的状况为限而也可视设计需要而包括其他需要的部件。

86.在一些实施例中,上述的第三方向d3可被视为第一半导体晶片10或/及第一基底11的厚度方向,而与第三方向d3大体上正交的水平方向(例如上述的第一方向d1与第二方向d2)可与上述的第一半导体晶片10的被表面bs、前表面fs、第一基底11的第一表面11a或/及第二表面11b平行,但并不以此为限。此外,在本文中所述在第三方向d3上相对较高的位置或/及部件与第一基底11的第一表面11a之间在第三方向d3上的距离大于在第三方向d3上相对较低的位置或/及部件与第一基底11的第一表面11a之间在第三方向d3上的距离,各部件的底部可比此部件的顶部在第三方向d3上更接近第一基底11的第一表面11a,在某个部件之上的另一部件可被视为在第三方向d3上相对较远离第一基底11的第一表面11a,而在某个部件之下的另一部件可被视为在第三方向d3上相对较接近第一基底11的第一表面11a。

87.在一些实施例中,第一基底11可包括硅基底、硅锗半导体基底、硅覆绝缘(silicon-on-insulator,soi)基底或其他适合的材料所形成的半导体基底。第一主动装置层12可包括主动(有源)元件或/及被动(无源)元件,例如晶体管、二极管、电容器、电阻器等,而第一互连层13可包括层间介电层以及设置于层间介电层中的多层导电层与多个导电插塞,用以电连接第一主动装置层12中的元件或/及使得第一主动装置层12中的元件电连接至第一接触垫15,但并不以此为限。上述的层间介电层以及钝化层14可包括介电材料,例如氧化硅、氮化硅、氮氧化硅、低介电常数(low dielectric constant,low-k)介电材料或其他适合的介电材料。上述的low-k介电材料可包括苯并环丁烯(benzocyclclobutene,bcb)、hsq(hydrogen silsesquioxane)、msq(methyl silesquioxane)、硅氧碳氢化物

(sioc-h)、多孔性介电材料或其他适合的low-k介电材料。第一接触垫15以及上述的导电层与导电插塞可分别包括导电材料例如钨、铝、铜、铝化钛(titanium aluminide,tial)、钛、氮化钛(titanium nitride,tin)、钽、氮化钽(tantalum nitride,tan)、氧化铝钛(titanium aluminum oxide,tialo)等或其他适合的导电材料。

88.在一些实施例中,第一切割步骤91可包括一干式蚀刻制作工艺,用以移除第一半导体晶片10的一部分而形成上述的第一开口op1,但并不以此为限。在一些实施例中,第一切割步骤91也可包括其他非等向性(anisotropic)蚀刻制作工艺或其他适合的蚀刻方式,用以形成第一开口op1并控制第一开口op1的深度与大小。在一些实施例中,可于第一半导体晶片10的前表面fs上形成一第一图案化掩模层81,用以覆盖第一半导体晶片10上不须形成第一开口op1的区域,而第一图案化掩模层81可被视为第一切割步骤91中的蚀刻掩模,但并不以此为限。第一图案化掩模层81可包括单层或多层的掩模材料,例如光致抗蚀剂材料、抗反射材料、有机介电材料或其适合的掩模材料,而第一图案化掩模层81可于第一切割步骤91之后以及上述的薄化步骤之前被移除。在第一切割步骤91之后,各第一开口op1的一部分可于第一半导体晶片10的厚度方向(例如第三方向d3)上自第一基底11的第一表面11a朝向第二表面11b延伸,且各第一开口op1并未贯穿第一半导体晶片10以及第一基底11。因此,在第一切割步骤91之后以及上述的薄化步骤之前,第一基底11的一部分可在第三方向d3上位于各第一开口op1与第二表面11b之间。

89.如图2至图4b所示,在第一切割步骤91之后以及薄化步骤92之前,可将一保护膜31附于第一半导体晶片10的前表面fs上,然后可自第一半导体晶片10的背表面bs(也就是第一基底11的第二表面11b)进行薄化步骤92,用以薄化第一半导体晶片10中的第一基底11。在一些实施例中,薄化步骤92可包括化学机械研磨薄化、回蚀刻或其他适合的物理性或/及化学性薄化方式,而保护膜31可包括一研磨胶带(back grinding tape)、一绝缘膜或其他适合之具有黏性或不具黏性的保护材料,用以在薄化步骤92中提供保护效果。在一些实施例中,第一基底11的厚度可被薄化步骤92减少,且在第三方向d3上位于各第一开口op1与第一半导体晶片10的背表面bs之间的部分(例如在第三方向d3上位于各第一开口与第一基底11的第二表面11a之间的部分的第一基底11)可被薄化步骤92移除,使得各第一开口op1可于薄化步骤92之后贯穿第一半导体晶片10。值得说明的是,由于进行薄化步骤92时还未形成上述的第二开口,故可相对增加第一半导体晶片10的前表面fs与保护膜31之间的接合面积,进而可提升第一半导体晶片10与保护膜31之间的接合力而有助于薄化步骤92的进行与制作工艺良率。

90.如图5a至图7所示,在薄化步骤92之后以及第二切割步骤93之前,可将一支撑基底32附于第一半导体晶片10的背表面bs上,并可移除保护膜31而暴露出第一半导体晶片10的前表面fs,用以接着自第一半导体晶片10的前表面fs进行第二切割步骤93。在一些实施例中,支撑基底32可包括胶带例如pvc胶膜、金属基底、绝缘基底例如硅基板、玻璃基底、塑胶基底、蓝宝石(sapphire)基底、陶瓷基底或其他适合种类的支撑材料。然后,进行第二切割步骤93,用以形成多个第二开口op2,并因此将至少部分的第一半导体晶片10切割成多个互相分离的半导体管芯sd。如图7与图8所示,各第二开口op2可于第三方向d3上贯穿第一半导体晶片10,且各第二开口op2可沿第二方向d2延伸并形成于切割道区r2的多个第二部分s2中的一个之内。第一开口op1与第二开口op2可彼此相交,由此将至少部分的第一半导体晶

片10切割成多个互相分离的半导体管芯sd,且各半导体管芯sd可形成于对应的管芯区r1中。

91.在一些实施例中,第二切割步骤93可包括一切割刀(saw blade)切割制作工艺,利用切割刀自第一半导体晶片10的前表面fs对第一半导体晶片10进行切割而形成第二开口op2,但并不以此为限。在一些实施例中,第二切割步骤93也可视设计需要而包括其他适合的方式,例如雷射切割制作工艺、干式蚀刻制作工艺或/及湿式蚀刻制作工艺,用以移除第一半导体晶片10的一部分而形成第二开口op2,但并不以此为限。此外,在一些实施例中,还可在第二切割步骤93之后对半导体管芯sd进行的一湿式蚀刻制作工艺,用以弧形化各半导体管芯sd的角落,但并不以此为限。值得说明的是,当上述的第一切割步骤与第二切割步骤分别使用不同的方法进行时,对应形成的第一开口op1的宽度w1可不同于第二开口op2的宽度w2,且各半导体管芯sd对应第一开口op1的侧表面的粗糙度(roughness)可不同于对应第二开口op2的侧表面的粗糙度,但并不以此为限。此外,第一开口op1的宽度w1也可被视为第一开口op1于第二方向d2上的长度,而第二开口op2的宽度w2也可被视为第二开口op2于第一方向d1上的长度。举例来说,当第一切割步骤为干式蚀刻制作工艺且第二切割步骤为割刀切割制作工艺时,各第二开口op2的宽度w2可大于各第一开口op1的宽度w1,而各半导体管芯sd对应第一开口op1的侧表面的粗糙度可低于对应第二开口op2的侧表面的粗糙度,但并不以此为限。

92.在一些实施例中,各半导体管芯sd包括第一主动装置层12而可被视为一半导体装置,但并不以此为限。在一些实施例中,也可利用上述制作方法所形成的半导体管芯sd与其他部件结合而形成所需的半导体装置。举例来说,如图7与图9所示,在形成半导体管芯sd之后,可将多个半导体管芯sd与一第二半导体晶片20接合(bonding)而形成一半导体装置100。第二半导体晶片20可包括一第二基底21、一第二主动装置层22、一第二互连层23、一第二钝化层24以及至少一第二接触垫25于第三方向d3上堆叠设置。在一些实施例中,第二基底21、第二主动装置层22、第二互连层23、第二钝化层24以及第二接触垫25的材料或/及结构可分别与上述的第一基底11、第一主动装置层12、第一互连层13、第一钝化层14以及第一接触垫15相似,但并不以此为限。各半导体管芯sd与第二半导体晶片20可通过第一接触垫15与第二接触垫25进行键合而形成电连接,且半导体装置100可被视为一晶片上芯片(chip-on-wafer,cow)键合结构,但并不以此为限。在一些实施例中,可于第二切割步骤之后将各半导体管芯sd与支撑基底32分离,然后再将半导体管芯sd与第二半导体晶片20进行接合,但并不以此为限。在一些实施例中,也可将支撑基底32上的各半导体管芯sd与第二半导体晶片20进行对位与接合之后,再将支撑基底32移除,而支撑基底32也可包括具有弹性的基底,用以调整在进行接合时各半导体管芯sd在支撑基底32上的间距或/及相对位置,但并不以此为限。

93.请参阅图10与图11。图10为本发明一实施例的半导体管芯sd的上视示意图,而图11为本发明另一实施例的半导体管芯sd的上视示意图。如图10所示,在一些实施例中,半导体管芯sd可包括两个第一侧表面f1彼此分离以及两个第二侧表面f2彼此分离。两个第一侧表面f1于第一方向d1上彼此相对,两个第二侧表面f2于第二方向d2上彼此相对,第二方向d2垂直于第一方向d1,且各第一侧表面f1的粗糙度不同于各第二侧表面f2的粗糙度。在一些实施例中,半导体管芯sd可由上述的制作方法所形成,各第一侧表面f1可对应上述制作

方法中的第二切割步骤所形成的第二开口,而各第二侧表面f2可对应上述制作方法中的第一切割步骤所形成的第一开口。因此,当第一切割步骤与第二切割步骤分别使用不同的方法进行时,可造成各第一侧表面f1的粗糙度不同于各第二侧表面f2的粗糙度。举例来说,当第一切割步骤为干式蚀刻制作工艺且第二切割步骤为割刀切割制作工艺时,第二侧表面f2的粗糙度可低于第一侧表面f1的粗糙度,但并不以此为限。此外,在一些实施例中,各第一侧表面f1可沿第二方向d2延伸,各第二侧表面f2可沿第一方向d1延伸,而各第一侧表面f1可直接连接两个第二侧表面f2。换句话说,在半导体管芯sd的上视图中,半导体管芯sd可为一矩形,两个第一侧表面f1与两个第二侧表面f2可为此矩形的四个边,而第一方向d1与第二方向d2可大体上分别与半导体管芯sd的一厚度方向(例如第三方向d3)正交,但并不以此为限。

94.如图11所示,在一些实施例中,半导体管芯sd可还包括多个角落侧表面f3,且各角落侧表面f3可分别与两个第一侧表面f1中的一个以及两个第二侧表面f2中的一个直接相连。在一些实施例中,各角落侧表面f3可为弧形表面,而此弧形表面可通过上述在第二切割步骤93之后对半导体管芯sd进行的湿式蚀刻制作工艺所形成,但并不以此为限。因此,各角落侧表面f3的粗糙度也可不同于各第一侧表面f1的粗糙度或/及各第二侧表面f2的粗糙度,而对角落侧表面f3进行弧形化可降低半导体管芯sd在角落处的应力破坏,对于半导体管芯sd在后续处理过程(例如封装制作工艺,但并不以此为限)的良率有正面帮助。

95.下文将针对本发明的不同实施例进行说明,且为简化说明,以下说明主要针对各实施例不同之处进行详述,而不再对相同之处作重复赘述。此外,本发明的各实施例中相同的元件是以相同的标号进行标示,以利于各实施例间互相对照。

96.请参阅图12。图12为本发明第二实施例的半导体装置的制作方法示意图。如图12所示,本实施例的第二切割步骤93可包括一干式蚀刻制作工艺,用以移除第一半导体晶片10的一部分而形成多个第二开口op2。在一些实施例中,可于第一半导体晶片10的前表面fs上形成一第二图案化掩模层82,用以覆盖第一半导体晶片10上不须形成第二开口op2的区域,而第二图案化掩模层82可被视为第二切割步骤93中的蚀刻掩模,但并不以此为限。第二图案化掩模层82可包括单层或多层的掩模材料,例如光致抗蚀剂材料、抗反射材料、有机介电材料或其适合的掩模材料,而第二图案化掩模层82可于第二切割步骤93之后被移除。换句话说,在一些实施例中,可利用蚀刻方式进行上述的第一切割步骤与第二切割步骤,并于第一切割步骤与第二切割步骤之间进行薄化步骤,而利用蚀刻方式进行第二切割步骤可缩小第二开口op2的宽度w2,进而可提升第一半导体晶片10的晶片面积使用率。

97.请参阅图13至图19。图13至图19为本发明第三实施例的半导体装置的制作方法示意图,其中图14绘示了图13之后的状况示意图,图15a为沿图14中c-c’剖线所绘示的剖视图或沿图14中d-d’剖线所绘示的剖视图,图15b为沿图14中e-e’剖线所绘示的剖视图,图16绘示了图15a之后的状况示意图,图17a绘示了图16之后的状况示意图,图17b绘示了图17a的状况下沿另一方向(例如第四方向d4)的部分剖面示意图,图18绘示了图17b之后的状况示意图,图19绘示了图18的状况的对应上视示意图,而图18可被视为沿图19中f-f’剖线所绘示的剖视图。如图13所示,在一些实施例中,切割道区r2可还包括多个角落部分s3,各角落部分s3位于在第一方向d1上相邻的两个第一部分s1之间且位于在第二方向d2上相邻的两个第二部分s2之间,而第一部分s1与第二部分s2可未直接相连。

98.如图14、图15a与图15b所示,可对第一半导体晶片10进行分离制作工艺90中的第一切割步骤91,对第一半导体晶片10进行蚀刻而于第一半导体晶片10中形成多个第一开口op1。在一些实施例中,多个第一开口op1可分别形成于第一部分s1以及第二部分s2之内,且多个第一开口op1可彼此互相分离。举例来说,一些第一开口op1可形成于第一部分s1中,而另一些第一开口op1可形成于第二部分s2,形成于第一部分s1中的第一开口op1可沿第一方向d1延伸,形成于第二部分s2中的第一开口op1可沿第二方向d2延伸,且相邻的第一开口op1可被角落部分s3分隔。在第一切割步骤91之后,各第一开口op1的一部分可于第三方向d3上自第一基底11的第一表面11a朝向第二表面11b延伸,且各第一开口op1并未贯穿第一半导体晶片10以及第一基底11。

99.如图14至图17b所示,在第一切割步骤91之后以及薄化步骤92之前,可将保护膜31附于第一半导体晶片10的前表面fs上,然后可自第一半导体晶片10的背表面bs(也就是第一基底11的第二表面11b)进行薄化步骤92,用以薄化第一半导体晶片10中的第一基底11,并使各第一开口op1于薄化步骤92之后贯穿第一半导体晶片10与第一基底11。在一些实施例中,图17b可被视为绘示了图17a的状况下沿第四方向d4的部分剖面示意图,第四方向d4可大体上与第三方向d3正交,而第四方向d4可未垂直于第一方向d1与第二方向d2,但并不以此为限。值得说明的是,由于第一开口op1彼此互相分离而第一半导体晶片10的各管芯区r1在薄化步骤92时仍可通过切割道区r2的角落部分s3而彼此相连,故可相对增加第一半导体晶片10的前表面fs与保护膜31之间的接合面积,进而可提升第一半导体晶片10与保护膜31之间的接合力而有助于薄化步骤92的进行与制作工艺良率。

100.然后,如图16至图19所示,在薄化步骤92之后以及第二切割步骤93之前,可将支撑基底32附于第一半导体晶片10的背表面bs上,并可移除保护膜31而暴露出第一半导体晶片10的前表面fs,用以接着自第一半导体晶片10的前表面fs进行第二切割步骤93。然后,进行第二切割步骤93,用以形成多个第二开口op2,并因此将至少部分的第一半导体晶片10切割成多个互相分离的半导体管芯sd。在一些实施例中,各第二开口op2可形成于多个角落部分s3中的一个之内,且各第二开口op2可与相邻的第一开口op1直接相连,用以分隔各半导体管芯sd。在一些实施例中,第二切割步骤93可包括一干式蚀刻制作工艺,用以移除第一半导体晶片10的一部分而于角落部分s3形成第二开口op2,但并不以此为限。在一些实施例中,也可视设计需要以其他方式(例如湿式蚀刻)移除位于角落部分s3的第一半导体晶片10而分离各半导体管芯sd。在本实施例的制作方法中,可利用蚀刻方式形成沿第一方向d1延伸的第一开口op1以及沿第二方向d2延伸的第一开口op1,故可缩小相邻管芯区r1之间的距离,进而可提升第一半导体晶片10的晶片面积使用率。

101.请参阅图20以及图18。图20为本发明第四实施例的半导体装置的制作方法示意图,而图18可被视为沿图20中g-g’剖线所绘示的剖视图。如图20与图18所示,在一些实施例中,第二切割步骤93可包括一湿式蚀刻制作工艺,用以移除第一半导体晶片10的一部分而于角落部分s3形成第二开口op2,且湿式蚀刻制作工艺可用以弧形化各半导体管芯sd的角落,使得半导体管芯sd的角落侧表面(例如图11中所示的角落侧表面f3)成为弧形表面,但并不以此为限。在一些实施例中,第二切割步骤93可包括干式蚀刻制作工艺以及于此干式蚀刻制作工艺之后进行的湿式蚀刻制作工艺,用以形成第二开口op2并达到上述弧形化各半导体管芯sd的角落的效果,但并不以此为限。

102.请参阅图20、图18以及图19。在一些实施例中,图18可被视为沿图19中f-f’剖线所绘示的剖视图,而图20可被视为绘示了图19之后的状况示意图。因此,如图18至图20所示,在一些实施例中,可于第二切割步骤93之后进行的湿式蚀刻制作工艺,用以弧形化各半导体管芯sd的角落。换句话说,可于第二开口op2形成之后再进行湿式蚀刻制作工艺以弧形化各半导体管芯sd的角落侧表面。

103.综上所述,在本发明的半导体管芯以及半导体装置的制作方法中,可利用对半导体晶片进行第一切割步骤、第二切割步骤以及在第一切割步骤与第二切割步骤之间的薄化步骤来达到切割半导体晶片并形成互相分离的半导体管芯的效果。其中,第一切割步骤或/及第二切割步骤可利用蚀刻方式进行,由此可缩小相邻管芯区之间的距离,进而提升半导体晶片的晶片面积使用率。此外,由于第二切割步骤是于薄化步骤之后进行,故可相对增加半导体晶片与保护膜之间的接合面积,进而可提升半导体晶片与保护膜之间的接合力而有助于薄化步骤的进行与制作工艺良率。

104.以上所述仅为本发明的优选实施例,凡依本发明权利要求所做的均等变化与修饰,都应属本发明的涵盖范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。