1.本发明属于半导体技术领域,具体涉及一种半导体器件的形成方法及半导体器件。

背景技术:

2.芯片行业的日益更新,技术节点的日趋提升,对工艺和技术的精雕细琢也要求越来越高,尤其是到了3纳米及以下,精细化工艺就日趋突出,例如绝大部分工艺的均一性(uniformity),不管在薄膜的沉积还是刻蚀,抛光等工艺随着纳米节点的提升都需要很高的均一性。在刻蚀方面,又例如需要工艺的精准性,低损伤及较强的刻蚀能力。

3.目前在3nm及以下,有机材料的刻蚀面临着极大的挑战,尤其是小孔(宽度尺寸低于15nm)刻蚀,由于该小孔具有很高的深宽比,小孔底部的刻蚀能力急剧减弱,再加上介质层的复杂化,光阻图形层的密集程度,小孔刻蚀遭到多方面的瓶颈,需要同时满足例如较低的薄膜损失,合适的光阻尺寸,较强的有机刻蚀能力等条件。

4.目前的化学环境很难全部满足这些条件,在实际应用中,也是如此。图1示出了一种具有高深宽比小尺寸的有机涂层的小孔刻蚀完成前后状态示意图,图1中的a是半导体器件的初始状态示意图,经过刻蚀后,通常存在以下问题:如图1的b所示,1)顶部介电质层薄膜损失较大(损失薄膜层11);2)底部有残留有机层12。形成这些问题的最主要原因就是刻蚀的刻蚀剂(etchant)不够及轰击力(bombardment)较强造成了光阻被溅射(sputter)到小孔里面及薄膜的损失。

5.因此,亟需研发一种适于小孔刻蚀工艺,以降低介电质层顶部的损失,同时降低有机层的残留。

技术实现要素:

6.本发明的目的是解决高深宽比的小孔刻蚀工艺中,顶部介电质层薄膜损失较大以及小孔底部易残留有机层的问题,提供一种方法,在小孔刻蚀前在介电质层、图形层表面形成一保护层,从而无需为避免将图形层的光阻材料溅射到小孔内而减小轰击力,也无需为减少介电质层的损失而降低刻蚀剂的浓度,使得小孔内刻蚀能力较强,底部无残留有机层,且介电质层损失较小。

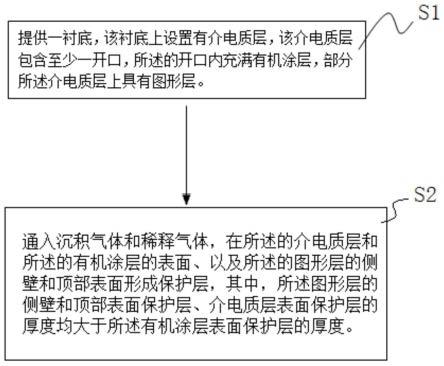

7.为了达到上述目的,本发明提供了一种半导体器件的形成方法,其包含:

8.提供一衬底,该衬底上设置有介电质层,该介电质层包含至少一开口,所述的开口内充满有机涂层,部分所述介电质层上具有图形层;

9.通入沉积气体和稀释气体,在所述的介电质层和所述的有机涂层的表面、以及所述的图形层的侧壁和顶部表面形成保护层,其中,所述图形层侧壁和顶部表面保护层、介电质层表面保护层的厚度均大于所述有机涂层表面保护层的厚度。

10.可选的,所述的沉积气体为c

xhy

,x=1~5,y=2~8,所述的稀释气体包括:co和co2中的至少一种。

11.可选的,所述的沉积气体包括ch4,c2h6和c2h4中的至少一种。

12.可选的,所述的沉积气体与稀释气体的体积比为1:1~3:1。

13.可选的,所述的开口的宽度为5nm~15nm。

14.可选的,所述的开口的宽度为6nm~8nm。

15.可选的,所述的有机涂层为底部抗反射层。

16.可选的,所述的图形层为光刻胶。

17.可选的,所述沉积形成保护层的工艺条件包含:压力为40mt~120mt,射频频率为50mhz~70mhz,功率为150w~600w,上电极温度为80℃~120℃,下电极温度为15℃~30℃。

18.可选的,形成所述保护层之后,还包含:对所述有机涂层的刻蚀,以暴露开口底部的衬底。

19.可选的,形成所述保护层步骤和对所述有机涂层的刻蚀步骤交替进行,直至暴露开口底部的衬底。

20.本发明还提供了一种半导体器件,包括:

21.衬底,所述衬底上具有介电质层,该介电质层包含至少一开口,所述的开口内充满有机涂层,部分所述介电质层上具有图形层;

22.位于所述的介电质层和所述的有机涂层的表面、以及图形层的侧壁和顶部表面的保护层,且所述图形层侧壁和顶部表面保护层、介电质层表面保护层的厚度均大于有机涂层表面保护层的厚度。

23.本发明的技术构思:通过选择沉积气体与稀释气体并调节二者的比例,实现在图形层的顶部和侧壁表面、介电质层表面形成均一的保护层,而在开口顶部的有机涂层上很少沉积。这种保护层对图形层的侧壁具有一定的钝化作用,能保护图形层的侧壁,使其不易被溅射到开口内;且侧壁足够厚的保护层可以同时保护图形层底部与介电质层接触的地方不受干扰,减少图形层和介电质层的薄膜损失。开口的顶部很少聚合物沉积,不会干扰小孔刻蚀,能确保选择性地对开口内的有机涂层进行刻蚀;且由于在介电质层表面及图形层表面形成的较厚保护层,可以保证小孔的刻蚀速度,无需为避免薄膜损伤而降低刻蚀的功率和/或刻蚀剂浓度。

24.本发明的有益效果:

25.由于本发明提供的沉积气体与稀释气体形成的保护层在开口顶部及其开口周围的图形层、介电质层表面形成的厚度差异,即,所述图形层侧壁和顶部表面保护层、介电质层表面保护层的厚度均大于所述有机涂层表面保护层的厚度,可实现后续对开口刻蚀工艺中,无需为避免图形层或介电质层的损伤而降低刻蚀功率,从而可以保证开口(小尺寸结构)的刻蚀速度。所以说,本发明提供的工艺方法,兼顾了增加小孔的刻蚀能力和降低介电质层损伤的优点。

附图说明

26.图1为现有技术的一种具有高深宽比小尺寸的有机涂层的小孔刻蚀完成前后状态示意图。

27.图2为本发明的一种半导体器件形成方法流程图。

28.图3为本发明的沉积保护层的反应原理示意图。

29.图4为本发明沉积的保护层在器件中心与边缘的刻蚀速率比较示意图。

30.图5a为本发明的实施例1的半导体器件处理前的截面图;

31.图5b为本发明的实施例1的半导体器件经沉积保护层处理后的截面图;

32.图5c为本发明的实施例1的半导体器件经沉积保护层-刻蚀步骤1个循环处理后的截面图;

33.图5d为本发明的实施例1的半导体器件经沉积保护层-刻蚀步骤2个循环处理后的截面图。

34.图6为本发明的实施例2的半导体器件经本发明的若干次沉积保护层-刻蚀完成前后状态示意图。

35.损失薄膜层11

36.残留有机层12

37.衬底21

38.介电质层22

39.损失层221

40.开口23

41.有机涂层24

42.图形层25

43.保护层26。

具体实施方式

44.下面将结合附图对本发明的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

45.在本发明的描述中,需要说明的是,术语“上”、“下”、“内”、“顶部”、“侧壁”、“底部”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。

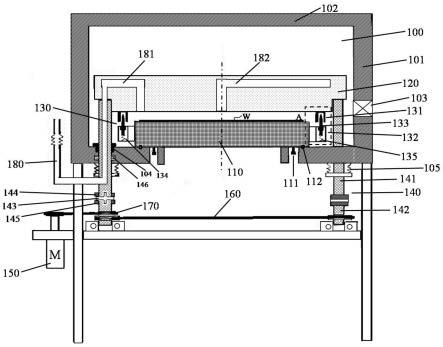

46.如图2所示,本发明提供了一种半导体器件形成方法,其包含:

47.步骤s1,提供一衬底,该衬底上设置有介电质层,该介电质层包含至少一开口,所述的开口内充满有机涂层,至少部分所述介电质层上具有图形层。所述的开口的宽度小于15nm,该开口为高深宽比的小孔。

48.一些实施例中,所述的有机涂层为底部抗反射层。所述的图形层为光刻胶(photoresist,简称pr)。

49.步骤s2,通入沉积气体和稀释气体,在所述的介电质层和所述的有机涂层的表面、以及所述的图形层的侧壁和顶部表面形成保护层,其中,所述图形层的侧壁和顶部表面保护层、介电质层表面保护层的厚度均大于所述有机涂层表面保护层的厚度。

50.沉积形成所述保护层的工艺条件包含:压力为40mt~120mt,射频频率为高频,如可选择50mhz~70mhz,功率为150w~600w,上电极温度为80~120℃,下电极温度为15~30℃。

51.对于开口宽度小于15nm的高深宽比的小尺寸结构,由于尺寸效应,沉积离子很难进入小尺寸开口,不容易在开口顶部形成聚合物沉积,使得聚合物保护层更容易形成在开口附近的图形层、介电质层表面,而不易形成在开口顶部。

52.进一步地,由于曝光面积的缘故,所述的图形层的侧壁和顶部表面保护层的厚度>所述的介电质层表面保护层的厚度>所述的有机涂层表面保护层的厚度。开口顶部的有机涂层表面上形成的聚合物保护层几乎没有。

53.所述的沉积气体为c

xhy

,x=1~5,y=2~8,用于形成保护层。一些实施例中,所述的沉积气体可选择ch4,c2h6和c2h4中的至少一种。

54.所述的稀释气体包括:co和co2中的至少一种。

55.如图3所示,为本发明沉积保护层的反应原理示意图。向反应腔中输入的混合气体c

x1hy1

oz(其中,x1、y1、z分别用于表示c、h、o的原子比例,均为大于0的正数)包含沉积气体c

xhy

及稀释气体co或co2。其中,c

xhy

作为聚合物来源用以沉积聚合物形成保护层,co或co2作为稀释气体并可参与反应:一方面用于调节聚合物沉积使其均匀分布,达到均一性,一方面产生正离子,该正离子具有方向性能促进特定结构(如图形层、介电质层上)里更快的沉积聚合物。本发明还采用ar、n2和he分别作为稀释气体,替代co或co2进行对比实验,结果显示,同等条件下,ar作为稀释气体,导致了更多的介电质层的损失;且ar、n2和he作为稀释气体,均一性均较差。

56.通过调节沉积气体/稀释气体的比例实现图形层(光阻)顶部和侧壁较快的均一的聚合物沉积,而底部(有机涂层上)较慢的聚合物沉积,不会产生刻蚀停止的现象。如稀释气体(如,co)过多,形成的保护层的厚度会变薄,均匀性不可控;如co过少,则成核不均匀,无法起到保护作用。可选的,所述的沉积气体与稀释气体的体积比为1:1~3:1,形成的保护层均一性好,无论是在光片上还是在具有特征图案的芯片上。

57.这种均一性在图4上得到验证:10s的沉积后可以刻蚀15s,甚至可以持续到30s,且持续保持器件中心/边缘均一的刻蚀效果,可见,这种沉积气体/稀释气体具有非常好的沉积效果。进一步地发现,随着功率升高,均一性效果更佳。

58.实施例1

59.如图5a所示,处理前的半导体器件包含:衬底21,衬底上的介电质层22,介电质层设有若干开口23,在介电质层与开口中均旋涂填充有barc有机涂层24,开口周围的介电质层上均设有图形层25,其中,图形层高度为138.5nm,图形层宽度为65.9nm,开口内barc凹陷的尺寸为46.0nm。

60.采用体积比为3:1的ch4/co作为聚合物的前驱体,压力为60mt,射频频率60mhz,功率为300w,上电极温度为80℃,下电极温度为23℃,沉积聚合物形成保护层。

61.沉积10s结果如下:如图5b所示,发现图形层的顶部和侧壁具有相对比较均一的保护层26(图形层高度增厚到157.7nm,增加了19.2nm,图形层25宽度增厚到95.0nm,增加了29.1nm),该保护层保护了图形层的侧壁及顶部;且,图形层的底部,也就是开口的顶部几乎没有沉积聚合物(barc凹陷的尺寸为44.7nm,增加了1.3nm),这对小孔刻蚀带来极大的优势。

62.对上述沉积了保护层的半导体器件进行小孔刻蚀,刻蚀30s后,如图5c所示,图形层25高度为106.5nm(减少了51.2nm),图形层宽度为71.2nm(减少了23.8nm),开口上barc凹

陷的尺寸为86.2nm(刻蚀了41.5nm,相对于形成保护层前刻蚀了40.2nm),可见,图形层的侧壁并没有完全消耗保护层,而开口的顶部已经进行了一定的刻蚀。

63.再一次进行沉积(5s)和刻蚀(20s),如图5d所示,图形层25高度为88.4nm(相对于图5c中的图形层高度又减少了18.1nm),图形层宽度为69.7nm(相对于图5c中的图形层宽度又减少了1.5nm),开口上barc凹陷的尺寸为116.7nm(相对于图5c中的图形层凹陷又刻蚀了30.5nm),可见,图形层的侧壁依然保持合适的厚度,而小孔的刻蚀并没有受到任何干扰,证明均一的聚合物沉积可以很好保护图形层的侧壁而不影响到底下开口的刻蚀。

64.实施例2

65.将衬底21置于等离子刻蚀腔中。如图6的a所示,该衬底21上设置有介电质层22,该介电质层22包含至少一开口23,所述的开口23内充满有机涂层24,部分所述介电质层上具有图形层25。

66.分别通入沉积气体ch4和稀释气体co,二者的流量比为1:1。沉积保护层:压力为40mt,射频频率为60mhz,功率为150w,上电极温度为120℃,下电极温度为30℃。10s后,在所述的介电质层22和所述的有机涂层24的表面、以及图形层25的侧壁和顶部表面的保护层26。其中,位于所述的介电质层22和所述的有机涂层24的表面、以及图形层25的侧壁和顶部表面的保护层26,且所述图形层侧壁和顶部表面保护层、介电质层表面保护层的厚度均大于有机涂层表面保护层的厚度。

67.为了使得后续刻蚀工艺选择性地主要刻蚀开口23内的有机涂层24,其表面上形成的保护层越薄越好。

68.刻蚀15s,由于所述的图形层25的侧壁和顶部形成了较厚的保护层,在离子轰击时,图形层的光阻材料不容易溅射到开口内,减少了刻蚀剂因开口内光阻材料的消耗,从而能提高对开口内有机涂层的刻蚀速率。由于所述的介电质层22的表面形成的保护层较有机涂层上的保护层更厚,刻蚀过程中,所有的有机涂层上的保护层先被刻蚀掉,然后对有机涂层进行刻蚀,由于介电质层22表面上的保护层的阻隔,所述的介电质层较少损失。

69.交替进行上述的沉积保护层步骤及刻蚀步骤,直到开口内的有机涂层完全被刻蚀,如图6的b所示,开口底部无有机涂层残留,介电质层的损失层221较小,图形层的高度和宽度也损失较少。

70.综上所述,本发明提供的方法是在小孔刻蚀前,通过通入沉积气体、稀释气体,在介电质层表面、图形层的侧壁和顶部表面沉积一层聚合物保护层,开口顶部的有机涂层上沉积很少几乎没有,由于保护层的阻挡,可以兼顾增加小孔刻蚀能力并降低介电质层、图形层的薄膜损伤。

71.尽管本发明的内容已经通过上述优选实施例作了详细介绍,但应当认识到上述的描述不应被认为是对本发明的限制。在本领域技术人员阅读了上述内容后,对于本发明的多种修改和替代都将是显而易见的。因此,本发明的保护范围应由所附的权利要求来限定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。