氧化铝层的沉积

本技术是申请号为201711119934.7、申请日为2017年11月14日、发明名称为“氧化铝蚀刻停止层的沉积”的申请的分案申请。

技术领域

1.本发明涉及半导体衬底处理方法。具体地,本发明涉及在集成电路(ic)制造期间在层间电介质(ild)上和在金属上沉积电介质蚀刻停止层的方法。

背景技术:

2.在集成电路制造中,金属线(例如铜线)通常嵌入在ild层中,其中ild通常是基于多孔氧化硅的介电材料或具有低介电常数的有机聚合物介电材料,例如介电常数为2.2或2.2以下的超低-k(ulk)电介质。使用镶嵌工艺形成这样的嵌入金属线需要图案化和蚀刻ild以形成通孔和沟槽,然后用金属(例如铜)例如通过使用电镀来填充这些通孔和沟槽。在通孔和沟槽被金属填充之后,第二ild层被沉积并再次被图案化以形成通孔和沟槽。这些凹陷特征再次用金属填充,使得形成具有嵌入金属线的ild层的堆叠,其中金属线形成集成电路的导电路径。蚀刻停止层通常沉积在单独的ild层和金属线上,并且用于ic制造工艺的图案化操作,以保护这些层下方的材料在图案化期间不被蚀刻。例如,半导体衬底可以包括位于两个ild层之间的蚀刻停止层。当顶部ild层被图案化和蚀刻(例如,使用氟基化学品)来限定通孔和沟槽时,蚀刻停止层保护蚀刻停止点下方的底部ild层不被蚀刻。

3.蚀刻停止层的材料应该相对于被蚀刻的材料显示出良好的蚀刻选择性。换句话说,蚀刻停止层材料应以比暴露的ild材料(或正在被图案化的其它材料)显著更低的速率进行蚀刻。

4.蚀刻停止层通常在集成电路制造期间不被完全去除,并且作为较厚的ild层之间的薄膜保留在最终制造的半导体器件中。常规使用的蚀刻停止层材料的示例包括碳化硅和氮化硅。

技术实现要素:

5.提供了用于形成高质量的氧化铝层的方法、装置和系统。所提供的方法使得能够沉积氧化铝而不引起上面沉积了该氧化铝的金属层的氧化。这是提供的方法的显著优点,因为金属的氧化导致金属线的增加的电阻,并且因此增加不需要的电阻-电容(rc)延迟。此外,通过本文提供的方法沉积的氧化铝材料非常适合用作蚀刻停止层,因为它们的特征在于低介电常数(k)并且具有高密度。对于蚀刻停止层,低介电常数是非常需要的,因为在处理期间没有从半导体器件中完全去除蚀刻停止层,并且最终器件通常在单个ild层之间包含薄的蚀刻停止层。为了最小化金属线之间的串扰并减少rc延迟,重要的是使用具有低介电常数的蚀刻停止材料。然而,许多常规的低k材料通常具有相对于ild材料的相对低的蚀刻选择性。因此,需要具有低介电常数和高蚀刻选择性的材料。蚀刻选择性是与材料密度正相关的特性。因此,期望同时具有低介电常数和高密度的材料。

6.根据一些实施方式,通过本文提供的方法沉积的氧化铝材料的特征在于介电常数小于约7,例如介于约4-6之间,密度至少为约2.5g/cm3,例如介于约3.0-3.2g/cm3之间(例如,介于约2.6-3.2g/cm3之间)。成形膜的示例包括介电常数小于约6并且密度至少约2.8g/cm3的膜。在一些实现方案中,形成介电常数为约4-6且密度为约3.0-3.2g/cm3的氧化铝膜。

7.根据一个方面,提供了一种用于处理半导体衬底的方法。所述方法包括:提供包含暴露的介电层(例如ulk介电层)和暴露的金属层的半导体衬底;以及通过使含铝前体与选自醇和烷氧基铝的反应物反应在所述介电层和所述金属层之上形成氧化铝蚀刻停止膜并且所述氧化铝蚀刻停止膜接触所述介电层且接触所述金属层,其中所形成的所述氧化铝蚀刻停止膜具有小于约7的介电常数和至少约2.5g/cm3的密度。在一些实施方式中,所述蚀刻停止膜形成介于约10-100埃之间的厚度,例如介于约20-50埃之间的厚度。

8.各种金属可以在暴露的金属层中。在一些实施方式中,金属选自铜、钴和钨,并且氧化铝的沉积不会导致在金属和氧化铝之间的界面处形成金属氧化物。在一些实施方式中,金属是钴,并且在氧化铝沉积时没有形成可通过x射线光电子能谱(xps)检测到的co-o键。

9.在一些实施方式中,形成氧化铝蚀刻停止膜包括使含铝前体与含有至少四个碳原子的醇反应。例如,在一个实现方式中,通过使三甲基铝(tma)与叔丁醇反应而形成高质量的氧化铝蚀刻停止膜。与使用具有较少碳原子的更具反应性的醇相比,使用具有至少四个碳原子的醇使得能实现对反应的改进的控制。

10.在一些实施方式中,所述氧化铝蚀刻停止膜通过基本上在所述半导体衬底的表面上发生的反应形成。在其他实施方式中,所述氧化铝蚀刻停止膜通过基本上在所述半导体衬底的表面外发生的反应形成。

11.在一种实现方式中,形成所述氧化铝蚀刻停止膜包括:(i)在容纳所述半导体衬底的处理室中,(例如通过使三烷基铝流至所述处理室持续约0.1-10秒)使所述含铝前体吸附到所述半导体衬底的表面,其中所述含铝前体是三烷基铝;(ii)在所述含铝前体已被吸附之后,清扫和/或排空所述处理室;(iii)在清扫后,向所述处理室提供具有至少四个碳原子的醇(例如通过使醇流至所述处理室持续约0.1-10秒),并使所述醇与所吸附的含铝前体反应且形成氧化铝;(iv)在所述反应后,清扫和/或排空所述处理室;以及(v)重复(i)-(iv)。在一些实施方式中,步骤(i)-(iv)重复至少三次。优选地,在(iii)中三烷基铝和醇之间的反应在不存在等离子体的情况下进行。在一些实施方式中,所述氧化铝蚀刻停止膜在介于约50-400℃之间的温度下以及在介于约0.5-8托之间的压强下形成。在一个优选实施方式中,三烷基铝是tma,并且醇是叔丁醇。

12.在一些实施方式中,所述半导体衬底处理方法还包括:将光致抗蚀剂施加到所述半导体衬底;使所述光致抗蚀剂暴露于光;图案化所述光致抗蚀剂并将所述图案转移到所述半导体衬底;以及选择性地从所述半导体衬底去除所述光致抗蚀剂。在一些实施方式中,所述半导体衬底处理方法还包括在所述氧化铝层上沉积介电层,以及在暴露的蚀刻停止层的存在下在所沉积的所述介电层中蚀刻凹陷特征。在一些实施方式中,在已经形成所述凹陷特征之后(至少部分地)去除所述氧化铝蚀刻停止层。

13.根据另一方面,提供了一种用于沉积氧化铝蚀刻停止膜的装置。在一个实施方式中,该装置包括具有用于保持半导体衬底的支撑件和控制器的处理室。控制器包括用于进

行本文提供的任何沉积方法的程序指令。在一些实施方式中,控制器被编程为:通过使含铝前体与选自醇和烷氧基铝的反应物反应,在介电层和金属层上形成氧化铝蚀刻停止膜,并且氧化铝蚀刻停止膜接触介电层和金属层,其中所形成的氧化铝蚀刻停止膜具有小于约7的介电常数和至少约2.5g/cm3的密度。程序指令可以包括用于以下操作的指令:(a)将含铝前体和醇或烷氧基铝引入(例如,顺序地引入)到处理室中;和(b)让它们反应并在衬底上形成氧化铝蚀刻停止膜。

14.在一些实施方式中,所述装置包括构造成将含铝前体输送到所述处理室的第一管道;以及构造成将醇或烷氧基铝输送到所述处理室的第二管道,其中所述第一和第二管道是不同的管道。

15.根据另一方面,本文提供了一种系统,其包括用于沉积氧化铝蚀刻停止膜和步进机(stepper)的沉积装置。

16.根据另一方面,提供了一种非暂时性计算机机器可读介质。它包括用于控制沉积装置的程序指令。所述指令包括用于本文提供的沉积方法的代码。在一些实施方式中,提供了用于以下操作的代码:(a)将含铝前体和醇(或醇氧基铝)引入(例如,顺序地引入)到处理室中;和(b)让它们反应并在半导体衬底上形成氧化铝蚀刻停止膜。

17.根据另一个方面,提供了一种半导体器件,其包含氧化铝蚀刻停止膜,其中所述氧化铝蚀刻停止膜具有介于约10-50埃之间的厚度,并且其特征在于介电常数小于约6,密度至少约2.8g/cm3,其中所述氧化铝与金属层保持接触,并且其中所述金属层没有显示氧化的迹象。

18.本发明的这些和其它特征和优点在下文参照相关附图进行更详细地描述。

附图说明

19.图1a-1c根据本文提供的实施方式示出了在处理过程中半导体衬底的横截面图,其中示出了蚀刻停止膜。

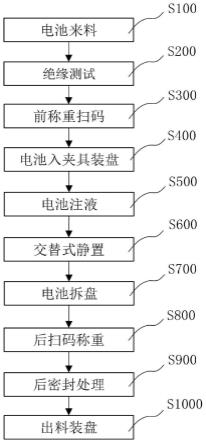

20.图2是本文提供的处理方法的工艺流程图。

21.图3是根据本文提供的实施方式的沉积氧化铝蚀刻停止膜的方法的工艺流程图。

22.图4是根据本文提供的实施方式的可用于沉积氧化铝膜的ald处理站的示意图。

23.图5示出了根据本文提供的实施方式的多站处理工具的示意图。

24.图6是根据本文提供的实施方式的被配置用于沉积薄膜的处理工具的框图。

25.图7a是根据本文的方法沉积氧化铝膜沉积后的钴层的实验xps图。

26.图7b是沉积比较的含铝膜之后的钴层的实验xps图,其示出了钴的氧化。

具体实施方式

27.在以下的详细描述中,阐述了许多具体细节以提供对所公开的实现方式的充分理解。然而,对于本领域技术人员而言,显而易见,所公开的实现方式可以在没有这些具体细节的情况下或者通过使用替代的元件或者工艺实施。在其他示例中,未详细描述公知的工艺、程序和部件,以避免不必要地模糊所公开的实施方式的方面。

28.在本技术中,术语“半导体晶片”、“半导体衬底”、“晶片”、“衬底”、“晶片衬底”和“部分制造的集成电路”可互换使用。本领域的普通技术人员应理解,术语“部分制造的集成

电路”可以指在其上面进行集成电路制造的许多阶段中的任何阶段期间的硅晶片。下面的详细描述描述了在晶片上的界面层的沉积。然而,所公开的实现方式并不限于此。工件可以是各种形状、尺寸和材料。除了半导体晶片之外,可以利用所公开的实现方式的优点的其它工件还包括诸如印刷电路板等各种制品。本文所用的术语“半导体晶片”或“半导体衬底”是指在其主体内任何地方都具有半导体材料的衬底,并且可以理解,半导体材料不需要暴露。在许多实施方式中,半导体衬底包括形成在半导体材料上的一个或多个介电层和导电层。

29.本文提供的氧化铝膜包含al和o。尽管在一些实施方式中可能存在其它元素,但是在许多说明性实施方式中,膜基本上由al和o组成,并且不包含多于5原子%的其它元素(例如,不含有5原子%以上的碳,不含有5原子%以上的氢)。在这些示例性实施方式中,铝与氧的原子比为约2至3。意外地发现本文提供的沉积方法可用于在金属表面(例如,钴或铜表面)上沉积氧化铝而不在金属和氧化铝之间的界面处形成金属氧化物。这一发现是出人意料的,因为诸如铜和钴等金属非常容易形成氧化物,并且由于通过不同的方法沉积基于氧化铝的膜会显示出导致这样的不希望有的铜和钴氧化。

30.本文提供的氧化铝膜是高质量的膜,其中高质量是指高密度和低介电常数的组合。具体地,本文提供的膜具有小于约7的介电常数和至少约2.5g/cm3的密度。在一些实施方式中,这些膜具有小于约6的介电常数和至少约2.8g/cm3的密度。在一些实施方式中,提供介电常数为约4-6并且密度为约3.0g/cm

3-3.2g/cm3的氧化铝膜。此外,在一些实施方式中,所提供的膜的特征在于大于约8mv/cm的击穿电压,例如至少约9mv/cm,或至少约11mv/cm的击穿电压。这些膜表现出对钴的良好粘合性,从而表明形成了al-o-co键。对铜的粘附性也被证明是好的。发现根据一些实施方式提供的膜具有特性(没有金属氧化、对金属的强粘附性、高密度、低介电常数和高击穿电压)的独特组合,这使得它们非常适合用作蚀刻停止层。

31.本文提供的氧化铝膜通常作为介电层之间和/或金属层与介电层之间的薄界面层沉积。在一些实施方式中,膜位于包含金属(例如铜、钴或钨)与ulk电介质的层和扩散阻挡材料层(例如,掺杂或未掺杂的碳化硅层或掺杂或未掺杂的氮化硅层)之间的界面处。所提供的层的厚度为约10-200埃,更典型地为约10-100埃,例如约20-50埃。

32.在一些实施方式中,提供了半导体器件,其中半导体器件包括两层ild(例如,ulk电介质)和位于两层ild之间的提供的氧化铝膜的薄层(例如,在约之间,例如约)。ild层还可以包括嵌入的金属(例如铜、钨或钴)线,并且在一些实施方式中,薄氧化铝膜也位于金属和ild之间(例如,ulk电介质),同时接触ild和金属两者。有利地,在一些实施方式中,在金属层和氧化铝层之间的界面处不存在通过xps或反射计可检测到的金属氧化物。在一些实施方式中,该器件包含介于钴和氧化铝之间的界面。

33.所提供的氧化铝膜特别适合用作蚀刻停止层,但也可用作各种目的的界面层(例如,以改善电迁移阻力或作为硬掩模)。

34.通常,所提供的膜可以沉积在平坦的或者在图案化的衬底上。在一种实施方式中,所提供的膜沉积在位于具有包括暴露的电介质和金属(例如铜、钴或钨)两者的暴露的平坦表面的半导体衬底上。

35.图1a-1c提供了经历几个步骤的双镶嵌处理的半导体衬底的示例,其中可以使用所提供的氧化铝膜。参考图1a,示出了用于双镶嵌制造的部分制造的集成电路(ic)结构100

的示例。如图1a-1c所示,结构100是半导体衬底的一部分,并且在一些实施方式中可以直接驻留在包含有源器件(例如晶体管)的层上。在其它实施方式中,它可以直接驻留在金属化层上或包含导电材料的其他层上,例如在含有存储电容器的层上。

36.图1a所示的层103是层间介电层,其可以是二氧化硅,但更典型地是低k介电材料。为了使金属间电介质堆叠的介电常数最小化,k值小于约3.5,优选小于约3.0且经常小于约2.8的材料被用作层间电介质。这些材料包括但不限于掺杂氟或碳的二氧化硅(例如,sicoh)、有机低k材料和多孔掺杂二氧化硅材料。这种材料可以例如通过等离子体增强化学气相沉积(pecvd)或通过旋涂方法沉积。在一些实施方式中,层103包含ulk电介质。层103被蚀刻有线路径(沟槽和通孔),在线路径中沉积部分导电的金属扩散阻挡层105,然后用铜导电路线107嵌入。在其它实施方式中,使用不同于铜的金属(例如,钴或钨)。由于铜或其他可移动导电材料提供了半导体衬底的导电路径,所以必须保护靠近金属线的下伏的硅器件和介电层免受金属离子(例如,cu

2

)的影响,否则这些金属离子(例如,cu

2

)可能会扩散或漂移到硅或层间电介质内,并导致其性能的降低。为了保护ic器件的介电层,使用了几种类型的金属扩散阻挡层。这些类型可以分为部分导电的含金属层,例如105和介电阻挡层。用于部分导电扩散阻挡层105的合适材料包括诸如钽、氮化钽、钛、氮化钛等材料。这些通常通过物理气相沉积(pvd)或原子层沉积(ald)方法共形沉积到具有通孔和沟槽的介电层上。

37.可以在通过包括pvd、电镀、无电沉积、化学气相沉积(cvd)等多种技术沉积扩散阻挡层105之后,形成铜导电路线107。在一些实现方式中,形成铜填充物的优选方法包括通过pvd沉积薄的铜晶种层,随后通过电镀沉积主体铜填充物。由于通常沉积铜会形成位于场区域的覆盖层,因此需要进行化学机械抛光(cmp)操作来去除覆盖层并获得平坦化结构100。如上所述,在一些实施方式中,导电路线107由钨或钴制成,其可以例如通过cvd或ald(其中cvd和ald可以是热或等离子体辅助的)沉积。

38.接下来,参考图1b,在结构100完成之后,提供的氧化铝蚀刻停止膜109使用本文提供的方法沉积到铜线107和电介质103上。有利的是,在铜线107与氧化铝蚀刻停止膜109之间的界面处,该沉积方法不会引起铜氧化物的形成(当钴和钨用于金属线中时,也不会引起钴和钨氧化物的形成)。

39.应注意,在一些实施方式中,ild层103的顶部(其上面沉积了层109)可以与该层109的主体部分不同。例如,在一些实施方式中,层103的顶部比该主体部分在机械上较稳固。在一种实现方式中,层103的顶部是机械稳固的经掺杂或未经掺杂的碳化硅或氮化硅,而介电层103的主体部分是更精密的ulk电介质(例如,多孔材料)。在一个示例中,层103的顶部是掺杂氧的碳化硅(odc)。存在这种更稳固的层使得使用等离子体步骤沉积蚀刻停止膜更容易,而不损坏衬底的暴露部分。

40.在一些实施方式中,氧化铝蚀刻层109在其位于制造的结构中的铜和电介质之间的界面时还用作电介质扩散阻挡层。在一些实施方式中,单独的扩散阻挡层沉积在层109的顶部上。通常,这种扩散阻挡层(未示出)包括掺杂或未掺杂的碳化硅(例如,碳氧化硅)或氮化硅。

41.参考图1b,将双镶嵌介电结构的第一介电层111沉积到氧化铝蚀刻停止膜109上。其后在第一介电层111上沉积蚀刻停止膜113。蚀刻停止膜113可以是本文提供的氧化铝蚀刻停止膜,或者其可以包含不同的蚀刻停止材料。介电层111通常包含低k电介质材料,诸如

为介电层103列出的那些低k介电材料,并且还可以包括机械上更稳固的顶部(例如,包含odc的顶部)。注意,层111和103不一定具有相同的组成。在一些实施方式中,层111和103均为ulk介电层。

42.工艺继续,如图1c所示,其中双镶嵌介电结构的第二介电层115以类似于沉积第一介电层111的方式沉积到蚀刻停止膜113上。然后沉积抗反射层(未示出)和cmp停止膜117。第二介电层115通常包含低k介电材料,例如上面针对层103和111描述的那些,并且可以任选地包括机械上更稳固的顶部部分。cmp停止膜117用于在随后的cmp操作期间保护层间介电层115的精细介电材料。通常,cmp停止层经历与蚀刻停止膜109和113相似的集成要求,并且可以包括本文提供的氧化铝膜。替代地,其可以包含基于碳化硅或氮化硅的常规cmp停止材料。

43.在随后的操作期间,图案化ild层111和115以形成凹陷特征(通孔和沟槽)。图案化通常使用常规光刻技术进行,并且涉及将光致抗蚀剂施加到衬底上,使光致抗蚀剂暴露于光,图案化光致抗蚀剂并且通过通常使用基于氟的化学品蚀刻介电材料而将图案转移到衬底,以及去除光致抗蚀剂。提供的氧化铝蚀刻停止膜相对于ild电介质(例如,ulk电介质和/或odc)具有良好的蚀刻选择性,并保护位于蚀刻停止层下方的材料不被蚀刻。在一些实施方式中,在暴露的蚀刻停止氧化铝膜119存在下,使用基于氟的化学品(例如,使用c4f8、cf4、o2和氩在等离子体中的混合物)蚀刻介电层111(例如,sicoh层),从而保护下伏层。必要时(例如,在电介质蚀刻完成之后),可以通过湿式蚀刻去除氧化铝蚀刻停止膜的暴露部分。用于氧化铝去除的湿式蚀刻组合物的示例包括氨与过氧化氢的混合物和溴与甲醇的混合物。

44.应注意,所提供的氧化铝蚀刻停止膜可以在各种不同的集成方案中使用,并且它们的用途不限于图1a-1c所示的方案。因为钴特别易于氧化,所以在含有钴线的衬底上使用所提供的膜是特别有利的,因此,允许在钴上形成蚀刻停止膜而不引起钴氧化的方法是非常有价值的。

45.在图2中提供了利用氧化铝蚀刻停止层的处理方法的工艺流程图。该工艺从201开始,在201,提供具有暴露的金属层和暴露的介电层的半导体衬底。例如,衬底可以包括暴露的ulk介电层和暴露的金属层,例如铜、钨或钴层。图1a中示出了这种衬底的一个示例。接下来,在203中,氧化铝蚀刻停止膜沉积在衬底上。通过使含铝的前体(例如三烷基铝)与醇或烷氧基铝反应来进行沉积,从而在反应中形成氧化铝。通常,反应可以使用各种方法(例如cvd和ald)进行。在一些实施方式中,优选基本上在衬底的表面上进行反应,从而使得能对所形成的层的厚度进行高水平的控制。在其他实施方式中,反应基本上在衬底的表面之外进行,例如在cvd模式中在处理室的主体部分(bulk)中进行。反应通常在不使用等离子体的情况下进行。然而,等离子体处理可以在氧化铝膜已经沉积之后使用,以提高膜的质量。

46.在一种实施方式中,氧化铝蚀刻停止膜的沉积包括向处理室提供含铝前体和醇(或烷氧基铝),并且配置用于将氧化铝膜沉积在衬底上的工艺条件。合适的挥发性含铝前体包括但不限于有机铝化合物,例如三甲基铝(tma)、二甲基氢化铝、三乙基铝、三异丁基铝和三(二乙基氨基)铝。在一些实施方式中,卤化铝(例如alcl3)可以用作含铝前体。在许多实施方式中,三烷基铝(例如tma)是优选的前体。醇的示例包括甲醇、乙醇、丙醇(例如正丙醇或异丙醇)和丁醇(例如叔丁醇)。在一些实施方式中,优选具有至少四个碳原子的醇(特别是当含铝前体是tma时),因为它们的反应性低于低级醇,并且反应可以更容易控制,这在

需要沉积具有限定厚度的非常薄的膜时是有利的。丁醇(特别是叔丁醇)是特别优选的,因为它们比低级醇的反应性低,并且允许良好的反应控制,但同时它们具有足够的挥发性并且可以在真空室中容易地处理。在优选实施方式之一中,使用tma与叔丁醇的反应形成氧化铝。

47.合适的烷氧基铝的示例包括乙醇铝(oet)3和异丙醇铝al(oipr)3。例如,氧化铝膜可以通过使tma与异丙烷氧基铝反应,或者通过经由ald使alcl3与异丙醇铝或乙醇铝反应来沉积。

48.在一些实施方式中,前体和反应物的引入是连续的。在一些实施方式中,反应主要发生在衬底的表面上,并且抑制或不允许在处理室的主体部分中前体和反应物的混合。在其它实施方式中,允许在处理室的主体部分中前体和反应物的混合,并且反应可以在衬底的表面上并且在处理室的体积中的主体部分中发生。

49.在一些实施方式中,通过基于表面的反应(ald)和来自处理室的主体部分的沉积(cvd)的组合来沉积氧化铝膜。例如,如果在每个吸附步骤之后前体不能从处理室中完全除去,则可能发生基于表面的反应和来自主体部分的沉积两者。

50.在一些实施方式中,沉积在介于约50-400℃之间的温度范围和介于约0.5-8托之间的压强下进行。含铝前体和醇(或烷氧基铝)的流速将取决于处理室的尺寸,并且在一些实施方式中在约10-20000sccm的范围内。当含铝前体和醇(或烷氧基铝)依次投配(dose)时,在一些实施方式中,每一者都流到处理室持续介于约0.1-10秒之间。

51.再次参考图2的工艺流程图,在沉积氧化铝蚀刻停止膜之后,该工艺接着如下:可选地,在氧化铝蚀刻停止膜上沉积介电扩散阻挡层并与介电扩散阻挡层接触,如205所示。扩散阻挡膜可以是例如通过pecvd沉积的掺杂氧的碳化硅层。

52.接下来,在操作207中,ild层沉积在蚀刻停止层和可选的扩散阻挡膜上。然后在选择的位置(在标准光刻图案化之后)蚀刻ild层以形成凹陷特征。在通常使用氟基化学品进行的蚀刻期间,氧化铝膜保护蚀刻停止层之下的材料不被蚀刻。

53.在图3中示出了氧化铝蚀刻停止膜的沉积的示例性工艺之一。该工艺包括将半导体衬底放置在处理室中(例如,在ald处理室中),并且在操作301中提供含铝的前体(例如,tma)到处理室。在一些实施方式中,将含铝前体用载气(如n2或惰性气体)提供给处理室。该步骤中的温度和压强被选择为使得含铝前体能吸附在衬底表面上。接下来,在操作303中,处理室被清扫和/或排空以从处理室去除未吸附的含铝前体。在一些实施方式中,去除基本上是完全的。在其它实施方式中,一部分含铝前体会保留在处理室中。该工艺在305继续,在305中,提供醇(例如叔丁醇)或烷氧基铝(例如异丙醇铝)到处理室。利用诸如n2或惰性气体之类的载气来提供(气化形式的)醇。重要的是,在一些实施方式中,含铝前体和醇(或烷氧基铝)通过分离的管道被引入处理室,使得在输送到处理室期间不会发生这些前体的混合。使醇或烷氧基铝能在衬底的表面上反应。在该所示的实施方式中,反应基本上在衬底的表面上发生(例如,在表面上的反应中形成了超过50%的氧化铝)。在其它实施方式中,反应基本上可能发生在衬底表面之外(例如,超过50%的氧化铝在处理室的主体部分中形成,然后沉积在衬底上)。

54.接下来,在307中,处理室被清扫和/或排空以除去反应产物。通常,操作301-307的一个循环在衬底上形成平均厚度在约0.2-3埃之间的氧化铝膜。在操作311中确定是否需要

进一步沉积。如果该层不够厚,则重复操作301-309,直到形成所需厚度的氧化铝膜。通常,沉积工艺包括将操作301-309循环执行至少4次,例如至少5次,例如介于约5次-20次之间。通常,沉积的蚀刻停止膜的厚度在约10埃-100埃之间,例如在约20埃-100埃之间,例如约30埃。

55.用于根据图3所示方法沉积氧化铝膜的合适的工艺条件提供在表1中。表1:用于沉积氧化铝膜的说明性工艺条件

56.注意,虽然沉积反应通常在不存在等离子体的情况下进行,但在一些实施方式中,所形成的氧化铝膜在沉积后进行等离子体处理。

57.在几个实验验证的示例中,根据图3所示的方法,使用tma和叔丁醇作为反应物沉积氧化铝膜。在ald处理室中,在250-350℃的温度下,在1托的压强下进行沉积,其中tma和叔丁醇分别依次投配5秒。发现得到的氧化铝膜具有高密度(3.0-3.2g/cm3)和低介电常数(4-6)的优异组合。当氧化铝膜沉积在铜上时,通过反射率测量没有观察到铜的氧化。当氧化铝膜沉积在钴上时,通过xps没有观察到钴的氧化。这是令人惊奇的结果,因为铜,特别是钴,非常易于氧化,并且通过不同的方法(使用tma剂量,然后在co2中进行等离子体处理)沉积的基于氧化铝的膜的形成显示出铜和钴的氧化。此外,所提供的氧化铝膜的特征在于大于11mv/cm的击穿电压,并且在4mv/cm下具有约5

·

10-9

amp/cm2的相对低的漏电流。发现实验获得的膜基本上不含氢和碳(每种含量小于5原子%),铝与氧的比率为约2:3。

58.此外,实验获得的膜对铜和钴表现出良好的粘附性,并且在退火时稳定。在氩气气氛中,膜在400℃退火2小时后,未观察到对下伏的铜层的损坏。所提供的膜与aln膜相比是较好的,因为它们比aln膜会具有较高的密度(大于3.0g/cm3,而相比之下,对于aln膜为约2.7g/cm3)。进一步提供的膜与通过其它方法沉积的许多氧化铝膜相比是较好的,因为它们表现出非常低的介电常数(例如,k为4-6,而相比之下,对比氧化铝膜中观察到的k大于7),并且可以沉积在金属上而不引起氧化性的损坏。装置

59.本文公开的实施方式的另一方面是配置成完成本文所述方法的装置。合适的装置包括用于完成处理操作的硬件和具有根据所公开的实现方式来控制处理操作的指令的系统控制器。在一些实施方式中,该装置包括具有用于执行图2或图3中提供的方法步骤的程

序指令的系统控制器。

60.用于完成沉积工艺操作的硬件包括ald(包括iald)处理室和cvd(包括pecvd)处理室。在一些实施方式中,提供的方法的所有操作在单个处理室中执行。在其他实现方式中,衬底可以从室传送到室以执行方法的不同步骤。系统控制器通常将包括一个或多个存储器设备和配置成执行指令的一个或多个处理器,使得装置将根据所公开的实现方式执行方法。包含用于根据所公开的实现方式来控制工艺操作的指令的机器可读介质可以耦合到系统控制器。

61.在一些实施方式中,沉积在iald反应器中进行,该iald反应器是可从lam research corp.(fremont,ca)获得的vector excel沉积模块的一部分。虽然所示的装置具有等离子体形成的能力,其例如可以用于形成的氧化铝层的等离子体后处理,但是,应注意,形成氧化铝层不需要等离子体,并且也可以使用没有等离子体发生器的装置。

62.合适的处理室包括用于在沉积期间保持晶片衬底的支撑件(晶片基座),以及用于将含铝前体和醇(或烷氧基铝)输送到处理室的管道。在一些实施方式中,这些管道是分离的管道,其中每个管道分别与含铝前体的源和醇(或烷氧基铝)的源连接。在一些实施方式中,管道连接成使得含铝前体和醇(或醇铝)不能在管道内(例如,在输送管线内)混合。该装置进一步构造成用于清扫和/或排空处理室,并且用于在沉积期间保持处理室中所需的压强和温度。

63.美国专利no.6,416,822,美国专利no.6,428,859和美国专利no.8,747,964中描述了iald处理室的示例,其全部内容通过引用并入本文。

64.图4示意性地示出了可用于使用原子层沉积(ald)沉积所提供的膜的处理站400的一种实施方式。所示装置具有形成等离子体的能力,并且可以用于热ald模式和离子诱导的iald模式两者。在所提供的工艺中,等离子体处理在氧化铝沉积期间不使用,但可以在氧化铝膜沉积之后使用。

65.为了简化起见,处理站400被描述成具有用于维持低压环境的处理室主体402的独立处理站。然而,应理解,多个处理站400可被包括在共同的处理工具环境中。进一步地,应理解,在一些实施方式中,处理站400的包括在下文详细讨论的那些硬件参数在内的一个或多个硬件参数可以通过编程由一个或多个计算机控制器进行调整。

66.处理站400与反应物输送系统401流体连通,以将工艺气体输送到分配喷头406。反应物输送系统401包括用于混合和/或调节工艺气体以输送到喷头406的混合容器404。一个或多个混合容器入口阀420可控制工艺气体向混合容器404的导入。类似地,喷头入口阀405可控制工艺气体向喷头406的导入。

67.一些反应物可以在汽化前以液体形式存储,随后输送到处理站。例如,图4的实施方式包括用于汽化待供应到混合容器404的液体反应物的汽化点403。在一些实施方式中,汽化点403可以是加热蒸发器。从这样的蒸发器中产生的反应物气相可能在下游输送管路中凝结。将不相容的气体暴露于凝结的反应物会产生小颗粒。这些小颗粒会堵塞管路,妨碍阀的操作,污染衬底等。解决这些问题的一些方法涉及打扫和/或排空输送管路,以去除残留的反应物。然而,打扫输送管路可能会增加处理站的循环时间,降低处理站的吞吐量。因此,在一些实施方式中,汽化点403下游的输送管路也可以进行热跟踪。在一些示例中,混合容器404也可以进行热跟踪。在一个非限制性的示例中,汽化点403下游的管路具有从约100

℃到在混合容器404处的约150℃的升高的温度分布。

68.在一些实施方式中,反应物液体可在液体注射器处被汽化。例如,液体注射器可将脉冲的液体反应物注入到混合容器上游的载气流中。在一种情况下,液体注射器可通过从高压到低压闪蒸液体来汽化反应物。在另一种情况下,液体注射器可将液体雾化成分散的微滴,这些微滴随后在加热的输送管路中汽化。应该理解的是,稍小的液滴会比稍大的液滴汽化更快,从而减小在液体注入和完全汽化之间的延迟。更快的汽化可以减小汽化点403下游的管路的长度。在一种情况下,液体注射器可直接安装到混合容器404上。在另一种情况下,液体注射器可直接安装到喷头406上。

69.在一些实施方式中,可以在汽化点403上游提供液体流量控制器,以控制用于汽化并输送到处理站400的液体的质量流量。例如,液体流量控制器(lfc)可包括位于lfc下游的热质量流量计(mfm)。然后,可响应反馈控制信号调节lfc的柱塞阀,该反馈控制信号是由与mfm电通信的比例-积分-微分(pid)控制器提供的。然而,使用反馈控制以稳定液流可能需要一秒或更长时间。这可以延长投配液体反应物的时间。因此,在一些实施方式中,lfc可以在反馈控制模式和直接控制模式之间动态切换。在一些实施方式中,lfc可以通过禁用lfc和pid控制器的感测管而动态地从反馈控制模式切换到直接控制模式。

70.在一些实施方式中,为了避免含铝前体与醇(或烷氧基铝)的混合,使用分离的管道436和434将含铝前体430的源和含硅前体432的源分别连接到达喷头,以确保将这些前体分离地输送到处理室。含铝前体和醇(或烷氧基铝)可以分开与载气混合并蒸发(如果需要)。

71.喷头406朝向衬底412分配工艺气体。在图4所示的实施方式中,衬底412位于喷头406的下方,并示为搁置在基座408上。应该理解的是,喷头406可具有任何合适的形状,并且可以具有任何合适的数量和端口配置,以将工艺气体分配到衬底412。

72.在一些实施方式中,微体积407位于喷头406下面。在微体积中而不是在处理站的整个体积中执行ald工艺可以减少反应物暴露和打扫时间,可以减少用于改变工艺条件(如,压强、温度等)的次数,可限制处理站机械手暴露于工艺气体,等等。示例的微体积尺寸包括但不限于在0.1升和2升之间的体积。这种微量体积也会影响生产率。当每个循环的沉积速率下降时,循环时间也同时减少。在某些情况下,后者的影响足够大,以提高给定目标厚度膜的模块的整体吞吐量。

73.在一些实施方式中,基座408可以被升高或降低,以将衬底412暴露于微体积407和/或改变微体积407的体积。例如,在衬底转移阶段,基座408可被降低,以使得衬底412能被装载到基座408上。在沉积工艺阶段期间,基座408可被升高,以将衬底412定位在微体积407内。在一些实施方式中,微体积407可以完全包围衬底412以及基座408的一部分,以在沉积工艺期间创建有高流动阻抗的区域。

74.可选地,基座408可在沉积工艺的部分期间降低和/或升高,以调节微体积407内的工艺压强、反应物浓度等。在处理室主体402在沉积工艺期间保持基本压强的一种情况下,降低基座408可使得微体积407能被排空。微体积与室容积的比例的示例包括但不限于在1:900和1:10之间的体积比。应当理解的是,在一些实施方式中,基座高度可以由合适的计算机控制器通过编程进行调整。

75.在另一种情况下,调整基座408的高度可以使得等离子体密度能在包括于沉积工

艺内的等离子体活化和/或处理循环期间变化。在沉积工艺阶段结束时,基座408可在另一个衬底转移阶段期间被降低,以使得能从基座408去除衬底412。

76.虽然在此描述的示例性的微体积变化涉及高度可调的基座,但应理解的是,在一些实施方式中,喷头406的位置可以相对于基座408被调整,以改变微体积407的体积。此外,应当理解,基座408和/或喷头406的竖直位置可以通过在本公开的范围内的任何合适的机制来改变。在一些实施方式中,基座408可以包括用于旋转衬底412的方向的旋转轴。应当理解的是,在一些实施方式中,这些示例性调整中的一个或多个可以由一个或多个合适的计算机控制器通过编程来执行。

77.返回到图4中所示的实施方式。喷头406和基座408电连通rf功率414和匹配网络416,以便为等离子体提供功率。在一些实施方式中,等离子体的能量可通过控制处理站的压强、气体浓度、rf源功率、射频源频率和等离子体功率脉冲时序中的一个或多个进行控制。例如,rf功率源414和匹配网络416可在任何合适的功率下操作,以形成具有期望的自由基物质组合物的等离子体。合适的功率的示例包括在上文内。同样地,rf功率源414可以提供任何适当频率的rf功率。在一些实施方式中,rf功率源414可被配置为彼此独立地控制高频rf功率和低频rf功率。低频rf频率的示例可以包括但不限于在50khz和900khz之间的频率。高频rf频率的示例可以包括但不限于在1.8mhz和2.45ghz之间的频率。应当理解,任何合适的参数都可以被离散地或连续地调节,以便为表面反应提供等离子体能量。在一个非限制性的实例中,等离子体功率可以间歇脉冲化,以相对于连续被激励的等离子体减少对衬底表面的离子轰击。

78.在一些实施方式中,等离子体可由一个或多个等离子体监控器原位监控。在一种情形中,等离子体功率可通过一个或一个以上的电压、电流传感器(例如,vi探针)进行监控。在另一种情况下,等离子体密度和/或工艺气体的浓度可以由一个或多个光发射谱(oes)传感器来测量。在一些实施方式中,一个或多个等离子体参数可基于来自这样的原位等离子体监控器的测量结果通过编程方式进行调节。例如,oes传感器可用于反馈回路中以提供对等离子体功率的编程式控制。应理解的是,在一些实施方式中,可使用其它监控器来监控等离子体和其它工艺特性。这样的监控器可包括,但不限于,红外(ir)监控器、声学监控器、以及压力传感器。

79.在一些实施方式中,可以经由输入/输出控制(ioc)测序指令来控制等离子体。在一个示例中,用于设置用于等离子体处理阶段的等离子条件的指令可被包括在沉积工艺配方的相应的等离子体激活配方阶段中。在某些情况下,工艺配方阶段可按顺序排列,使得用于沉积工艺阶段的所有指令与该工艺阶段同步执行。在一些实施方式中,用于设定一个或一个以上的等离子体参数的指令可以被包括在等离子体工艺阶段之前的配方阶段中。例如,第一配方阶段可以包括用于设置惰性气体和/或反应物气体的流率的指令、用于设置等离子体发生器至功率设定点的指令、以及用于第一配方阶段的时延指令。后续的第二配方阶段可包括用于启用等离子体发生器的指令以及用于第二配方的时延指令。第三配方阶段可以包括用于禁用等离子体发生器的指令以及用于第三配方的时延指令。应当理解,这些配方可进一步以在本公开的范围内的任何合适的方式细分和/或重复。

80.在一些沉积工艺中,等离子体激励持续几秒钟的数量级或更长的持续时间。在某些实现方式中,可使用短得多的等离子体激励。这些可以是从10毫秒到1秒的量级,通常约

20毫秒至80毫秒,50毫秒是一个具体的示例。如此很短的射频等离子体激励要求等离子体的极端快速稳定。为了实现这一点,等离子体发生器可以被配置为使得阻抗匹配被预设为特定电压,而频率被允许浮动。按惯例,高频等离子体是在约13.56mhz的rf频率下产生的。在本文公开的各种实施方式中,频率被允许浮动到与这个标准值不同的值。通过允许频率浮动而同时将阻抗匹配固定到预定电压,等离子体可以远远更迅速地稳定,结果在使用与某些种类的沉积循环相关联的非常短的等离子体激励时会是很重要的。

81.在一些实施方式中,基座408可以通过加热器410进行温度控制。此外,在一些实施方式中,用于沉积处理站400的压强控制可以由蝶形阀418提供。如在图4的实施方式中所示的那样,蝶形阀418节流由下游真空泵(未示出)提供的真空。然而,在一些实施方式中,处理站400的压强控制也可以通过改变引入到处理站400的一种或多种气体的流速进行调整。

82.在一些实施方式中,本文所提供的衬底在多站式工具中处理。图5示出了多站式处理工具500的实施方式的示意图,多站式处理工具500具有入站装载锁502和出站装载锁504,入站装载锁502和出站装载锁504中的任一者或两者可包括远程等离子体源。在大气压下,机械手506被配置为将晶片从经由晶舟508装载的盒通过大气端口510移动到入站装载锁502中。晶片由机械手506置于入站装载锁502中的基座512上,关闭大气端口510,并且抽空装载锁。其中,入站装载锁502包括远程等离子体源,晶片可以暴露于装载锁中的远程等离子体处理中,然后被引入到处理室514。进一步,晶片也可以在入站装载锁502中被加热,例如,以除去水分和吸附的气体。接着,打开通向处理室514的室传输端口516,而另一个机械手(未示出)将晶片放置到反应器中于在反应器中所示出的基座上以进行处理。

83.所描绘的处理室514包括四个处理站,在图5所示的实施方式中,编号为1至4。每个站具有加热基座(对于站1以518显示)以及气体管线入口。应当理解,在一些实施方式中,每一个处理站可以具有不同的用途或多种用途。虽然所描绘的处理室514包括四个站,但是应当理解,根据本公开的处理室可以具有任何合适数量的站。在一些实施方式中,处理室可以具有5个或更多个站,而在其他实施方式中,处理室可以具有3个或更少的站。

84.图5还描绘了用于在处理室514内传送晶片的晶片搬运系统590的一个实施方式。在一些实施方式中,晶片搬运系统590可以在各种处理站之间和/或在处理站和装载锁之间传送晶片。应当理解,可以采用任何合适的晶片搬运系统。非限制性实例包括晶片旋转式传送带和晶片搬运机械手。图5还描绘了用于控制处理工具500的工艺条件和硬件状态的系统控制器550的一个实施方式。系统控制器550可包括一个或多个存储器设备556、一个或多个大容量存储设备554以及一个或多个处理器552。处理器552可以包括cpu或计算机、模拟和/或数字输入/输出连接件、步进电机控制器板等。

85.在一些实施方式中,系统控制器550控制处理工具500的活动中的全部。系统控制器550执行系统控制软件558,系统控制软件558存储在大容量存储设备554中,装载到存储器设备556中,并且在处理器552上执行。系统控制软件558可包括用于控制时序、气体的混合、室和/或站的压强、室和/或站的温度、清扫条件和时序、晶片的温度、rf功率电平、rf频率、衬底、基座、卡盘和/或底座的位置、以及通过处理工具500执行的特定工艺的其它参数的指令。系统控制软件558可以以任何合适的方式进行配置。例如,各种处理工具组件子程序或控制的对象可以被写入以控制根据所公开的方法执行各种处理工具处理所需要的处理工具组件的操作。系统控制软件558可以以任何合适的计算机可读编程语言进行编码。

86.在一些实施方式中,系统控制软件558可包括用于控制上述各种参数的输入/输出控制(ioc)测序指令。例如,ald工艺的各阶段可包括用于由系统控制器550执行的一个或多个指令。用于设置ald工艺阶段的工艺条件的指令例如可以被包括在相应的ald配方阶段中。在一些实施方式中,可按顺序排列这些ald配方阶段,使得用于ald处理阶段的所有指令与该处理阶段同时执行。

87.在一些实施方式中,可以采用存储在与系统控制器550相关联的大容量存储设备554和/或存储器设备556上的其它计算机软件和/或程序。用于此目的的程序或程序段的示例包括衬底定位程序、工艺气体控制程序、压强控制程序、加热器控制程序以及等离子体控制程序。

88.衬底定位程序可以包括用于处理工具组件的程序代码,该处理工具组件用于将衬底装载到基座518上并控制衬底和处理工具500的其它部件之间的间隔。

89.工艺气体控制程序可包括用于控制气体组成和流率以及任选地用于使气体在沉积之前流入一个或多个处理站以稳定在处理站中的压强的代码。该工艺气体控制程序可以包括用于控制气体组成和在公开范围中的任何范围内的流率的代码。压强控制程序可以包括用于通过例如在处理站的排放系统中的节流阀、调节流进处理站中的气体流量等控制处理站内的压强的代码。压强控制程序可以包括用于保持处理站内在公开范围中的任何范围内的压强的代码。

90.加热器控制程序可包括用于控制流至用于加热衬底的加热单元的电流的代码。替代地,加热器控制程序可控制传热气体(如氦)朝向衬底上的传送。加热器控制程序可以包括将衬底的温度保持在在公开范围中的任何范围内的指令。

91.等离子体控制程序可以包括用于设置施加到在一个或多个处理站中的处理电极的rf功率电平和频率的代码,例如使用本文公开的任何rf功率电平。等离子体控制程序还可以包括用于控制每次等离子体暴露的持续时间的代码。

92.在一些实施方式中,可以存在与系统控制器550相关联的用户界面。用户界面可以包括显示屏、装置和/或工艺条件的图形软件显示器、以及诸如定点设备、键盘、触摸屏、麦克风等用户输入设备。

93.在一些实施方式中,由系统控制器550调整的参数会涉及工艺条件。非限制性实例包括工艺气体组成和流率、温度、压强、等离子体条件(例如,rf功率电平、频率和暴露时间)、等等。这些参数可以以配方的形式提供给用户,配方可以利用所述用户界面输入。

94.用于监控处理的信号可以由系统控制器550的模拟和/或数字输入连接件从各种处理工具传感器提供。用于控制处理的信号可以通过处理工具500的模拟和数字输出连接件输出。可被监控的处理工具传感器的非限制性实例包括质量流量控制器、压力传感器(例如压力计)、热电偶等。经适当编程的反馈和控制算法可以与来自这些传感器的数据一起使用,以保持工艺条件。

95.可以使用任何合适的室来实现所公开的实施方式。示例性的沉积装置包括但不限于来自产品系列、产品系列和/或产品系列(每一种可从加利福尼亚州fremont的lam research corp.获取)的装置,或各种其他可商用的处理系统中的任何一种。站中的两个或更多个可以执行相同的功能。类似地,两个或更多个站可以执行不同的功能。每个站可以被设计/配置为根据需要执行特定的功能/方法。

96.图6是适用于根据本发明的某些实施方式进行薄膜沉积工艺的处理系统的框图。所述系统600包括传送模块603。当正被处理的衬底在不同的反应器模块之间移动时,传送模块603提供干净的加压环境以尽可能减小所述衬底的污染风险。安装在传送模块603上的是两个多站式反应器609和610,每一个能够根据某些实施方式执行原子层沉积(ald)和/或化学气相沉积(cvd)。反应器609和610可以包括可以依照所公开的实施方式顺序或非顺序地执行操作的多个站611、613、615和617。这些站可以包括加热基座或衬底支撑件、一个或多个气体入口或喷头或分散板。

97.也可以安装在所述传送模块603上的是一个或更多个单或多站式模块607,其能进行等离子体或化学(非等离子体)预清洗或者所描述的与所公开的方法相关的任何其他工艺。该模块607在某些情况下也可用于多种处理,以例如制备用于沉积工艺的衬底。该模块607还可以被设计/配置为执行各种其它处理,例如蚀刻或抛光。所述系统600还包括一个或更多个晶片源模块601,在处理之前和之后晶片被存储在晶片源模块601。大气转移室619中的大气机械手(未示出)可以首先将晶片从源模块601移动到装载锁621。传送模块603中的晶片传移设备(通常为机械手臂单元)将晶片从装载锁621移动到安装在传送模块603上的模块上以及将晶片在这些模块之间移动。

98.在多种实施方式中,采用系统控制器629控制沉积过程中的工艺条件。所述控制器629将通常包括一个或更多个存储器器件和一个或更多个处理器。所述处理器可包括cpu或计算机、模拟和/或数字输入/输出连接、步进电机控制器板等。

99.所述控制器629可控制所有沉积设备的活动。所述系统控制器629运行系统控制软件,所述系统控制软件包括用于控制时序、气体混合、室压强、室温度、晶片温度、射频(rf)功率电平、晶片卡盘或基座位置和特定工艺的其他参数的指令集。在一些实施方式中,可以使用存储在与控制器629相关的存储器器件上的其他计算机程序。

100.通常,将有与控制器629相关联的用户界面。用户界面可包括显示屏,所述装置和/或工艺条件的图形软件显示器和用户输入设备,例如定点设备、键盘、触摸屏、麦克风等。

101.系统控制逻辑可以任何合适的方式进行配置。一般情况下,所述逻辑可被设计或配置在硬件和/或软件中。用于控制驱动电路的指令可被硬编码或作为软件提供。所述指令可通过“编程”提供。这样的编程被理解为包括任何形式的逻辑,该逻辑包括数字信号处理器、专用集成电路以及具有作为硬件实施的具体算法的其他设备中的硬编码逻辑。编程也被理解为包括可在通用处理器上执行的软件或固件指令。系统控制软件可以以任何合适的计算机可读编程语言编码。

102.用于控制工艺序列中的含锗还原剂脉冲、氢气流量、和含钨前体脉冲以及其他工艺的计算机程序代码可以任何常规的计算机可读编程语言:例如,汇编语言、c、c 、pascal、fortran或其它写入。由处理器执行编译后的目标代码或脚本以进行程序中识别的任务。还如所指示的,程序代码可以是硬编码的。

103.控制器参数涉及工艺条件,诸如例如工艺气体组成和流率、温度、压强、冷却气体压强、衬底温度和室壁温度。这些参数以配方的形式提供给用户,并且可利用用户界面输入。用于监控工艺的信号可以通过系统控制器629的模拟和/或数字输入连接来提供。用于控制工艺的信号通过沉积装置620的模拟和数字输出连接件输出。

104.所述系统软件可以许多不同的方式进行设计或配置。例如,可以写入多个室组件

子程序或控制目标以控制根据公开的实施方式执行沉积工艺(以及在某些情况下执行其他工艺)所需要的室组件的操作。用于此目的的程序或程序段的示例包括衬底定位代码、工艺气体控制代码、压强控制代码、和加热器控制代码。

105.在一些实施方案中,控制器629是系统的一部分,该系统可以是上述实施例的一部分。这样的系统包括半导体处理设备,半导体处理设备包括一个或多个处理工具、一个或多个室、用于处理的一个或多个平台、和/或特定的处理部件(晶片基座、气体流系统等)。这些系统可以与电子器件集成,以便在半导体晶片或衬底的处理之前、期间或之后控制这些系统的操作。电子器件可以被称为“控制器”,其可以控制一个或多个系统的各种组件或子部分。根据处理要求和/或系统的类型的不同,控制器629可以被编程,以控制本发明所公开的工艺中的任何一些,包括控制处理气体的输送、温度设置(例如,加热和/或冷却)、压强设置、真空设置、功率设置、在一些系统中的射频(rf)发生器设置、rf匹配电路设置、频率设置、流率设置、流体输送设置、位置和操作设置、晶片转移进出工具和其他转移工具和/或连接到特定系统的或与该系统接口的装载锁的传送。

106.从广义上讲,控制器可以被定义为接收指令、发出指令、控制操作、使能清洁操作、使能终点测量等的具有各种集成电路、逻辑、存储器、和/或软件的电子器件。该集成电路可以包括固件形式的存储程序指令的芯片、数字信号处理器(dsp)、定义为专用集成电路(asic)的芯片、和/或执行程序指令(例如,软件)的一个或多个微处理器或微控制器。程序指令可以是以各种不同的设置(或程序文件)形式输送到控制器或系统的指令,不同的设置(或程序文件)定义用于在半导体晶片上或针对半导体晶片进行特定处理的操作参数。在一些实施方式中,所述操作参数可以是由工艺工程师定义的用以完成在晶片的一个或多个(种)层、材料、金属、氧化物、硅、二氧化硅、表面、电路和/或裸芯片的制造过程中的一个或多个处理步骤的配方的一部分。

107.在一些实施方案中,控制器可以是与系统集成、耦接或者说是通过网络连接系统或它们的组合的计算机的一部分或者与该计算机耦接。例如,控制器可以在“云端”或者是晶片厂(fab)主计算机系统的全部或一部分,它们可以允许远程访问晶片处理。计算机可以启用对系统的远程访问以监测制造操作的当前进程,检查过去的制造操作的历史,检查多个制造操作的趋势或性能标准,以改变当前处理的参数,设置处理步骤以跟随当前的处理或者开始新的工艺。在一些实施例中,远程计算机(例如,服务器)可以通过网络给系统提供工艺配方,网络可以包括本地网络或互联网。远程计算机可以包括允许输入或编程参数和/或设置的用户界面,这些参数和/或设置然后从远程计算机传输到系统。在一些示例中,控制器接收数据形式的指令,这些指令指明在一个或多个操作期间将要执行的每个处理步骤的参数。应当理解,这些参数可以针对将要执行的工艺类型以及工具类型,控制器被配置成连接或控制该工具类型。因此,如上所述,控制器可以例如通过包括一个或多个分立的控制器而分布,这些分立的控制器通过网络连接在一起并且朝着共同的目标(例如,本文所述的工艺和控制)工作。用于这些目的的分布式控制器的实例将是与一个或多个远程集成电路(例如,在平台水平或作为远程计算机的一部分)通信的在室内的一个或多个集成电路,它们结合以控制室内的工艺。

108.示例性系统可以包括但不限于等离子体蚀刻室或模块、沉积室或模块、旋转冲洗室或模块、金属电镀室或模块、清洁室或模块、倒角边缘蚀刻室或模块、物理气相沉积(pvd)

室或模块、化学气相沉积(cvd)室或模块、原子层沉积(ald)室或模块、原子层蚀刻(ale)室或模块、离子注入室或模块、轨道室或模块、以及在半导体晶片的制备和/或制造中可以关联的或使用的任何其他的半导体处理系统。

109.如上所述,根据工具将要执行的一个或多个工艺步骤,控制器可以与一个或多个其他的工具电路或模块、其他工具组件、组合工具、其他工具界面、相邻的工具、邻接工具、位于整个工厂中的工具、主机、另一个控制器、或者将晶片的容器往来于半导体制造工厂中的工具位置和/或装载口搬运的材料搬运中使用的工具通信。进一步的实现方式

110.本文描述的装置和工艺可以与光刻图案化工具或工艺结合使用,例如,用于制备或制造半导体器件、显示器、led、光伏电池板等。通常,虽然不是必要地,这样的装置和工艺将在共同的制造设施中一起使用或操作。膜的光刻图案化通常包括以下步骤中的一些或所有,每个步骤启用多个可行的工具:(1)使用旋涂或喷涂工具在工件,即,衬底上涂覆光致抗蚀剂;(2)使用热板或加热炉或紫外线固化工具固化光致抗蚀剂;(3)使用例如晶片步进机(stepper)之类的工具使光致抗蚀剂暴露于可见光或紫外线或x射线;(4)使抗蚀剂显影以便选择性地去除抗蚀剂并且从而使用例如湿式清洗台之类的工具将其图案化;(5)通过使用干式或等离子体辅助蚀刻工具将抗蚀剂图案转印到下伏的膜或工件上;并且(6)使用例如射频或微波等离子体抗蚀剂剥离器之类的工具去除抗蚀剂。可以采用这种处理,例如,以将如上所述的上面沉积有氮化钽、钽和/或铜层的介电层图案化。xps实验结果

111.使用表1所示的工艺条件,通过将晶片衬底顺序地暴露于tma和叔丁醇而将氧化铝膜沉积在含有钴层的晶片衬底上。通过xps分析钴层。图7a示出了晶片边缘上的膜的xps图。可以看出,xps表明不存在归因于钴-氧键的显著的信号。在晶片衬底的中心获得了类似的结果。

112.通过用tma和co2等离子体依次处理具有钴层的衬底来沉积比较的基于氧化铝的膜。通过xps分析钴层。图7b中提供的晶片边缘上的膜的xps图示出了显著的钴-氧键合。对于从晶片的中心获得的膜,获得了类似的结果。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。