1.本技术涉及显示技术领域,具体涉及一种显示面板及其制备方法。

背景技术:

2.在生产制造业,精简生产工艺、降低生产成本是永不过时的追求;在显示面板行业也是如此。目前显示行业应用最广泛的薄膜晶体管(thin film transistor,tft)显示面板,由于曝光制程的精密性和曝光设备的昂贵价格,导致曝光制程道数越多,代表其工艺越复杂,从而制程成本增高。而现有的显示面板中,制备像素电极和钝化层通常需要进行两道曝光工艺,从而导致显示面板的制备成本增加。

技术实现要素:

3.本技术实施例提供一种显示面板及其制备方法,降低显示面板的制备成本。

4.本技术提供一种显示面板,包括:

5.衬底;

6.晶体管层,所述晶体管层设置于所述衬底上,所述晶体管层远离所述衬底的一面上设置有诱导结晶部;以及

7.像素电极,所述像素电极设置于所述晶体管层上,且位于所述诱导结晶部上,所述像素电极为结晶的像素电极。

8.可选的,在本技术的一些实施例中,所述诱导结晶部包括第一诱导结晶部和第二诱导结晶部,所述晶体管层包括晶体管和设置于所述晶体管上的钝化层;

9.所述晶体管包括第一电极,所述第一电极远离所述衬底的一面设置有所述第一诱导结晶部;

10.所述钝化层包括通孔,所述通孔贯穿所述钝化层以暴露所述第一诱导结晶部,所述钝化层远离所述衬底的一面设置有所述第二诱导结晶部,且所述第二诱导结晶部围绕所述通孔设置。

11.可选的,在本技术的一些实施例中,所述第一诱导结晶部为第一粗糙表面,所述第二诱导结晶部为第二粗糙表面。

12.可选的,在本技术的一些实施例中,所述第一粗糙表面和所述第二粗糙表面的粗糙度均大于等于10纳米。

13.可选的,在本技术的一些实施例中,所述第一粗糙表面的粗糙度大于所述第二粗糙表面的粗糙度。

14.可选的,在本技术的一些实施例中,所述钝化层远离所述衬底的一面具有多个间隔设置的所述第二诱导结晶部。

15.相应的,本技术还提供一种显示面板的制备方法,包括:

16.提供一衬底;

17.在所述衬底上设置晶体管层材料,对所述晶体管层材料进行图案化处理形成晶体

管层,所述晶体管层远离所述衬底的一面设置有诱导结晶部;以及

18.在所述晶体管层上形成像素电极,且所述像素电极位于所述诱导结晶部上,所述像素电极为结晶的像素电极。

19.可选的,在本技术的一些实施例中,晶体管层包括晶体管和设置于所述晶体管的钝化层,所述晶体管包括第一电极,在所述衬底上设置晶体管层材料,对所述晶体管层材料进行图案化处理形成晶体管层的步骤中,包括:

20.在所述衬底上形成晶体管的导电层;

21.在所述晶体管上设置钝化层材料,并进行图形化处理,所述钝化层材料形成钝化层,所述导电层形成第一电极;

22.其中,所述第一电极远离所述衬底的一面形成第一诱导结晶部,所述钝化层包括通孔,所述通孔贯穿所述钝化层以暴露所述第一诱导结晶部,所述钝化层远离所述衬底的表面形成第二诱导结晶部。

23.可选的,在本技术的一些实施例中,所述晶体管层包括非结晶区和设置于所述非结晶区两侧的结晶区,所述导电层位于所述结晶区,在所述晶体管上设置钝化层材料,并进行图形化处理,所述钝化层材料形成钝化层,所述导电层形成第一电极的步骤中,包括:

24.在所述晶体管层上设置钝化层材料;

25.提供一光阻层,所述光阻层设置于所述钝化层材料上,并位于所述非结晶区;

26.对所述钝化层材料进行第一图案化处理,形成具有通孔的钝化中间层,所述通孔贯穿所述钝化中间层以暴露所述导电层;

27.对所述钝化中间层进行第二图案化处理,所述导电层形成第一电极,所述第一电极远离所述衬底的一面形成第一诱导结晶部,所述钝化中间层形成钝化层,所述钝化层远离所述衬底的一面形成第二诱导结晶部,所述第二诱导结晶部围绕所述通孔设置,所述第一诱导结晶部和所述第二诱导结晶部位于所述结晶区;

28.去除所述光阻层。

29.可选的,在本技术的一些实施例中,在所述钝化层上设置像素电极,所述像素电极设置于所述第二诱导结晶部,并延伸入所述通孔中与所述第一诱导结晶部接触的步骤中,包括:

30.在所述钝化层上设置像素电极材料,采用湿蚀刻方式处理所述像素电极材料,所述像素电极材料形成像素电极,所述像素电极位于所述第二诱导结晶部,并延伸入所述通孔与所述第一诱导结晶部接触。

31.本技术公开了一种显示面板及其制备方法,显示面板包括衬底、晶体管层和像素电极,晶体管层设置于衬底上,晶体管层远离衬底的一面上设置有诱导结晶部,像素电极设置于晶体管层上,且位于诱导结晶部上。在本技术中,通过在晶体管层上设置诱导结晶部,以诱导位于诱导结晶部上的像素电极结晶,从而使得制备像素电极的过程中无需采用曝光工艺,从而减少了显示面板的曝光制程数量,简化了显示面板的制备工艺。

附图说明

32.为了更清楚地说明本技术实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于

本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

33.图1是本技术实施例提供的显示面板的结构示意图。

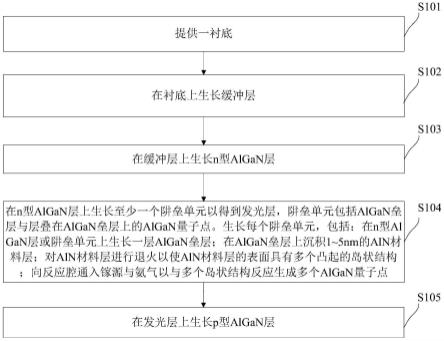

34.图2是本技术实施例提供的显示面板的制备方法的流程步骤示意图。

35.图3-图9是本技术实施例提供的显示面板的制备方法的流程步骤示意图。

具体实施方式

36.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。此外,应当理解的是,此处所描述的具体实施方式仅用于说明和解释本技术,并不用于限制本技术。在本技术中,在未作相反说明的情况下,使用的方位词如“上”和“下”通常是指装置实际使用或工作状态下的上和下,具体为附图中的图面方向;而“内”和“外”则是针对装置的轮廓而言的。在本技术中,“反应”可以为化学反应或物理反应。

37.本技术公开了一种显示面板及其制备方法,显示面板包括衬底、晶体管层和像素电极,晶体管层设置于衬底上,晶体管层远离衬底的一面上设置有诱导结晶部,像素电极设置于晶体管层上,且位于诱导结晶部上。

38.在本技术中,通过在晶体管层上设置诱导结晶部,以诱导位于诱导结晶部上的像素电极结晶,从而使得制备像素电极的过程中无需采用曝光工艺,从而减少了显示面板的曝光制程数量,简化了显示面板的制备工艺。

39.请参阅图1,本技术提供一种显示面板10。显示面板10包括衬底100、晶体管层200和像素电极300。

40.晶体管层200设置于衬底100上,晶体管层200远离衬底100的一面上设置有诱导结晶部201。具体的,诱导结晶部201用于诱导像素电极300结晶。诱导结晶部201包括一第一诱导结晶部202和至少一第二诱导结晶部203。晶体管层200包括非结晶区204和设置于非结晶区204两侧的结晶区205。晶体管层200包括至少一晶体管和设置于晶体管上的钝化层260。晶体管为底栅晶体管。每一晶体管包括栅极210、栅绝缘层220、有源层230、第一电极240和第二电极250。栅极210设置于衬底100上。栅绝缘层220设置于衬底100以及栅极210上。有源层230设置于栅绝缘层220上。有源层230位于栅极210的正上方。有源层230包括金属氧化物有源层和硅基有源层中的一种。第一电极240设置于栅绝缘层220以及有源层230的一侧上。第一电极240远离衬底100的一面设置有第一诱导结晶部202。第一诱导结晶部202位于结晶区205。第一诱导结晶部202用于诱导位于第一诱导结晶部202上的像素电极300结晶。进一步的,第一诱导结晶部202为第一粗糙表面。第二电极250设置于有源层230的另一侧上。第一电极240和第二电极250间隔设置。第一电极240为源极和漏极中的一种。第二电极250为源极和漏极中的另一种。钝化层260设置于栅绝缘层220、有源层230、第一电极240和第二电极250上。钝化层260设置有通孔261。通孔261贯穿钝化层260以暴露第一诱导结晶部202。第一诱导结晶部202仅位于通孔261暴露的第一电极240区域。第二诱导结晶部203设置于钝化层260远离衬底100的一面。第二诱导结晶部203位于围绕通孔261设置。第二诱导结晶部203

位于结晶区205。第二诱导结晶部203用于诱导位于第二诱导结晶部203上的像素电极300结晶。第二诱导结晶部203为第二粗糙表面。

41.现有技术中,像素电极300必须在高温下才能发生结晶,而在本技术中,在第一电极240上设置第一诱导结晶部202,在钝化层260上设置第二诱导结晶部203,且第一诱导结晶部202为第一粗糙表面,第一诱导结晶部202为第一粗糙表面,使得像素电极300与第一电极240以及钝化层260的接触面积增大,同时粗糙表面的凸起充当晶核,可以降低像素电极300的晶化温度,即可以降低像素电极300结晶所需的能量,使得像素电极300在沉积的过程中发生结晶,而非结晶区204上的像素电极300不结晶,使得在后续采用蚀刻工艺蚀刻像素电极300时,结晶的像素电极300的蚀刻速率小于不结晶的像素电极300,从而使得不结晶的像素电极300被蚀刻,结晶的像素电极300留在第一电极240以及钝化层260上,从而使得像素电极300无需采用曝光工艺才可以形成,节省了显示面板10的曝光次数,从而简化了显示面板10的制备工艺,从而降低了显示面板10的制备成本。

42.在一实施例中,钝化层260远离衬底100的一面具有多个间隔设置的第二诱导结晶部203。

43.在一实施例中,第一粗糙表面和第二粗糙表面的粗糙度均大于等于10纳米。进一步的,第一粗糙表面和第二粗糙表面的粗糙度均为10纳米-100纳米。具体的,第一粗糙表面和第二粗糙表面的粗糙度均可以为10纳米、15纳米、20纳米、50纳米、80纳米、90纳米或100纳米等。

44.在本技术中,第一粗糙表面和第二粗糙表面的粗糙度均设置为大于等于10纳米,进一步使得像素电极300与第一电极240以及钝化层260的接触面积增大,进一步降低像素电极300结晶所需的能量,使得像素电极300在沉积的过程中发生结晶,而非结晶区204上的像素电极300不结晶,使得在后续采用蚀刻工艺蚀刻像素电极300时,结晶的像素电极300的蚀刻速率进一步小于非晶的像素电极300,从而使得非晶的像素电极300被蚀刻,结晶的像素电极300留在第一电极240以及钝化层260上,从而使得像素电极300无需采用曝光工艺才可以形成,节省了显示面板10的曝光次数,从而简化了显示面板10的制备工艺,从而降低了显示面板10的制备成本。

45.在一实施例中,第一粗糙表面的粗糙度大于第二粗糙表面的粗糙度。在本技术中,因位于第一诱导结晶部202上的像素电极300较厚,将第一粗糙表面的粗糙度设置为大于第二粗糙表面的粗糙度,进一步提高像素电极300与第一诱导结晶部202的接触面积,进一步降低了像素电极300结晶所需的能量,从而提高像素电极300的结晶性能。

46.像素电极300设置于晶体管层200上,且位于诱导结晶部201上。具体的,像素电极300设置于钝化层260上,并延伸入通孔261中与第一电极240接触。像素电极300位于结晶区205。

47.在另一实施例中,晶体管可以为顶栅晶体管。

48.在一实施例中,诱导结晶部201为具有粘附性的涂层,且涂层的可见光透过率大于85%及以上。涂层的可见光透过率可以大于85%、90%、95%或98%等。

49.本技术还提供一种显示面板10的制备方法,包括:

50.b11、提供一衬底。

51.b12、在衬底上设置晶体管层材料,对晶体管层材料进行图案化处理形成晶体管

层,晶体管层远离衬底的一面形成诱导结晶部。

52.b13、在晶体管层上形成像素电极,且像素电极位于诱导结晶部上,像素电极为结晶的像素电极。

53.本技术提供一种显示面板的制备方法,包括:提供一衬底。然后,在衬底上设置晶体管层材料,对晶体管层材料进行图案化处理形成晶体管层,晶体管层远离衬底的一面形成诱导结晶部。最后,在晶体管层上形成像素电极,像素电极为结晶的像素电极,且像素电极位于诱导结晶部上,像素电极为结晶的像素电极。在本技术中,在晶体管层远离衬底的一面设置于诱导结晶部,以诱导位于诱导结晶部上的像素电极结晶,从而使得制备像素电极的过程中无需采用曝光工艺,从而减少了显示面板的曝光制程数量,简化了显示面板的制备工艺。

54.请参阅图2-图9,本技术还提供一种显示面板10的制备方法,包括:

55.b11、提供一衬底。

56.b12、在衬底上设置晶体管层材料,对晶体管层材料进行图案化处理形成晶体管层,晶体管层远离衬底的一面形成诱导结晶部。

57.请参阅图3,具体的,晶体管层200包括非结晶区204和设置于非结晶区204两侧的结晶区205。在衬底100上设置栅极210材料,并进行曝光、显影和蚀刻等处理形成栅极210。即栅极210采用第一道光罩。然后,在衬底100以及栅极210上形成栅绝缘层220。然后,在栅绝缘层220上层叠形成半导体层和导电层材料,并进行曝光、显影和蚀刻等处理后,半导体层形成有源层230,导电层材料形成间隔设置于有源层230上的导电层397和第二电极250,即有源层230、导电层397和第二电极250采用一道光罩形成。有源层230位于栅极210的正上方。有源层230包括金属氧化物有源层230和硅基有源层230中的一种。栅极210、栅绝缘层220、有源层230、导电层397和第二电极250构成晶体管层200的晶体管。

58.请参阅图4,然后,在栅绝缘层220、有源层230、第一电极240和第二电极250上设置钝化层260材料。

59.请参阅图5,然后,提供一光阻层398。光阻层398设置于钝化层260材料上。光阻层398包括多个间隔设置的光阻部。光阻部位于非结晶区204。光阻层为光刻胶。

60.请参阅图6,然后,对钝化层260材料进行第一图案化处理,形成具有通孔261的钝化中间层,通孔261贯穿钝化中间层以暴露导电层397。具体的,对钝化层260材料进行曝光、显影和蚀刻等处理形成具有通孔261的钝化中间层,通孔261贯穿钝化中间层以暴露导电层397。然后,对光阻层398进行灰化处理,使得光阻层398的厚度减薄。

61.然后,对钝化中间层进行第二图案化处理,导电层397形成第一电极240,第一电极240远离衬底100的一面形成第一诱导结晶部202,钝化中间层形成钝化层260,钝化层260远离衬底100的一面形成第二诱导结晶部203,第二诱导结晶部203围绕通孔261设置,第一诱导结晶部202和第二诱导结晶部203位于结晶区205。具体的,对钝化中间层进行等离子体处理,导电层397形成第一电极240,且第一电极240远离衬底100的一面形成第一诱导结晶部202,同时钝化中间层形成钝化层260,且钝化层260远离衬底100的一面形成第二诱导结晶部203。

62.请参阅图7,去除光阻层398。

63.b13、在晶体管层上形成像素电极,且像素电极位于诱导结晶部上,像素电极为结

晶的像素电极。

64.请参阅图8和图9,具体的,采用物理气相沉积工艺沉积像素电极材料301,设置于第一诱导结晶部202和第二诱导结晶部203的像素电极材料301结晶,而设置于非结晶区204的像素电极材料301不结晶,对像素电极材料301进行蚀刻处理时,因结晶区205上的像素电极材料301的蚀刻速率远远低于非结晶区204上的像素电极材料301,使得非结晶区204的像素电极材料301被蚀刻,而结晶区205的像素电极材料301留在第一电极240和钝化层260上,从而形成像素电极300。像素电极300具有多个间隔设置的像素电极300部。像素电极300和钝化层260采用一道光罩制成。也即采用物理气相沉积工艺沉积像素电极材料301后,直接对其进行蚀刻形成像素电极。即,像素电极的形成无需经过曝光工艺,从而降低了显示面板10的制备成本。

65.在一实施例中,蚀刻处理为湿蚀刻处理或干蚀刻处理。进一步的,湿蚀刻处理的蚀刻液为草酸蚀刻液或硝硫酸蚀刻液。

66.在一实施例中,物理气相沉积工艺的沉积气体包括水蒸气、氢气和氧气的混合气体。

67.在一实施例中,在沉积像素电极材料301时,将设备的温度控制为0-200摄氏度。具体的,可以将设备的温度可以为0摄氏度、50摄氏度、80摄氏度、150摄氏度或200摄氏度等。

68.现有技术中,像素电极300必须在高温下才能发生结晶,而在本技术中,在第一电极240上设置第一诱导结晶部202,在钝化层260上设置第二诱导结晶部203,且第一诱导结晶部202为第一粗糙表面,第一诱导结晶部202为第一粗糙表面,使得像素电极300与第一电极240以及钝化层260的接触面积增大,同时粗糙表面的凸起充当晶核,可以降低像素电极300的晶化温度,即可以降低像素电极300结晶所需的能量,使得像素电极300在沉积的过程中发生结晶,而非结晶区204上的像素电极300不结晶,使得在后续采用蚀刻工艺蚀刻像素电极300时,结晶的像素电极300的蚀刻速率小于非晶的像素电极300,从而使得非晶的像素电极300被蚀刻,结晶的像素电极300留在第一电极240以及钝化层260上,从而使得像素电极300无需采用曝光工艺才可以形成,节省了显示面板10的曝光次数,从而简化了显示面板10的制备工艺,从而降低了显示面板10的制备成本。

69.本技术提供一种显示面板10及其制备方法,包括:提供一衬底100。然后,在衬底100上设置晶体管层200材料,对晶体管层200材料进行图案化处理形成晶体管层200,晶体管层200远离衬底100的一面形成诱导结晶部201。最后,在晶体管层200上形成像素电极300,像素电极300为结晶的像素电极300,且像素电极300位于诱导结晶部201上,像素电极300为结晶的像素电极300。在本技术中,在晶体管层200远离衬底100的一面设置于诱导结晶部201,以诱导位于诱导结晶部201上的像素电极300结晶,从而使得制备像素电极300的过程中无需采用曝光工艺,从而减少了显示面板10的曝光制程数量,简化了显示面板10的制备工艺。

70.以上对本技术实施例所提供的一种显示面板及其制备方法进行了详细介绍,本文中应用了具体个例对本技术的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本技术的方法及其核心思想;同时,对于本领域的技术人员,依据本技术的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本技术的限制。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。