1.本发明涉及通信技术领域,尤其涉及一种芯片或芯片模块的检测方法和装置。

背景技术:

2.芯片设计是芯片产业链的核心和源头,其自主可控度在整个芯片的自主可控度中占有举足轻重的地位。芯片设计环节自主可控度的评估,多按照完全自主设计、部分自主设计、完全外包的方式进行分级,取证多通过调查、评审等形式进行。

3.相关的自主可控评级的实施方案,多采用调查、评审的方式进行,这种评估方法的准确度取决于相关材料的真实性、可核查性、完备性、以及专家的经验和水平,在一定程度上无法保证其客观性和全面性。

技术实现要素:

4.有鉴于此,本发明实施例期望提供一种芯片或芯片模块的检测方法和装置。

5.为达到上述目的,本发明实施例的技术方案是这样实现的:

6.本发明实施例提供了一种芯片或芯片模块的检测方法,该方法包括:

7.确定芯片或芯片模块的实物信息,和/或确定芯片或芯片模块的设计信息;

8.将所述实物信息与所述设计信息进行比对,和/或对所述设计信息进行验证;

9.基于比对结果和/或验证结果,对芯片或芯片模块的自主度和/或可控度进行判定。

10.本发明实施例还提供了一种芯片或芯片模块的检测装置,该装置包括:

11.信息确定模块,用于确定芯片或芯片模块的实物信息,和/或确定芯片或芯片模块的设计信息;

12.信息处理模块,用于将所述实物信息与所述设计信息进行比对,和/或对所述设计信息进行验证;

13.判定模块,用于基于比对结果和/或验证结果,对芯片或芯片模块的自主度和/或可控度进行判定。

14.本发明实施例还提供了一种芯片或芯片模块的检测装置,该装置包括:处理器和用于存储能够在处理器上运行的计算机程序的存储器,

15.其中,所述处理器用于运行所述计算机程序时,执行上述方法的步骤。

16.本发明实施例提供的芯片或芯片模块的检测方法和装置,确定芯片或芯片模块的实物信息,和/或确定芯片或芯片模块的设计信息;将所述实物信息与所述设计信息进行比对,和/或对所述设计信息进行验证;基于比对结果和/或验证结果,对芯片或芯片模块的自主度和/或可控度进行判定。可见,本发明实施例为芯片或芯片模块的自主度和/或可控度的评估提供了一个简便、客观的检测依据,提高了芯片或芯片模块的自主度和/或可控度评估的客观性、实操性和全面性,并可为芯片或芯片模块的自主度和/或可控度评估取证材料的真实性做佐证依据,可作为芯片或芯片模块的自主度和/或可控度评估的有力支撑。

附图说明

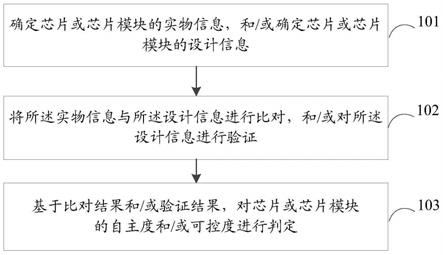

17.图1为本发明实施例所述芯片或芯片模块的检测方法流程示意图;

18.图2为本发明实施例所述芯片或芯片模块的检测装置结构示意图;

19.图3为本发明场景实施例1所述检测方法流程示意图(为了清楚显示,图中仅给出各操作的编号);

20.图4为本发明场景实施例2所述检测方法流程示意图(为了清楚显示,图中仅给出各操作的编号,另外,2.5中的和/或关系,图中无法一一展示,只展示其中一种情况-将1.7条中的第二设计信息与1.8条中的第三设计信息进行验证)。

具体实施方式

21.下面结合附图和实施例对本发明进行描述。

22.本发明实施例提供了一种芯片或芯片模块的检测方法,如图1所示,该方法包括:

23.步骤101:确定芯片或芯片模块的实物信息,和/或确定芯片或芯片模块的设计信息;

24.步骤102:将所述实物信息与所述设计信息进行比对,和/或对所述设计信息进行验证;

25.步骤103:基于比对结果和/或验证结果,对芯片或芯片模块的自主度和/或可控度进行判定。

26.本发明实施例为芯片或芯片模块的自主度和/或可控度的评估提供了一个简便、客观的检测依据,提高了芯片或芯片模块的自主度和/或可控度评估的客观性、实操性和全面性,并可为芯片或芯片模块的自主度和/或可控度评估取证材料的真实性做佐证依据,可作为芯片或芯片模块的自主度和/或可控度评估的有力支撑。

27.本发明实施例中,所述芯片包括但不限于以下一种或多种:

28.封装了一个或多个裸片(裸片亦称为裸晶、晶粒)的芯片;

29.未封装的裸片。

30.本发明实施例中,所述芯片模块包括但不限于以下一种或多种:

31.封装了一个或多个裸片的芯片中的裸片;

32.裸片中的功能模块(亦可称之为功能单元、单元等)。

33.(需要说明的是,从分类的角度,这里的芯片、芯片模块是一个统称,包括但不限于集成电路ic、微系统mems、微机电系统、半导体器件、分立器件、传感器、执行器等多个类别)

34.本发明实施例中,所述实物信息包括但不限于以下一种或多种(需要说明的是:可以根据判定芯片或芯片模块的自主度和/或可控度所需要的比对种类,选取实物信息种类,使得实物信息的选取更有针对性):

35.芯片或芯片模块与封装基板间的实物连接关系、和/或芯片或芯片模块与其他芯片或芯片模块间的实物连接关系,所述实物连接关系包括但不限于以下一种或多种表述形式:连接关系实物、描述连接关系的实物图、描述实物连接关系的表格、描述实物连接关系的管脚实物名称及由名称表述的实物连接关系;

36.封装基板的实物信息,所述实物信息包括但不限于以下一种或多种:封装基板实物、封装基板实物线路或线路图、封装基板实物布局或布局图、封装基板实物布线或布线

图、封装基板实物电路或电路图;

37.芯片或芯片模块的实物信息,所述实物信息包括但不限于以下一种或多种:芯片或芯片模块实物、芯片或芯片模块实物版图、芯片或芯片模块实物布图、芯片或芯片模块实物布局布线或布局布线图、芯片或芯片模块实物电路或电路图;

38.其中,所述实物信息包括但不限于以下一种或多种的实物信息:所有层、部分层、一层,层号的选取方法包括但不限于以下一种或多种:随机选取、按照规则选取、设定;对于其中一层,所述实物信息包括但不限于以下一种或多种的实物信息:整个区域、多个局部区域、一个局部区域,区域的选取方法包括但不限于以下一种或多种:随机选取、按照规则选取、设定。

39.本发明实施例中,所述实物信息的获取方法,包括但不限于以下一种或多种:

40.直接取得一个或多个待测芯片或芯片模块并获取实物信息;

41.随机或按照规则选取一个或多个待测芯片或芯片模块并获取实物信息;

42.直接通过包括但不限于以下一种或多种方式获取实物信息:电子计算机断层扫描ct、x射线、x光、放射线、超声、无损检测(亦称为无损观测);(如:对于一个已封装的芯片,直接通过ct获取芯片内部的信息)

43.对已封装的芯片进行芯片开盖(简称开盖)并获取实物信息;

44.针对芯片或芯片模块与封装基板间的实物连接关系、和/或芯片或芯片模块与其他芯片或芯片模块间的实物连接关系被遮挡的情况,通过包括但不限于以下一种或多种方式获取实物连接关系:ct、x射线、x光、放射线、超声、无损检测、去层(亦称为去层次、去除层次、层次去除)、平磨、磨削、研磨、打磨、抛光、腐蚀、刻蚀、剖片(亦称为芯片解剖)、解剖、染色;所述实物连接关系被遮挡的情况包括但不限于倒装焊的芯片中的所述实物连接关系被遮挡;(如:对于倒装焊的芯片,平磨至倒装焊界面,在此界面获取实物连接关系)

45.将芯片或芯片模块与封装基板分离、和/或将芯片或芯片模块与其他芯片或芯片模块分离,所述分离的方法包括但不限于以下一种或多种:断开或移除或去除连接线、腐蚀、刻蚀、加热、去层、平磨、磨削、研磨、打磨、剖片、解剖、取下芯片;

46.通过包括但不限于以下一种或多种方式获取一层或多层的实物信息:直接获取、通过显微镜(包括但不限于以下一种或多种:光学显微镜、电子显微镜)和/或显微成像仪器和/或ct和/或x射线和/或x光和/或放射线和/或超声和/或无损检测获取、去层、平磨、磨削、研磨、打磨、抛光、腐蚀、刻蚀、剖片、解剖、染色、断开或移除或去除连接线;

47.通过显微镜和/或显微成像仪器和/或ct和/或x射线和/或x光和/或放射线和/或超声和/或无损检测、与拍照或/和图像采集或/和录像相结合,或者,直接拍照或/和图像采集或/和录像的方式获取并记录实物信息对应的实物图像、影像或视频;所述实物图像、影像或视频为一个文件、或者多个文件、或者由多个文件拼接或合成的一个整体文件;

48.通过显微镜和/或显微成像仪器和/或ct和/或x射线和/或x光和/或放射线和/或超声和/或无损检测、与肉眼观察相结合,或者直接肉眼观察的方式获取实物信息及对应的实物图像、影像。

49.本发明实施例中,取得或者选取多个待测芯片或芯片模块并获取实物信息,包括但不限于以下一种或多种:

50.为获取多个样本,对实物信息、或/和实物信息与设计信息的比对、或/和芯片或芯

片模块的自主度和/或可控度做统计分析,取得或者选取多个相同型号的芯片或芯片模块、从各芯片或芯片模块中获取相同的实物信息;

51.对于获取实物信息时有破坏性操作或/和从一个芯片或芯片模块中只能获取部分实物信息的情况,取得或者选取多个相同型号的芯片或芯片模块,并从各芯片或芯片模块中获取不同的实物信息、或同时获取相同和不同的实物信息;

52.为判定由多个芯片模块共同组成的芯片的自主度和/或可控度,对芯片中的多个芯片模块分别获取各自的实物信息、开展自主度和/或可控度的判定,基于此结果对芯片的自主度和/或可控度进行判定。

53.本发明实施例中,所述设计信息包括但不限于以下一种或多种(需要说明的是:可以根据判定芯片或芯片模块的自主度和/或可控度所需要的比对种类和/或验证种类,选取设计信息种类,使得设计信息的选取更有针对性):

54.芯片或芯片模块与封装基板间的设计连接关系、和/或芯片或芯片模块与其他芯片或芯片模块间的设计连接关系,所述设计连接关系包括但不限于以下一种或多种表述形式:描述连接关系的设计图、描述设计连接关系的表格、描述设计连接关系的管脚设计名称及由名称表述的设计连接关系;所述设计信息包括但不限于以下一种或多种的设计信息:所有层、部分层、一层,层号的选取方法包括但不限于以下一种或多种:随机选取、按照规则选取、设定;对于其中一层,所述设计信息包括但不限于以下一种或多种的设计信息:整个区域、多个局部区域、一个局部区域,区域的选取方法包括但不限于以下一种或多种:随机选取、按照规则选取、设定;所述设计连接关系的格式包括但不限于一种或多种格式;

55.封装基板的设计信息,所述设计信息包括但不限于以下一种或多种:封装基板设计线路或线路图、封装基板设计布局或布局图、封装基板设计布线或布线图、封装基板设计电路或电路图;所述设计信息包括但不限于以下一种或多种的设计信息:所有层、部分层、一层,层号的选取方法包括但不限于以下一种或多种:随机选取、按照规则选取、设定;对于其中一层,所述设计信息包括但不限于以下一种或多种的设计信息:整个区域、多个局部区域、一个局部区域,区域的选取方法包括但不限于以下一种或多种:随机选取、按照规则选取、设定;所述封装基板的设计信息的格式包括但不限于一种或多种格式;

56.芯片或芯片模块的第一设计信息,所述第一设计信息包括但不限于以下一种或多种:芯片或芯片模块设计版图、芯片或芯片模块设计布图、芯片或芯片模块设计布局布线或布局布线图;所述第一设计信息包括但不限于以下一种或多种的设计信息:所有层、部分层、一层,层号的选取方法包括但不限于以下一种或多种:随机选取、按照规则选取、设定;对于其中一层,所述第一设计信息包括但不限于以下一种或多种的设计信息:整个区域、多个局部区域、一个局部区域,区域的选取方法包括但不限于以下一种或多种:随机选取、按照规则选取、设定;用于比对的第一设计信息,是所述第一设计信息中的所有设计信息或者部分设计信息;用于验证的第一设计信息,是所述第一设计信息中的所有设计信息或者部分设计信息;用于比对的第一设计信息与用于验证的第一设计信息,为相同的或者不同的设计信息(如,确定第一设计信息是所有层设计信息、和部分层或一层设计信息的结合,部分层或一层设计信息是所有层设计信息的一部分;当芯片或芯片模块的实物信息是部分层或一层实物信息时,用于比对的第一设计信息,是与实物信息相对应的部分层或一层的设计信息;当第二设计信息是整个芯片的第二设计信息时,用于验证的第一设计信息,是所有

层设计信息,与第二设计信息做验证);所述第一设计信息的格式包括但不限于一种或多种格式;用于比对的第一设计信息格式与用于验证的第一设计信息格式,为相同的或者不同的格式;

57.芯片或芯片模块的第二设计信息,所述第二设计信息包括但不限于芯片或芯片模块的原理图和/或网表,所述原理图和/或网表包括但不限于以下一种或多种:原理图、原理图对应的网表、晶体管级的网表(需要说明的是,晶体管级的网表是指描述的是晶体管级别,形式多种多样,如cdl网表、scs网表、spice网表等)、数字芯片或数字芯片模块完成最终设计的门级网表、数字芯片或数字芯片模块第一设计信息对应的门级网表;所述第二设计信息包括但不限于所有或者部分的所述设计信息;用于与第一设计信息验证的第二设计信息,是所述第二设计信息中的所有设计信息或者部分设计信息;用于与第三设计信息验证的第二设计信息,是所述第二设计信息中的所有设计信息或者部分设计信息;用于与第四设计信息验证的第二设计信息,是所述第二设计信息中的所有设计信息或者部分设计信息;用于与第一设计信息验证的第二设计信息、用于与第三设计信息验证的第二设计信息、与用于与第四设计信息验证的第二设计信息中,任意两者之间为相同的或者不同的设计信息;所述第二设计信息的格式包括但不限于一种或多种格式;用于与第一设计信息验证的第二设计信息格式、用于与第三设计信息验证的第二设计信息格式、与用于与第四设计信息验证的第二设计信息格式中,任意两者之间为相同的或者不同的格式;

58.芯片或芯片模块的第三设计信息,所述第三设计信息包括但不限于数字芯片或数字芯片模块的寄存器传输级rtl代码综合形成的门级网表;所述第三设计信息包括但不限于所有或者部分的所述设计信息;用于与第二设计信息验证的第三设计信息,是所述第三设计信息中的所有设计信息或者部分设计信息;用于与第四设计信息验证的第三设计信息,是所述第三设计信息中的所有设计信息或者部分设计信息;用于与第二设计信息验证的第三设计信息、与用于与第四设计信息验证的第三设计信息,为相同的或者不同的设计信息;所述第三设计信息的格式包括但不限于一种或多种格式;用于与第二设计信息验证的第三设计信息格式、与用于与第四设计信息验证的第三设计信息格式,为相同的或者不同的格式;

59.芯片或芯片模块的第四设计信息,所述第四设计信息包括但不限于数字芯片或数字芯片模块的rtl代码;所述第四设计信息包括但不限于所有或者部分的所述设计信息;用于与第二设计信息验证的第四设计信息,是所述第四设计信息中的所有设计信息或者部分设计信息;用于与第三设计信息验证的第四设计信息,是所述第四设计信息中的所有设计信息或者部分设计信息;用于与第二设计信息验证的第四设计信息、与用于与第三设计信息验证的第四设计信息,为相同的或者不同的设计信息;所述第四设计信息的格式包括但不限于一种或多种格式;用于与第二设计信息验证的第四设计信息格式、与用于与第三设计信息验证的第四设计信息格式,为相同的或者不同的格式。

60.本发明实施例中,所述将所述实物信息与所述设计信息进行比对,包括但不限于以下一种或多种:

61.将芯片或芯片模块与封装基板间的实物连接关系、和/或芯片或芯片模块与其他芯片或芯片模块间的实物连接关系,与对应的设计连接关系进行比对,检查二者是否一致;

62.将封装基板的实物信息与对应的封装基板的设计信息进行比对,检查二者是否一

致;

63.将芯片或芯片模块的实物信息与对应的芯片或芯片模块的第一设计信息进行比对,检查二者是否一致;

64.所述比对包括但不限于以下一种或多种的比对:所有层、部分层、一层,层号的选取方法包括但不限于以下一种或多种:随机选取、按照规则选取、设定;对于其中一层,所述比对包括但不限于以下一种或多种的比对:整个区域、多个局部区域、一个局部区域,区域的选取方法包括但不限于以下一种或多种:随机选取、按照规则选取、设定。

65.本发明一个实施例中,所述将所述实物信息与所述设计信息进行比对之前,该方法还包括:

66.确认获取的设计信息的准确性。

67.本发明实施例中,所述比对的方法包括但不限于以下一种或多种:通过检测装置自动比对,通过人工比对;

68.当比对方法为通过检测装置自动比对时,需要判断所述实物信息的格式是否为检测装置所能识别和/或使用的格式;当所述实物信息的格式不是检测装置所能识别和/或使用的格式时,需要将所述实物信息的格式调整为检测装置所能识别和/或使用的格式;所述将所述实物信息的格式调整为检测装置所能识别和/或使用的格式的方法,包括但不限于以下一种或多种:将实物信息记录为实物图像、将实物连接关系转化为描述实物连接关系的表格;

69.当比对方法为通过检测装置自动比对时,需要判断所述设计信息的格式是否为检测装置所能识别和/或使用的格式;当所述设计信息的格式不是检测装置所能识别和/或使用的格式时,需要将所述设计信息的格式调整为检测装置所能识别和/或使用的格式;所述将所述设计信息的格式调整为检测装置所能识别和/或使用的格式的方法,包括但不限于以下一种或多种:将设计信息转化为设计图像、将设计连接关系转化为描述设计连接关系的表格;所述设计图像包括但不限于将设计信息保存为或/和转化为或/和记录为图像格式的图像;

70.所述判断所述实物信息和/或所述设计信息的格式是否为检测装置所能识别和/或使用的格式的方法,包括但不限于以下一种或多种:通过检测装置自动判断,通过人工判断;

71.所述将所述实物信息和/或所述设计信息的格式调整为检测装置所能识别和/或使用的格式的方法,包括但不限于以下一种或多种:通过检测装置自动调整,通过人工调整。

72.本发明实施例中,所述将所述实物信息与所述设计信息进行比对时,所述实物信息与所述设计信息的对应关系包括但不限于以下一种或多种:

73.相同层的对应关系;

74.相同区域的对应关系;

75.相同位置的对应关系;

76.相同位置比例的对应关系,所述相同位置比例的对应关系包括但不限于以下一种或多种:所述实物信息和/或实物图像中的位置、和整个实物信息和/或实物图像中各点之间的距离的比值,与所述设计信息和/或设计图像中的位置、和整个设计信息和/或设计图

像中各点之间的距离的比值均相同,则所述实物信息和/或实物图像位置、与所述设计信息和/或设计图像位置为对应关系;所述实物信息和/或实物图像中的位置、与所述设计信息和/或设计图像中的位置,在整个实物信息和/或整个实物图像和/或整个设计信息和/或整个设计图像等比例缩放后,整个实物信息和/或整个实物图像、与整个设计信息和/或整个设计图像重合时,位置亦重合,则所述实物信息和/或实物图像位置、与所述设计信息和/或设计图像位置为对应关系;

77.相同管脚名称的对应关系。

78.本发明实施例中,将实物信息或实物图像、与设计信息或设计图像进行比对时,该方法还包括:将实物信息或实物图像、与对应的设计信息或设计图像,各自拆分成一个或多个板块,实物信息或实物图像的板块、与设计信息或设计图像的板块保持对应关系,针对各板块分别开展比对,综合各板块的比对结果分析本次比对的结果;

79.其中,拆分成一个或多个板块的情况包括但不限于以下一种或多种:实物信息或实物图像、与设计信息或设计图像的比对内容集中在一个或多个局部区域中,按照集中的区域将其拆分成一个或多个板块;实物信息或实物图像、与设计信息或设计图像的比对内容,在不同区域的图形尺寸差异大、按照不同图形尺寸或者按照不同尺寸范围、将其拆分成一个或多个板块;

80.其中,拆分成板块后,如果某些板块中没有需要的比对内容,则该板块的比对省略或者不省略,该板块的比对省略时,所述综合各板块的比对结果分析本次比对的结果时,不计入该板块(如,实物信息或实物图像、与设计信息或设计图像的比对内容集中在一个或多个局部区域中,按照集中的区域将其拆分成一个或多个板块,则集中的局部区域之外的部分,没有比对内容,则这部分板块可以省略比对,分析比对结果时,也不再考虑这部分板块)。

81.本发明实施例中,将实物信息或实物图像、与设计信息或设计图像进行比对,和/或将实物信息板块或实物图像板块、与设计信息板块或设计图像板块进行比对,所述比对的比对方式包括但不限于以下一种或多种:整体比对、细化比对、采样比对;

82.所述比对的比对内容包括但不限于以下一种或多种:连接关系、几何形状、几何形状特征;

83.所述比对的比对精细程度使用颗粒度表示,所述比对精细程度与比对方式、方法、内容及目的相关,所述颗粒度包括但不限于比对所述比对内容的精确程度,所述颗粒度的最小极限包括但不限于以下一种或多种:相应信息和/或图像中的最小图形,相应信息和/或图像中的最小尺寸,相应信息和/或图像中的最小面积,根据相应信息和/或图像所设定的图形,根据相应信息和/或图像所设定的尺寸,根据相应信息和/或图像所设定的面积。

84.本发明实施例中,将实物信息或实物图像、与设计信息或设计图像进行比对,和/或将实物信息板块或实物图像板块、与设计信息板块或设计图像板块进行比对,该方法还包括但不限于以下一种或多种:

85.针对要比对的实物图像和/或设计图像和/或实物图像板块和/或设计图像板块,调整实物图像和/或设计图像和/或实物图像板块和/或设计图像板块的分辨率和/或像素数量,在所述调整结果的基础上针对实物图像与设计图像、和/或实物图像板块与设计图像板块,进行比对;

86.当所述比对方法为通过检测装置自动比对时,针对本次计划比对的颗粒度,根据实物图像和/或设计图像和/或实物图像板块和/或设计图像板块的分辨率、和/或本次计划比对的颗粒度在实物图像和/或设计图像和/或实物图像板块和/或设计图像板块中包含的像素数量,以及检测装置的比对能力,调整实物图像和/或设计图像和/或实物图像板块和/或设计图像板块的分辨率和/或像素数量,在所述调整结果的基础上针对实物图像与设计图像、和/或实物图像板块与设计图像板块,进行比对;

87.所述检测装置的比对能力包括但不限于:检测装置在所述颗粒度下为完成比对、针对实物图像和/或设计图像和/或实物图像板块和/或设计图像板块各自需要的最小分辨率、和/或所述颗粒度需包含的最小像素数量;

88.所述调整的方法包括但不限于:针对本次计划比对的颗粒度,确保比对准确的前提下,减小实物图像和/或设计图像和/或实物图像板块和/或设计图像板块的分辨率和/或像素数量,使实物图像和/或设计图像和/或实物图像板块和/或设计图像板块的分辨率减小、和/或实物图像和/或设计图像和/或实物图像板块和/或设计图像板块中所述颗粒度所包含的像素数量减小,且大于等于检测装置的比对能力。

89.本发明实施例中,采用所述整体比对的方式,包括但不限于以下一种或多种:

90.针对整个所述实物信息或实物图像、与设计信息或设计图像的比对,和/或针对整个所述实物信息板块或实物图像板块、与设计信息板块或设计图像板块的比对;

91.所述整体比对包括但不限于以下一种或多种:整体精细比对、整体粗略比对;

92.整体精细比对时,所述比对的颗粒度已达最小极限;

93.整体粗略比对时,所述比对的颗粒度大于最小极限,所述比对内容体现为包括但不限于以下一种或多种:连接关系、芯片面积、芯片轮廓、封装基板面积、封装基板轮廓、图形概貌、图形分布特点、模块结构;

94.针对整个所述实物信息或实物图像、与设计信息或设计图像的整体精细比对的适用情况包括但不限于以下一种或多种:完成所述整体精细比对所需时间小于等于第一预设门限;所述实物图像的像素数量小于等于第二预设门限;所述设计图像的像素数量小于等于第三预设门限;所述实物图像的分辨率小于等于第四预设门限;所述设计图像的分辨率小于等于第五预设门限;所述实物信息和/或实物图像和/或设计信息和/或设计图像的面积小于等于第六预设门限;所述实物信息和/或实物图像和/或设计信息和/或设计图像中的最小图形的面积大于等于第七预设门限;

95.针对整个所述实物信息板块或实物图像板块、与设计信息板块或设计图像板块的整体精细比对的适用情况包括但不限于以下一种或多种:完成所述板块的整体精细比对所需时间小于等于第八预设门限;所述实物图像板块的像素数量小于等于第九预设门限;所述设计图像板块的像素数量小于等于第十预设门限;所述实物图像板块的分辨率小于等于第十一预设门限;所述设计图像板块的分辨率小于等于第十二预设门限;所述实物信息板块和/或实物图像板块和/或设计信息板块和/或设计图像板块的面积小于等于第十三预设门限;所述实物信息板块和/或实物图像板块和/或设计信息板块和/或设计图像板块中的最小图形的面积大于等于第十四预设门限;

96.针对整个所述实物信息或实物图像、与设计信息或设计图像的整体粗略比对的适用情况包括但不限于以下一种或多种:完成所述整体精细比对所需时间大于等于所述第十

五预设门限;所述实物图像的像素数量大于等于第十六预设门限;所述设计图像的像素数量大于等于第十七预设门限;所述实物图像的分辨率大于等于第十八预设门限;所述设计图像的分辨率大于等于第十九预设门限;所述实物信息和/或实物图像和/或设计信息和/或设计图像的面积大于等于第二十预设门限;所述实物信息和/或实物图像和/或设计信息和/或设计图像中的最小图形的面积小于等于第二十一预设门限;整体粗略比对与所述其他比对方式相结合;

97.针对整个所述实物信息板块或实物图像板块、与设计信息板块或设计图像板块的整体粗略比对的适用情况包括但不限于以下一种或多种:完成所述板块的整体精细比对所需时间大于等于所述第二十二预设门限;所述实物图像板块的像素数量大于等于第二十三预设门限;所述设计图像板块的像素数量大于等于第二十四预设门限;所述实物图像板块的分辨率大于等于第二十五预设门限;所述设计图像板块的分辨率大于等于第二十六预设门限;所述实物信息板块和/或实物图像板块和/或设计信息板块和/或设计图像板块的面积大于等于第二十七预设门限;所述实物信息板块和/或实物图像板块和/或设计信息板块和/或设计图像板块中的最小图形的面积小于等于第二十八预设门限;整体粗略比对与所述其他比对方式相结合。

98.本发明实施例中,采用所述细化比对的方式,包括但不限于以下一种或多种:

99.针对所述实物信息或实物图像、与设计信息或设计图像的比对,和/或所述实物信息板块或实物图像板块、与设计信息板块或设计图像板块的比对,针对包括但不限于以下一种或多种的区域,逐步缩小比对区域和/或减小颗粒度,开展一次或者多次比对:整体比对未通过的区域、整体比对通过后感兴趣或认为关键的区域、实现复杂的区域、功能关键的区域、整个区域;

100.所述开展一次或者多次比对时,细化极限为比对区域已缩小至相应信息和/或图像和/或信息板块和/或图像板块中的最小图形和/或最小尺寸、和/或颗粒度已达最小极限,细化比对需达到或者不需达到所述细化极限。

101.本发明实施例中,采用所述采样比对的方式,包括但不限于以下一种或多种:

102.针对所述实物信息或实物图像、与设计信息或设计图像的比对,和/或所述实物信息板块或实物图像板块、与设计信息板块或设计图像板块的比对,计算和/或设定可用于比对的面积(即此面积可以通过计算获得,和/或设定);

103.根据可用于比对的面积、从实物信息或实物图像或实物信息板块或实物图像板块中选取若干采样块,所述若干采样块的面积之和不得超过所述可用于比对的面积;

104.根据可用于比对的面积、从设计信息或设计图像或设计信息板块或设计图像板块中选取若干采样块,所述若干采样块的面积之和不得超过所述可用于比对的面积;

105.所述实物信息或实物图像或实物信息板块或实物图像板块中选取的采样块与所述设计信息或设计图像或设计信息板块或设计图像板块中选取的采样块保持对应关系;

106.采样块的选取方法包括但不限于以下一种或多种:随机采样,按照规则采样,正比于图形密度和/或复杂度分配采样块数量,正比于图形密度和/或复杂度分配采样块的面积,设定;

107.将实物信息或实物图像或实物信息板块或实物图像板块中的采样块、与对应的设计信息或设计图像或设计信息板块或设计图像板块中的采样块进行比对;

108.综合各采样块的比对结果分析本采样比对的结果;

109.采样比对的精细极限为颗粒度已达最小极限,采样比对需达到或者不需达到所述精细极限。

110.本发明实施例中,计算可用于比对的面积,包括但不限于以下一种或多种:

111.针对实物信息或实物图像或实物信息板块或实物图像板块、与设计信息或设计图像或设计信息板块或设计图像板块,根据完成单位面积比对所需要的时间,以及本次比对预期完成的时间,计算可用于比对的面积;

112.所述计算方法包括但不限于:可用于比对的面积=单位面积*本次比对预期完成的时间/完成单位面积比对所需要的时间。

113.本发明实施例中,所述最小图形和/或最小尺寸和/或最小面积的获取方法,包括但不限于以下一种或多种:

114.从相应的设计信息和/或实物信息和/或设计信息板块和/或实物信息板块中获取最小尺寸,所述获取的方法包括但不限于获取以下一种或多种信息:最小线宽、特征尺寸、工艺制程、栅极长度、沟道长度;

115.基于最小尺寸进一步分析获取最小图形和/或最小面积;

116.在相应的设计图像和/或实物图像和/或设计图像板块和/或实物图像板块中识别最小图形和/或最小尺寸和/或最小面积。

117.本发明实施例中,在包括但不限于以下一种或多种情况下,该方法还包括调整相应分辨率和/或像素数量后再比对:

118.图像比对开始前和/或拆分板块后和/或整体比对时,调整实物图像和/或设计图像和/或实物图像板块和/或设计图像板块的分辨率和/或像素数量后再比对;

119.细化比对缩小比对区域和/或减小颗粒度后,针对缩小后和/或减小颗粒度后的区域,调整相应图像的分辨率和/或像素数量后再比对;

120.选取采样块后,针对各采样块,调整相应图像的分辨率和/或像素数量后再比对。

121.本发明一个实施例中,该方法还包括:

122.针对包括但不限于以下一种或多种情况,调整比对的实现算法:不同的比对目的、不同的比对内容、不同的对比方法、不同的对比方式、比对中不同的工作阶段。

123.本发明实施例中,所述对所述设计信息进行验证,包括但不限于以下一种或多种:

124.将芯片或芯片模块的第一设计信息与对应的第二设计信息进行验证,验证方法包括但不限于lvs检查或验证;

125.将芯片或芯片模块的第二设计信息与对应的第三设计信息进行验证,和/或将芯片或芯片模块的第二设计信息与对应的第四设计信息进行验证,验证方法包括但不限于形式验证;

126.将芯片或芯片模块的第三设计信息,与对应的第四设计信息进行验证,验证方法包括但不限于形式验证。

127.本发明一个实施例中,所述对所述设计信息进行验证前,该方法还包括:

128.确认获取的设计信息的准确性。

129.本发明实施例中,所述确认获取的设计信息的准确性的方法包括但不限于以下一种或多种:

130.对于获取的用于比对的第一设计信息、与获取的用于验证的第一设计信息,确认其中的交叠部分和/或重复部分设计信息相同、和/或保持一致;所述确认所述交叠部分和/或重复部分的设计信息相同、和/或保持一致的方法,包括但不限于以下一种或多种:将获取的用于比对的第一设计信息格式、与获取的用于验证的第一设计信息格式统一,针对交叠部分和/或重复部分进行图像比对,针对交叠部分和/或重复部分进行图形比对,针对交叠部分和/或重复部分进行相似性比对,确定相似度大于等于第二十九预设门限,确定获取的用于比对的第一设计信息与获取的用于验证的第一设计信息中、其中一种信息的所有或者部分信息是从另一种信息中提取所有或者部分信息获得、和/或其中一种信息的所有或者部分信息是由另一种信息格式转换后从中提取所有或者部分信息获得;

131.将获取的用于比对的第一设计信息格式、与获取的用于验证的第一设计信息格式统一;所述将二者的格式统一的方法包括但不限于以下一种或多种:将两种格式中的一种格式转换成另一种格式,将两种格式均转化成第三种格式;所述第三种格式是指除获取的用于比对的第一设计信息格式、获取的用于验证的第一设计信息格式之外的格式;

132.对于获取的用于与第一设计信息验证的第二设计信息、获取的用于与第三设计信息验证的第二设计信息、与获取的用于与第四设计信息验证的第二设计信息中,对于三者中任意和/或设定的一种或多种两两组合的组合内部之间、和/或三者之间,确认交叠部分和/或重复部分设计信息相同、和/或保持一致;所述确认所述交叠部分和/或重复部分的设计信息相同、和/或保持一致的方法,包括但不限于以下一种或多种:将设计信息格式统一;针对交叠部分和/或重复部分进行图像比对;针对交叠部分和/或重复部分进行图形比对;针对交叠部分和/或重复部分进行相似性比对;确定相似度大于等于第三十预设门限;确定获取的用于与第一设计信息验证的第二设计信息、获取的用于与第三设计信息验证的第二设计信息、与获取的用于与第四设计信息验证的第二设计信息中,其中一种或多种信息的所有或者部分信息、是从另一种或多种信息中提取所有或者部分信息获得,和/或其中一种或多种信息的所有或者部分信息是由另一种或多种信息格式转换后从中提取所有或者部分信息获得;所述确认所述交叠部分和/或重复部分的设计信息相同、和/或保持一致的方法的应用场景,包括但不限于:对于模数混合芯片,确认其中的数字芯片模块的门级网表在格式转换为晶体管级的网表后,其内容与芯片晶体管级的网表中的数字芯片模块部分,相同或者保持一致;

133.对于获取的用于与第一设计信息验证的第二设计信息、获取的用于与第三设计信息验证的第二设计信息、与获取的用于与第四设计信息验证的第二设计信息中,对于三者中任意和/或设定的一种或多种两两组合的组合内部之间、和/或三者之间,将设计信息格式统一;所述将设计信息格式统一的方法包括但不限于以下一种或多种:对于两两组合的组合内部之间将两种格式中的一种格式转换成另一种格式,对于两两组合的组合内部之间将两种格式均转化成第三种格式,对于两两组合的组合内部之间所述第三种格式是指除组合中的设计信息格式之外的格式,对于三者之间将格式统一成三者格式中的一种格式,对于三者之间将三者格式均转化成第四种格式,对于三者之间所述第四种格式是指除三者中的设计信息格式之外的格式;

134.对于获取的用于与第二设计信息验证的第三设计信息、与获取的用于与第四设计信息验证的第三设计信息,确认其中的交叠部分和/或重复部分设计信息相同、和/或保持

一致;所述确认所述交叠部分和/或重复部分的设计信息相同、和/或保持一致的方法,包括但不限于以下一种或多种:将获取的用于与第二设计信息验证的第三设计信息格式、与获取的用于与第四设计信息验证的第三设计信息格式统一,针对交叠部分和/或重复部分进行图像比对,针对交叠部分和/或重复部分进行图形比对,针对交叠部分和/或重复部分进行相似性比对,确定相似度大于等于第三十一预设门限,确定获取的用于与第二设计信息验证的第三设计信息与获取的用于与第四设计信息验证的第三设计信息中、其中一种信息的所有或者部分信息是从另一种信息中提取所有或者部分信息获得、和/或其中一种信息的所有或者部分信息是由另一种信息格式转换后从中提取所有或者部分信息获得;

135.将获取的用于与第二设计信息验证的第三设计信息格式、与获取的用于与第四设计信息验证的第三设计信息格式统一;所述将二者的格式统一的方法包括但不限于以下一种或多种:将两种格式中的一种格式转换成另一种格式,将两种格式均转化成第三种格式;所述第三种格式是指除获取的用于与第二设计信息验证的第三设计信息格式、获取的用于与第四设计信息验证的第三设计信息格式之外的格式;

136.对于获取的用于与第二设计信息验证的第四设计信息、与获取的用于与第三设计信息验证的第四设计信息,确认其中的交叠部分和/或重复部分设计信息相同、和/或保持一致;所述确认所述交叠部分和/或重复部分的设计信息相同、和/或保持一致的方法,包括但不限于以下一种或多种:将获取的用于与第二设计信息验证的第四设计信息格式、与获取的用于与第三设计信息验证的第四设计信息格式统一,针对交叠部分和/或重复部分进行图像比对,针对交叠部分和/或重复部分进行图形比对,针对交叠部分和/或重复部分进行相似性比对,确定相似度大于等于第三十二预设门限,确定获取的用于与第二设计信息验证的第四设计信息与获取的用于与第三设计信息验证的第四设计信息中、其中一种信息的所有或者部分信息是从另一种信息中提取所有或者部分信息获得、和/或其中一种信息的所有或者部分信息是由另一种信息格式转换后从中提取所有或者部分信息获得;

137.将获取的用于与第二设计信息验证的第四设计信息格式、与获取的用于与第三设计信息验证的第四设计信息格式统一;所述将二者的格式统一的方法包括但不限于以下一种或多种:将两种格式中的一种格式转换成另一种格式,将两种格式均转化成第三种格式;所述第三种格式是指除获取的用于与第二设计信息验证的第四设计信息格式、获取的用于与第三设计信息验证的第四设计信息格式之外的格式;

138.确认获取的第二设计信息中的门级网表为后端网表、和/或非前端网表;

139.确认获取的第三设计信息中的门级网表为前端网表、和/或非后端网表;

140.所述确认获取的第二设计信息中的门级网表为后端网表、和/或非前端网表,和/或确认获取的第三设计信息中的门级网表为前端网表、和/或非后端网表的方法,包括但不限于以下一种或多种:关键词检索;将获取的第二设计信息中的门级网表、与获取的第三设计信息中的门级网表,进行相似度比对、和/或确定相似度小于等于第三十三预设门限;

141.确认获取的rtl代码为寄存器传输级描述、和/或非其他级别描述,所述其他级别描述包括但不限于门级描述;

142.通过所述获取的设计信息的文件后缀名,确认所述获取的设计信息的准确性。

143.本发明实施例中,所述对所述设计信息进行验证时,所述设计信息之间的对应关系包括但不限于以下一种或多种:相同模块的对应关系、相同单元的对应关系、相同功能的

对应关系、相同逻辑的对应关系、相同连接的对应关系。

144.本发明实施例中,开展所述验证时,确认验证的设置或/和条件,所述确认验证的设置或/和条件的方法,包括但不限于以下一种或多种:

145.所述验证为lvs验证时,通过分析lvs验证针对的设计信息、或/和查看lvs验证针对的设计信息所对应的设计说明,确认lvs验证的设置或/和条件;所述lvs验证的设置或/和条件包括但不限于以下一种或多种:顶层设计、顶层单元、顶层逻辑、顶层模块;

146.所述验证为形式验证时,通过分析形式验证针对的设计信息、或/和查看形式验证针对的设计信息所对应的设计说明,确认形式验证的设置或/和条件;所述形式验证的设置或/和条件包括但不限于以下一种或多种:顶层设计、顶层单元、顶层逻辑、顶层模块、常量设置;

147.验证设置或/和条件中的顶层设计和/或顶层单元和/或顶层逻辑和/或顶层模块,与验证针对的设计信息相关,是所述芯片或芯片模块的所有或者部分的设计信息;所述验证设置的顶层设计和/或顶层单元和/或顶层逻辑和/或顶层模块,是所述芯片的部分的设计信息的应用场景,包括但不限于:对于模数混合芯片,形式验证设置或/和条件中的顶层设计和/或顶层单元和/或顶层逻辑和/或顶层模块,为模数混合芯片中的数字芯片模块。

148.本发明实施例中,开展所述验证时,对验证的一项或多项结果或/和报告做综合分析,判断本次验证是否通过;所述验证为形式验证时,所述验证的结果或/和报告包括但不限于以下一种或多种:比较点匹配检查结果、验证结果、验证报告。

149.本发明实施例中,所述基于比对结果和/或验证结果,对芯片或芯片模块的自主度和/或可控度进行判定,包括但不限于以下一种或多种:

150.根据芯片或芯片模块的特点,确定为判定所述芯片或芯片模块的自主度和/或可控度,所需要的比对种类和/或验证种类;

151.针对所述需要的比对种类和/或验证种类,根据所述各种类所代表的环节的难易程度和/或关键程度,分配所述各种需要的比对和/或验证各自对应的分值;

152.针对所述需要的比对和/或验证中的每一种,在实际开展并通过时,所述芯片或芯片模块获得该种比对和/或验证对应的分值;

153.针对所述需要的比对和/或验证中的每一种,在实际开展未通过或实际未开展时,所述芯片或芯片模块不获得该种比对和/或验证对应的分值;

154.综合实际开展的各种比对和/或验证的结果,在所述芯片或芯片模块获得的各种比对和/或验证对应的分值中,梳理出无效分值;

155.在所述芯片或芯片模块获得的各种比对和/或验证对应的分值中、去除无效分值、其余分值为有效分值,将有效分值求和、并将此求和结果作为所述芯片或芯片模块的最终得分;

156.根据所述芯片或芯片模块的最终得分,对芯片或芯片模块的自主度和/或可控度进行判定。

157.本发明实施例中,所述综合实际开展的各种比对和/或验证的结果,在所述芯片或芯片模块获得的各种比对和/或验证对应的分值中,梳理出无效分值,包括但不限于以下一种或多种:

158.当所述芯片或芯片模块的实物信息与对应的第一设计信息进行比对未通过时,所

述芯片或芯片模块针对所述需要的验证中的每一种在实际开展并通过时所获得的对应分值均为无效分值;

159.当所述芯片或芯片模块的第一设计信息与对应的第二设计信息进行验证未通过时,所述芯片或芯片模块的第二设计信息与对应的第三设计信息的验证在实际开展并通过时所获得的对应分值为无效分值;

160.当所述芯片或芯片模块的第一设计信息与对应的第二设计信息进行验证未通过时,所述芯片或芯片模块的第二设计信息与对应的第四设计信息的验证在实际开展并通过时所获得的对应分值为无效分值;

161.当所述芯片或芯片模块的第一设计信息与对应的第二设计信息进行验证未通过时,所述芯片或芯片模块的第三设计信息与对应的第四设计信息的验证在实际开展并通过时所获得的对应分值为无效分值;

162.当所述芯片或芯片模块的第二设计信息与对应的第三设计信息进行验证未通过、且所述芯片或芯片模块的第二设计信息与对应的第四设计信息进行验证未通过时,所述芯片或芯片模块的第三设计信息与对应的第四设计信息的验证在实际开展并通过时所获得的对应分值为无效分值。

163.本发明实施例中,对于由一个或多个芯片模块组成的芯片,该芯片的自主度和/或可控度的判定包括但不限于以下一种或多种:

164.针对芯片中的各芯片模块,根据各芯片模块实现的难易程度和/或关键程度,分配相应的权值,芯片的得分为各芯片模块得分的加权求和值,基于所述加权求和值对芯片的自主度和/或可控度进行判定;

165.所述分配相应的权值,需要确保一个既定功能的芯片在不同方案下由一个或多个芯片模块组成时,在相同的自主度和/或可控度所对应的得分均相同;所述确保在相同的自主度和/或可控度所对应的得分均相同的实现方法包括但不限于以下一种或多种:权值分配归一化,在不同方案下、所述既定功能的芯片的各芯片模块的权值之和均相同,判定所述各芯片模块自主度和/或可控度最高时、所述各芯片模块的得分均相同,所述各芯片模块的满分均相同;

166.针对芯片中的各个芯片模块,在确定各个芯片模块的实物信息时,确保各芯片模块的实物信息不交叠和/或不重复、且各芯片模块的实物信息的总和为整个芯片的实物信息;

167.针对芯片中的各个芯片模块,在确定各个芯片模块的设计信息时,确保各芯片模块的设计信息不交叠和/或不重复、且各芯片模块的设计信息的总和为整个芯片的设计信息;

168.各自芯片模块的实物信息与设计信息保持对应的关系。

169.(上述确保各芯片模块的实物信息不交叠和/或不重复、和/或确保各芯片模块的设计信息不交叠和/或不重复的目的之一,是避免针对同一比对内容和/或验证内容重复计分。例如:在包括但不限于以下一种或多种的情况下,确定各芯片模块的实物信息、和/或确定各芯片模块的设计信息时,确保各芯片模块的实物信息不交叠和/或不重复、和/或确保各芯片模块的设计信息不交叠和/或不重复:多个芯片模块放置在同一封装基板上时,针对封装基板的实物信息与对应的设计信息,根据其与各芯片模块的关系进行划分,确保各芯

片模块所分配到的封装基板的实物信息不交叠、且其总和恰为封装基板的所有实物信息,确保各芯片模块所分配到的封装基板的设计信息不交叠、且其总和恰为封装基板的所有设计信息;多个芯片模块之间有连接时,针对芯片模块之间的实物连接关系与对应的设计连接关系,根据其与各芯片模块的关系进行划分,确保各芯片模块所分配到的芯片模块之间的实物连接关系不交叠、且其总和恰为各芯片模块之间的所有实物连接关系,确保各芯片模块所分配到的芯片模块之间的设计连接关系不交叠、且其总和恰为各芯片模块之间的所有设计连接关系。)

170.本发明实施例中,所述组成所述芯片的芯片模块中有相同型号的芯片模块时,将所述相同型号的芯片模块统一视作检测的一个整体芯片模块,统一计算一次分值、分配一个权值;所述将所述相同型号的芯片模块统一视作检测的一个整体芯片模块的处理方法包括但不限于以下一种或多种:

171.将所述相同型号的芯片模块的实物信息的总和确定为所述检测的一个整体芯片模块的实物信息,将所述相同型号的芯片模块的设计信息的总和确定为所述检测的一个整体芯片模块的设计信息,并针对所述检测的一个整体芯片模块计算得分;

172.从所述相同型号的芯片模块中,随机或按照规则选取一个芯片模块,将其得分作为所述检测的一个整体芯片模块的得分;

173.针对所述相同型号的芯片模块,从中选取所有数量或者部分数量的芯片模块,分别计算选取的各个芯片模块的得分,将选取的各个芯片模块的得分的平均值作为所述检测的一个整体芯片模块的分值。

174.本发明实施例中,所述判定由一个或多个芯片模块组成的芯片的自主度和/或可控度的方法的适用范围,包括但不限于以下一种或多种:

175.由数字芯片模块和模拟芯片模块共同组成的模数混合芯片;

176.由多个裸片(即所述芯片模块中的一种)封装在一起形成的多芯片组件mcm(即所述芯片中的一种);

177.射频前端模组。

178.为了实现上述方法实施例,本发明实施例还提供了一种芯片或芯片模块的检测装置,如图2所示,该装置包括:

179.信息确定模块201,用于确定芯片或芯片模块的实物信息,和/或确定芯片或芯片模块的设计信息;

180.信息处理模块202,用于将所述实物信息与所述设计信息进行比对,和/或对所述设计信息进行验证;

181.判定模块203,用于基于比对结果和/或验证结果,对芯片或芯片模块的自主度和/或可控度进行判定。

182.本发明实施例中,所述芯片包括但不限于以下一种或多种:

183.封装了一个或多个裸片的芯片;

184.未封装的裸片。

185.本发明实施例中,所述芯片模块包括但不限于以下一种或多种:

186.封装了一个或多个裸片的芯片中的裸片;

187.裸片中的功能模块。

188.本发明实施例中,所述实物信息包括但不限于以下一种或多种:

189.芯片或芯片模块与封装基板间的实物连接关系、和/或芯片或芯片模块与其他芯片或芯片模块间的实物连接关系,所述实物连接关系包括但不限于以下一种或多种表述形式:连接关系实物、描述连接关系的实物图、描述实物连接关系的表格、描述实物连接关系的管脚实物名称及由名称表述的实物连接关系;

190.封装基板的实物信息,所述实物信息包括但不限于以下一种或多种:封装基板实物、封装基板实物线路或线路图、封装基板实物布局或布局图、封装基板实物布线或布线图、封装基板实物电路或电路图;

191.芯片或芯片模块的实物信息,所述实物信息包括但不限于以下一种或多种:芯片或芯片模块实物、芯片或芯片模块实物版图、芯片或芯片模块实物布图、芯片或芯片模块实物布局布线或布局布线图、芯片或芯片模块实物电路或电路图;

192.其中,所述实物信息包括但不限于以下一种或多种的实物信息:所有层、部分层、一层,层号的选取方法包括但不限于以下一种或多种:随机选取、按照规则选取、设定;对于其中一层,所述实物信息包括但不限于以下一种或多种的实物信息:整个区域、多个局部区域、一个局部区域,区域的选取方法包括但不限于以下一种或多种:随机选取、按照规则选取、设定。

193.本发明实施例中,所述实物信息的获取方法,包括但不限于以下一种或多种:

194.直接取得一个或多个待测芯片或芯片模块并获取实物信息;

195.随机或按照规则选取一个或多个待测芯片或芯片模块并获取实物信息;

196.直接通过包括但不限于以下一种或多种方式获取实物信息:电子计算机断层扫描ct、x射线、x光、放射线、超声、无损检测;

197.对已封装的芯片进行芯片开盖并获取实物信息;

198.针对芯片或芯片模块与封装基板间的实物连接关系、和/或芯片或芯片模块与其他芯片或芯片模块间的实物连接关系被遮挡的情况,通过包括但不限于以下一种或多种方式获取实物连接关系:ct、x射线、x光、放射线、超声、无损检测、去层、平磨、磨削、研磨、打磨、抛光、腐蚀、刻蚀、剖片、解剖、染色;所述实物连接关系被遮挡的情况包括但不限于倒装焊的芯片中的所述实物连接关系被遮挡;

199.将芯片或芯片模块与封装基板分离、和/或将芯片或芯片模块与其他芯片或芯片模块分离,所述分离的方法包括但不限于以下一种或多种:断开或移除或去除连接线、腐蚀、刻蚀、加热、去层、平磨、磨削、研磨、打磨、剖片、解剖、取下芯片;

200.通过包括但不限于以下一种或多种方式获取一层或多层的实物信息:直接获取、通过显微镜和/或显微成像仪器和/或ct和/或x射线和/或x光和/或放射线和/或超声和/或无损检测获取、去层、平磨、磨削、研磨、打磨、抛光、腐蚀、刻蚀、剖片、解剖、染色、断开或移除或去除连接线;

201.通过显微镜和/或显微成像仪器和/或ct和/或x射线和/或x光和/或放射线和/或超声和/或无损检测、与拍照或/和图像采集或/和录像相结合,或者,直接拍照或/和图像采集或/和录像的方式获取并记录实物信息对应的实物图像、影像或视频;所述实物图像、影像或视频为一个文件、或者多个文件、或者由多个文件拼接或合成的一个整体文件;

202.通过显微镜和/或显微成像仪器和/或ct和/或x射线和/或x光和/或放射线和/或

超声和/或无损检测、与肉眼观察相结合,或者直接肉眼观察的方式获取实物信息及对应的实物图像、影像。

203.本发明实施例中,所述信息确定模块201取得或者选取多个待测芯片或芯片模块并获取实物信息,包括但不限于以下一种或多种:

204.为获取多个样本,对实物信息、或/和实物信息与设计信息的比对、或/和芯片或芯片模块的自主度和/或可控度做统计分析,取得或者选取多个相同型号的芯片或芯片模块、从各芯片或芯片模块中获取相同的实物信息;

205.对于获取实物信息时有破坏性操作或/和从一个芯片或芯片模块中只能获取部分实物信息的情况,取得或者选取多个相同型号的芯片或芯片模块,并从各芯片或芯片模块中获取不同的实物信息、或同时获取相同和不同的实物信息;

206.为判定由多个芯片模块共同组成的芯片的自主度和/或可控度,对芯片中的多个芯片模块分别获取各自的实物信息、开展自主度和/或可控度的判定,基于此结果对芯片的自主度和/或可控度进行判定。

207.本发明实施例中,所述设计信息包括但不限于以下一种或多种:

208.芯片或芯片模块与封装基板间的设计连接关系、和/或芯片或芯片模块与其他芯片或芯片模块间的设计连接关系,所述设计连接关系包括但不限于以下一种或多种表述形式:描述连接关系的设计图、描述设计连接关系的表格、描述设计连接关系的管脚设计名称及由名称表述的设计连接关系;所述设计信息包括但不限于以下一种或多种的设计信息:所有层、部分层、一层,层号的选取方法包括但不限于以下一种或多种:随机选取、按照规则选取、设定;对于其中一层,所述设计信息包括但不限于以下一种或多种的设计信息:整个区域、多个局部区域、一个局部区域,区域的选取方法包括但不限于以下一种或多种:随机选取、按照规则选取、设定;所述设计连接关系的格式包括但不限于一种或多种格式;

209.封装基板的设计信息,所述设计信息包括但不限于以下一种或多种:封装基板设计线路或线路图、封装基板设计布局或布局图、封装基板设计布线或布线图、封装基板设计电路或电路图;所述设计信息包括但不限于以下一种或多种的设计信息:所有层、部分层、一层,层号的选取方法包括但不限于以下一种或多种:随机选取、按照规则选取、设定;对于其中一层,所述设计信息包括但不限于以下一种或多种的设计信息:整个区域、多个局部区域、一个局部区域,区域的选取方法包括但不限于以下一种或多种:随机选取、按照规则选取、设定;所述封装基板的设计信息的格式包括但不限于一种或多种格式;

210.芯片或芯片模块的第一设计信息,所述第一设计信息包括但不限于以下一种或多种:芯片或芯片模块设计版图、芯片或芯片模块设计布图、芯片或芯片模块设计布局布线或布局布线图;所述第一设计信息包括但不限于以下一种或多种的设计信息:所有层、部分层、一层,层号的选取方法包括但不限于以下一种或多种:随机选取、按照规则选取、设定;对于其中一层,所述第一设计信息包括但不限于以下一种或多种的设计信息:整个区域、多个局部区域、一个局部区域,区域的选取方法包括但不限于以下一种或多种:随机选取、按照规则选取、设定;用于比对的第一设计信息,是所述第一设计信息中的所有设计信息或者部分设计信息;用于验证的第一设计信息,是所述第一设计信息中的所有设计信息或者部分设计信息;用于比对的第一设计信息与用于验证的第一设计信息,为相同的或者不同的设计信息;所述第一设计信息的格式包括但不限于一种或多种格式;用于比对的第一设计

信息格式与用于验证的第一设计信息格式,为相同的或者不同的格式;

211.芯片或芯片模块的第二设计信息,所述第二设计信息包括但不限于芯片或芯片模块的原理图和/或网表,所述原理图和/或网表包括但不限于以下一种或多种:原理图、原理图对应的网表、晶体管级的网表、数字芯片或数字芯片模块完成最终设计的门级网表、数字芯片或数字芯片模块第一设计信息对应的门级网表;所述第二设计信息包括但不限于所有或者部分的所述设计信息;用于与第一设计信息验证的第二设计信息,是所述第二设计信息中的所有设计信息或者部分设计信息;用于与第三设计信息验证的第二设计信息,是所述第二设计信息中的所有设计信息或者部分设计信息;用于与第四设计信息验证的第二设计信息,是所述第二设计信息中的所有设计信息或者部分设计信息;用于与第一设计信息验证的第二设计信息、用于与第三设计信息验证的第二设计信息、与用于与第四设计信息验证的第二设计信息中,任意两者之间为相同的或者不同的设计信息;所述第二设计信息的格式包括但不限于一种或多种格式;用于与第一设计信息验证的第二设计信息格式、用于与第三设计信息验证的第二设计信息格式、与用于与第四设计信息验证的第二设计信息格式中,任意两者之间为相同的或者不同的格式;

212.芯片或芯片模块的第三设计信息,所述第三设计信息包括但不限于数字芯片或数字芯片模块的寄存器传输级rtl代码综合形成的门级网表;所述第三设计信息包括但不限于所有或者部分的所述设计信息;用于与第二设计信息验证的第三设计信息,是所述第三设计信息中的所有设计信息或者部分设计信息;用于与第四设计信息验证的第三设计信息,是所述第三设计信息中的所有设计信息或者部分设计信息;用于与第二设计信息验证的第三设计信息、与用于与第四设计信息验证的第三设计信息,为相同的或者不同的设计信息;所述第三设计信息的格式包括但不限于一种或多种格式;用于与第二设计信息验证的第三设计信息格式、与用于与第四设计信息验证的第三设计信息格式,为相同的或者不同的格式;

213.芯片或芯片模块的第四设计信息,所述第四设计信息包括但不限于数字芯片或数字芯片模块的rtl代码;所述第四设计信息包括但不限于所有或者部分的所述设计信息;用于与第二设计信息验证的第四设计信息,是所述第四设计信息中的所有设计信息或者部分设计信息;用于与第三设计信息验证的第四设计信息,是所述第四设计信息中的所有设计信息或者部分设计信息;用于与第二设计信息验证的第四设计信息、与用于与第三设计信息验证的第四设计信息,为相同的或者不同的设计信息;所述第四设计信息的格式包括但不限于一种或多种格式;用于与第二设计信息验证的第四设计信息格式、与用于与第三设计信息验证的第四设计信息格式,为相同的或者不同的格式。

214.本发明实施例中,所述信息处理模块202将所述实物信息与所述设计信息进行比对,包括但不限于以下一种或多种:

215.将芯片或芯片模块与封装基板间的实物连接关系、和/或芯片或芯片模块与其他芯片或芯片模块间的实物连接关系,与对应的设计连接关系进行比对,检查二者是否一致;

216.将封装基板的实物信息与对应的封装基板的设计信息进行比对,检查二者是否一致;

217.将芯片或芯片模块的实物信息与对应的芯片或芯片模块的第一设计信息进行比对,检查二者是否一致;

218.所述比对包括但不限于以下一种或多种的比对:所有层、部分层、一层,层号的选取方法包括但不限于以下一种或多种:随机选取、按照规则选取、设定;对于其中一层,所述比对包括但不限于以下一种或多种的比对:整个区域、多个局部区域、一个局部区域,区域的选取方法包括但不限于以下一种或多种:随机选取、按照规则选取、设定。

219.本发明实施例中,所述信息处理模块202将所述实物信息与所述设计信息进行比对之前,所述信息确定模块201,还用于确认获取的设计信息的准确性。

220.本发明实施例中,所述信息处理模块202采用的所述比对的方法包括但不限于以下一种或多种:通过检测装置自动比对,通过人工比对;

221.当比对方法为通过检测装置自动比对时,需要判断所述实物信息的格式是否为检测装置所能识别和/或使用的格式;当所述实物信息的格式不是检测装置所能识别和/或使用的格式时,需要将所述实物信息的格式调整为检测装置所能识别和/或使用的格式;所述将所述实物信息的格式调整为检测装置所能识别和/或使用的格式的方法,包括但不限于以下一种或多种:将实物信息记录为实物图像、将实物连接关系转化为描述实物连接关系的表格;

222.当比对方法为通过检测装置自动比对时,需要判断所述设计信息的格式是否为检测装置所能识别和/或使用的格式;当所述设计信息的格式不是检测装置所能识别和/或使用的格式时,需要将所述设计信息的格式调整为检测装置所能识别和/或使用的格式;所述将所述设计信息的格式调整为检测装置所能识别和/或使用的格式的方法,包括但不限于以下一种或多种:将设计信息转化为设计图像、将设计连接关系转化为描述设计连接关系的表格;所述设计图像包括但不限于将设计信息保存为或/和转化为或/和记录为图像格式的图像;

223.所述判断所述实物信息和/或所述设计信息的格式是否为检测装置所能识别和/或使用的格式的方法,包括但不限于以下一种或多种:通过检测装置自动判断,通过人工判断;

224.所述将所述实物信息和/或所述设计信息的格式调整为检测装置所能识别和/或使用的格式的方法,包括但不限于以下一种或多种:通过检测装置自动调整,通过人工调整。

225.本发明实施例中,所述信息处理模块202将所述实物信息与所述设计信息进行比对时,所述实物信息与所述设计信息的对应关系包括但不限于以下一种或多种:

226.相同层的对应关系;

227.相同区域的对应关系;

228.相同位置的对应关系;

229.相同位置比例的对应关系,所述相同位置比例的对应关系包括但不限于以下一种或多种:所述实物信息和/或实物图像中的位置、和整个实物信息和/或实物图像中各点之间的距离的比值,与所述设计信息和/或设计图像中的位置、和整个设计信息和/或设计图像中各点之间的距离的比值均相同,则所述实物信息和/或实物图像位置、与所述设计信息和/或设计图像位置为对应关系;所述实物信息和/或实物图像中的位置、与所述设计信息和/或设计图像中的位置,在整个实物信息和/或整个实物图像和/或整个设计信息和/或整个设计图像等比例缩放后,整个实物信息和/或整个实物图像、与整个设计信息和/或整个

设计图像重合时,位置亦重合,则所述实物信息和/或实物图像位置、与所述设计信息和/或设计图像位置为对应关系;

230.相同管脚名称的对应关系。

231.本发明实施例中,所述信息处理模块202将实物信息或实物图像、与设计信息或设计图像进行比对时,还用于:将实物信息或实物图像、与对应的设计信息或设计图像,各自拆分成一个或多个板块,实物信息或实物图像的板块、与设计信息或设计图像的板块保持对应关系,针对各板块分别开展比对,综合各板块的比对结果分析本次比对的结果;

232.其中,拆分成一个或多个板块的情况包括但不限于以下一种或多种:实物信息或实物图像、与设计信息或设计图像的比对内容集中在一个或多个局部区域中,按照集中的区域将其拆分成一个或多个板块;实物信息或实物图像、与设计信息或设计图像的比对内容,在不同区域的图形尺寸差异大、按照不同图形尺寸或者按照不同尺寸范围、将其拆分成一个或多个板块;

233.其中,拆分成板块后,如果某些板块中没有需要的比对内容,则该板块的比对省略或者不省略,该板块的比对省略时,所述综合各板块的比对结果分析本次比对的结果时,不计入该板块。

234.本发明实施例中,所述信息处理模块202将实物信息或实物图像、与设计信息或设计图像进行比对,和/或将实物信息板块或实物图像板块、与设计信息板块或设计图像板块进行比对,所述比对的比对方式包括但不限于以下一种或多种:整体比对、细化比对、采样比对;

235.所述比对的比对内容包括但不限于以下一种或多种:连接关系、几何形状、几何形状特征;

236.所述比对的比对精细程度使用颗粒度表示,所述比对精细程度与比对方式、方法、内容及目的相关,所述颗粒度包括但不限于比对所述比对内容的精确程度,所述颗粒度的最小极限包括但不限于以下一种或多种:相应信息和/或图像中的最小图形,相应信息和/或图像中的最小尺寸,相应信息和/或图像中的最小面积,根据相应信息和/或图像所设定的图形,根据相应信息和/或图像所设定的尺寸,根据相应信息和/或图像所设定的面积。

237.本发明实施例中,所述信息处理模块202将实物信息或实物图像、与设计信息或设计图像进行比对,和/或将实物信息板块或实物图像板块、与设计信息板块或设计图像板块进行比对,还用于执行但不限于以下一种或多种:

238.针对要比对的实物图像和/或设计图像和/或实物图像板块和/或设计图像板块,调整实物图像和/或设计图像和/或实物图像板块和/或设计图像板块的分辨率和/或像素数量,在所述调整结果的基础上针对实物图像与设计图像、和/或实物图像板块与设计图像板块,进行比对;

239.当所述比对方法为通过检测装置自动比对时,针对本次计划比对的颗粒度,根据实物图像和/或设计图像和/或实物图像板块和/或设计图像板块的分辨率、和/或本次计划比对的颗粒度在实物图像和/或设计图像和/或实物图像板块和/或设计图像板块中包含的像素数量,以及检测装置的比对能力,调整实物图像和/或设计图像和/或实物图像板块和/或设计图像板块的分辨率和/或像素数量,在所述调整结果的基础上针对实物图像与设计图像、和/或实物图像板块与设计图像板块,进行比对;

240.所述检测装置的比对能力包括但不限于:检测装置在所述颗粒度下为完成比对、针对实物图像和/或设计图像和/或实物图像板块和/或设计图像板块各自需要的最小分辨率、和/或所述颗粒度需包含的最小像素数量;

241.所述调整的方法包括但不限于:针对本次计划比对的颗粒度,确保比对准确的前提下,减小实物图像和/或设计图像和/或实物图像板块和/或设计图像板块的分辨率和/或像素数量,使实物图像和/或设计图像和/或实物图像板块和/或设计图像板块的分辨率减小、和/或实物图像和/或设计图像和/或实物图像板块和/或设计图像板块中所述颗粒度所包含的像素数量减小,且大于等于检测装置的比对能力。

242.本发明实施例中,所述信息处理模块202采用所述整体比对的方式,包括但不限于以下一种或多种:

243.针对整个所述实物信息或实物图像、与设计信息或设计图像的比对,和/或针对整个所述实物信息板块或实物图像板块、与设计信息板块或设计图像板块的比对;

244.所述整体比对包括但不限于以下一种或多种:整体精细比对、整体粗略比对;

245.整体精细比对时,所述比对的颗粒度已达最小极限;

246.整体粗略比对时,所述比对的颗粒度大于最小极限,所述比对内容体现为包括但不限于以下一种或多种:连接关系、芯片面积、芯片轮廓、封装基板面积、封装基板轮廓、图形概貌、图形分布特点、模块结构;

247.针对整个所述实物信息或实物图像、与设计信息或设计图像的整体精细比对的适用情况包括但不限于以下一种或多种:完成所述整体精细比对所需时间小于等于第一预设门限;所述实物图像的像素数量小于等于第二预设门限;所述设计图像的像素数量小于等于第三预设门限;所述实物图像的分辨率小于等于第四预设门限;所述设计图像的分辨率小于等于第五预设门限;所述实物信息和/或实物图像和/或设计信息和/或设计图像的面积小于等于第六预设门限;所述实物信息和/或实物图像和/或设计信息和/或设计图像中的最小图形的面积大于等于第七预设门限;

248.针对整个所述实物信息板块或实物图像板块、与设计信息板块或设计图像板块的整体精细比对的适用情况包括但不限于以下一种或多种:完成所述板块的整体精细比对所需时间小于等于第八预设门限;所述实物图像板块的像素数量小于等于第九预设门限;所述设计图像板块的像素数量小于等于第十预设门限;所述实物图像板块的分辨率小于等于第十一预设门限;所述设计图像板块的分辨率小于等于第十二预设门限;所述实物信息板块和/或实物图像板块和/或设计信息板块和/或设计图像板块的面积小于等于第十三预设门限;所述实物信息板块和/或实物图像板块和/或设计信息板块和/或设计图像板块中的最小图形的面积大于等于第十四预设门限;

249.针对整个所述实物信息或实物图像、与设计信息或设计图像的整体粗略比对的适用情况包括但不限于以下一种或多种:完成所述整体精细比对所需时间大于等于所述第十五预设门限;所述实物图像的像素数量大于等于第十六预设门限;所述设计图像的像素数量大于等于第十七预设门限;所述实物图像的分辨率大于等于第十八预设门限;所述设计图像的分辨率大于等于第十九预设门限;所述实物信息和/或实物图像和/或设计信息和/或设计图像的面积大于等于第二十预设门限;所述实物信息和/或实物图像和/或设计信息和/或设计图像中的最小图形的面积小于等于第二十一预设门限;整体粗略比对与所述其

他比对方式相结合;

250.针对整个所述实物信息板块或实物图像板块、与设计信息板块或设计图像板块的整体粗略比对的适用情况包括但不限于以下一种或多种:完成所述板块的整体精细比对所需时间大于等于所述第二十二预设门限;所述实物图像板块的像素数量大于等于第二十三预设门限;所述设计图像板块的像素数量大于等于第二十四预设门限;所述实物图像板块的分辨率大于等于第二十五预设门限;所述设计图像板块的分辨率大于等于第二十六预设门限;所述实物信息板块和/或实物图像板块和/或设计信息板块和/或设计图像板块的面积大于等于第二十七预设门限;所述实物信息板块和/或实物图像板块和/或设计信息板块和/或设计图像板块中的最小图形的面积小于等于第二十八预设门限;整体粗略比对与所述其他比对方式相结合。

251.本发明实施例中,所述信息处理模块202采用所述细化比对的方式,包括但不限于以下一种或多种:

252.针对所述实物信息或实物图像、与设计信息或设计图像的比对,和/或所述实物信息板块或实物图像板块、与设计信息板块或设计图像板块的比对,针对包括但不限于以下一种或多种的区域,逐步缩小比对区域和/或减小颗粒度,开展一次或者多次比对:整体比对未通过的区域、整体比对通过后感兴趣或认为关键的区域、实现复杂的区域、功能关键的区域、整个区域;

253.所述开展一次或者多次比对时,细化极限为比对区域已缩小至相应信息和/或图像和/或信息板块和/或图像板块中的最小图形和/或最小尺寸、和/或颗粒度已达最小极限,细化比对需达到或者不需达到所述细化极限。

254.本发明实施例中,所述信息处理模块202采用所述采样比对的方式,包括但不限于以下一种或多种:

255.针对所述实物信息或实物图像、与设计信息或设计图像的比对,和/或所述实物信息板块或实物图像板块、与设计信息板块或设计图像板块的比对,计算和/或设定可用于比对的面积;

256.根据可用于比对的面积、从实物信息或实物图像或实物信息板块或实物图像板块中选取若干采样块,所述若干采样块的面积之和不得超过所述可用于比对的面积;

257.根据可用于比对的面积、从设计信息或设计图像或设计信息板块或设计图像板块中选取若干采样块,所述若干采样块的面积之和不得超过所述可用于比对的面积;

258.所述实物信息或实物图像或实物信息板块或实物图像板块中选取的采样块与所述设计信息或设计图像或设计信息板块或设计图像板块中选取的采样块保持对应关系;

259.采样块的选取方法包括但不限于以下一种或多种:随机采样,按照规则采样,正比于图形密度和/或复杂度分配采样块数量,正比于图形密度和/或复杂度分配采样块的面积,设定;

260.将实物信息或实物图像或实物信息板块或实物图像板块中的采样块、与对应的设计信息或设计图像或设计信息板块或设计图像板块中的采样块进行比对;

261.综合各采样块的比对结果分析本采样比对的结果;

262.采样比对的精细极限为颗粒度已达最小极限,采样比对需达到或者不需达到所述精细极限。

263.本发明实施例中,所述信息处理模块202计算可用于比对的面积,包括但不限于以下一种或多种:

264.针对实物信息或实物图像或实物信息板块或实物图像板块、与设计信息或设计图像或设计信息板块或设计图像板块,根据完成单位面积比对所需要的时间,以及本次比对预期完成的时间,计算可用于比对的面积;

265.所述计算方法包括但不限于:可用于比对的面积=单位面积*本次比对预期完成的时间/完成单位面积比对所需要的时间。

266.本发明实施例中,所述最小图形和/或最小尺寸和/或最小面积的获取方法,包括但不限于以下一种或多种:

267.从相应的设计信息和/或实物信息和/或设计信息板块和/或实物信息板块中获取最小尺寸,所述获取的方法包括但不限于获取以下一种或多种信息:最小线宽、特征尺寸、工艺制程、栅极长度、沟道长度;

268.基于最小尺寸进一步分析获取最小图形和/或最小面积;

269.在相应的设计图像和/或实物图像和/或设计图像板块和/或实物图像板块中识别最小图形和/或最小尺寸和/或最小面积。

270.本发明实施例中,在包括但不限于以下一种或多种情况下,所述信息处理模块202,还用于调整相应分辨率和/或像素数量后再比对:

271.图像比对开始前和/或拆分板块后和/或整体比对时,调整实物图像和/或设计图像和/或实物图像板块和/或设计图像板块的分辨率和/或像素数量后再比对;

272.细化比对缩小比对区域和/或减小颗粒度后,针对缩小后和/或减小颗粒度后的区域,调整相应图像的分辨率和/或像素数量后再比对;

273.选取采样块后,针对各采样块,调整相应图像的分辨率和/或像素数量后再比对。

274.本发明实施例中,所述信息处理模块202,还用于针对包括但不限于以下一种或多种情况,调整比对的实现算法:不同的比对目的、不同的比对内容、不同的对比方法、不同的对比方式、比对中不同的工作阶段。

275.本发明实施例中,所述信息处理模块202对所述设计信息进行验证,包括但不限于以下一种或多种:

276.将芯片或芯片模块的第一设计信息与对应的第二设计信息进行验证,验证方法包括但不限于lvs检查或验证;

277.将芯片或芯片模块的第二设计信息与对应的第三设计信息进行验证,和/或将芯片或芯片模块的第二设计信息与对应的第四设计信息进行验证,验证方法包括但不限于形式验证;

278.将芯片或芯片模块的第三设计信息,与对应的第四设计信息进行验证,验证方法包括但不限于形式验证。

279.本发明实施例中,所述信息处理模块202对所述设计信息进行验证前,所述信息确定模块201,还用于确认获取的设计信息的准确性。

280.本发明实施例中,所述信息确定模块201确认获取的设计信息的准确性的方法包含但不限于以下一种或多种:

281.对于获取的用于比对的第一设计信息、与获取的用于验证的第一设计信息,确认

其中的交叠部分和/或重复部分设计信息相同、和/或保持一致;所述确认所述交叠部分和/或重复部分的设计信息相同、和/或保持一致的方法,包括但不限于以下一种或多种:将获取的用于比对的第一设计信息格式、与获取的用于验证的第一设计信息格式统一,针对交叠部分和/或重复部分进行图像比对,针对交叠部分和/或重复部分进行图形比对,针对交叠部分和/或重复部分进行相似性比对,确定相似度大于等于第二十九预设门限,确定获取的用于比对的第一设计信息与获取的用于验证的第一设计信息中、其中一种信息的所有或者部分信息是从另一种信息中提取所有或者部分信息获得、和/或其中一种信息的所有或者部分信息是由另一种信息格式转换后从中提取所有或者部分信息获得;

282.将获取的用于比对的第一设计信息格式、与获取的用于验证的第一设计信息格式统一;所述将二者的格式统一的方法包括但不限于以下一种或多种:将两种格式中的一种格式转换成另一种格式,将两种格式均转化成第三种格式;所述第三种格式是指除获取的用于比对的第一设计信息格式、获取的用于验证的第一设计信息格式之外的格式;

283.对于获取的用于与第一设计信息验证的第二设计信息、获取的用于与第三设计信息验证的第二设计信息、与获取的用于与第四设计信息验证的第二设计信息中,对于三者中任意和/或设定的一种或多种两两组合的组合内部之间、和/或三者之间,确认交叠部分和/或重复部分设计信息相同、和/或保持一致;所述确认所述交叠部分和/或重复部分的设计信息相同、和/或保持一致的方法,包括但不限于以下一种或多种:将设计信息格式统一;针对交叠部分和/或重复部分进行图像比对;针对交叠部分和/或重复部分进行图形比对;针对交叠部分和/或重复部分进行相似性比对;确定相似度大于等于第三十预设门限;确定获取的用于与第一设计信息验证的第二设计信息、获取的用于与第三设计信息验证的第二设计信息、与获取的用于与第四设计信息验证的第二设计信息中,其中一种或多种信息的所有或者部分信息、是从另一种或多种信息中提取所有或者部分信息获得,和/或其中一种或多种信息的所有或者部分信息是由另一种或多种信息格式转换后从中提取所有或者部分信息获得;所述确认所述交叠部分和/或重复部分的设计信息相同、和/或保持一致的方法的应用场景,包括但不限于:对于模数混合芯片,确认其中的数字芯片模块的门级网表在格式转换为晶体管级的网表后,其内容与芯片晶体管级的网表中的数字芯片模块部分,相同或者保持一致;

284.对于获取的用于与第一设计信息验证的第二设计信息、获取的用于与第三设计信息验证的第二设计信息、与获取的用于与第四设计信息验证的第二设计信息中,对于三者中任意和/或设定的一种或多种两两组合的组合内部之间、和/或三者之间,将设计信息格式统一;所述将设计信息格式统一的方法包括但不限于以下一种或多种:对于两两组合的组合内部之间将两种格式中的一种格式转换成另一种格式,对于两两组合的组合内部之间将两种格式均转化成第三种格式,对于两两组合的组合内部之间所述第三种格式是指除组合中的设计信息格式之外的格式,对于三者之间将格式统一成三者格式中的一种格式,对于三者之间将三者格式均转化成第四种格式,对于三者之间所述第四种格式是指除三者中的设计信息格式之外的格式;

285.对于获取的用于与第二设计信息验证的第三设计信息、与获取的用于与第四设计信息验证的第三设计信息,确认其中的交叠部分和/或重复部分设计信息相同、和/或保持一致;所述确认所述交叠部分和/或重复部分的设计信息相同、和/或保持一致的方法,包括

但不限于以下一种或多种:将获取的用于与第二设计信息验证的第三设计信息格式、与获取的用于与第四设计信息验证的第三设计信息格式统一,针对交叠部分和/或重复部分进行图像比对,针对交叠部分和/或重复部分进行图形比对,针对交叠部分和/或重复部分进行相似性比对,确定相似度大于等于第三十一预设门限,确定获取的用于与第二设计信息验证的第三设计信息与获取的用于与第四设计信息验证的第三设计信息中、其中一种信息的所有或者部分信息是从另一种信息中提取所有或者部分信息获得、和/或其中一种信息的所有或者部分信息是由另一种信息格式转换后从中提取所有或者部分信息获得;

286.将获取的用于与第二设计信息验证的第三设计信息格式、与获取的用于与第四设计信息验证的第三设计信息格式统一;所述将二者的格式统一的方法包括但不限于以下一种或多种:将两种格式中的一种格式转换成另一种格式,将两种格式均转化成第三种格式;所述第三种格式是指除获取的用于与第二设计信息验证的第三设计信息格式、获取的用于与第四设计信息验证的第三设计信息格式之外的格式;

287.对于获取的用于与第二设计信息验证的第四设计信息、与获取的用于与第三设计信息验证的第四设计信息,确认其中的交叠部分和/或重复部分设计信息相同、和/或保持一致;所述确认所述交叠部分和/或重复部分的设计信息相同、和/或保持一致的方法,包括但不限于以下一种或多种:将获取的用于与第二设计信息验证的第四设计信息格式、与获取的用于与第三设计信息验证的第四设计信息格式统一,针对交叠部分和/或重复部分进行图像比对,针对交叠部分和/或重复部分进行图形比对,针对交叠部分和/或重复部分进行相似性比对,确定相似度大于等于第三十二预设门限,确定获取的用于与第二设计信息验证的第四设计信息与获取的用于与第三设计信息验证的第四设计信息中、其中一种信息的所有或者部分信息是从另一种信息中提取所有或者部分信息获得、和/或其中一种信息的所有或者部分信息是由另一种信息格式转换后从中提取所有或者部分信息获得;

288.将获取的用于与第二设计信息验证的第四设计信息格式、与获取的用于与第三设计信息验证的第四设计信息格式统一;所述将二者的格式统一的方法包括但不限于以下一种或多种:将两种格式中的一种格式转换成另一种格式,将两种格式均转化成第三种格式;所述第三种格式是指除获取的用于与第二设计信息验证的第四设计信息格式、获取的用于与第三设计信息验证的第四设计信息格式之外的格式;

289.确认获取的第二设计信息中的门级网表为后端网表、和/或非前端网表;

290.确认获取的第三设计信息中的门级网表为前端网表、和/或非后端网表;

291.所述确认获取的第二设计信息中的门级网表为后端网表、和/或非前端网表,和/或确认获取的第三设计信息中的门级网表为前端网表、和/或非后端网表的方法,包括但不限于以下一种或多种:关键词检索;将获取的第二设计信息中的门级网表、与获取的第三设计信息中的门级网表,进行相似度比对、和/或确定相似度小于等于第三十三预设门限;

292.确认获取的rtl代码为寄存器传输级描述、和/或非其他级别描述,所述其他级别描述包括但不限于门级描述;

293.通过所述获取的设计信息的文件后缀名,确认所述获取的设计信息的准确性。

294.本发明实施例中,所述信息处理模块202对所述设计信息进行验证时,所述设计信息之间的对应关系包括但不限于以下一种或多种:相同模块的对应关系、相同单元的对应关系、相同功能的对应关系、相同逻辑的对应关系、相同连接的对应关系。

295.本发明实施例中,所述信息处理模块202开展所述验证时,确认验证的设置或/和条件,所述确认验证的设置或/和条件的方法,包括但不限于以下一种或多种:

296.所述验证为lvs验证时,通过分析lvs验证针对的设计信息、或/和查看lvs验证针对的设计信息所对应的设计说明,确认lvs验证的设置或/和条件;所述lvs验证的设置或/和条件包括但不限于以下一种或多种:顶层设计、顶层单元、顶层逻辑、顶层模块;

297.所述验证为形式验证时,通过分析形式验证针对的设计信息、或/和查看形式验证针对的设计信息所对应的设计说明,确认形式验证的设置或/和条件;所述形式验证的设置或/和条件包括但不限于以下一种或多种:顶层设计、顶层单元、顶层逻辑、顶层模块、常量设置;

298.验证设置或/和条件中的顶层设计和/或顶层单元和/或顶层逻辑和/或顶层模块,与验证针对的设计信息相关,是所述芯片或芯片模块的所有或者部分的设计信息;所述验证设置的顶层设计和/或顶层单元和/或顶层逻辑和/或顶层模块,是所述芯片的部分的设计信息的应用场景,包括但不限于:对于模数混合芯片,形式验证设置或/和条件中的顶层设计和/或顶层单元和/或顶层逻辑和/或顶层模块,为模数混合芯片中的数字芯片模块。

299.本发明实施例中,所述信息处理模块202开展所述验证时,对验证的一项或多项结果或/和报告做综合分析,判断本次验证是否通过;所述验证为形式验证时,所述验证的结果或/和报告包括但不限于以下一种或多种:比较点匹配检查结果、验证结果、验证报告。

300.本发明实施例中,所述判定模块203基于比对结果和/或验证结果,对芯片或芯片模块的自主度和/或可控度进行判定,包括但不限于以下一种或多种:

301.根据芯片或芯片模块的特点,确定为判定所述芯片或芯片模块的自主度和/或可控度,所需要的比对种类和/或验证种类;

302.针对所述需要的比对种类和/或验证种类,根据所述各种类所代表的环节的难易程度和/或关键程度,分配所述各种需要的比对和/或验证各自对应的分值;

303.针对所述需要的比对和/或验证中的每一种,在实际开展并通过时,所述芯片或芯片模块获得该种比对和/或验证对应的分值;

304.针对所述需要的比对和/或验证中的每一种,在实际开展未通过或实际未开展时,所述芯片或芯片模块不获得该种比对和/或验证对应的分值;

305.综合实际开展的各种比对和/或验证的结果,在所述芯片或芯片模块获得的各种比对和/或验证对应的分值中,梳理出无效分值;

306.在所述芯片或芯片模块获得的各种比对和/或验证对应的分值中、去除无效分值、其余分值为有效分值,将有效分值求和、并将此求和结果作为所述芯片或芯片模块的最终得分;

307.根据所述芯片或芯片模块的最终得分,对芯片或芯片模块的自主度和/或可控度进行判定。

308.本发明实施例中,所述判定模块203综合实际开展的各种比对和/或验证的结果,在所述芯片或芯片模块获得的各种比对和/或验证对应的分值中,梳理出无效分值,包括但不限于以下一种或多种:

309.当所述芯片或芯片模块的实物信息与对应的第一设计信息进行比对未通过时,所述芯片或芯片模块针对所述需要的验证中的每一种在实际开展并通过时所获得的对应分

值均为无效分值;

310.当所述芯片或芯片模块的第一设计信息与对应的第二设计信息进行验证未通过时,所述芯片或芯片模块的第二设计信息与对应的第三设计信息的验证在实际开展并通过时所获得的对应分值为无效分值;

311.当所述芯片或芯片模块的第一设计信息与对应的第二设计信息进行验证未通过时,所述芯片或芯片模块的第二设计信息与对应的第四设计信息的验证在实际开展并通过时所获得的对应分值为无效分值;

312.当所述芯片或芯片模块的第一设计信息与对应的第二设计信息进行验证未通过时,所述芯片或芯片模块的第三设计信息与对应的第四设计信息的验证在实际开展并通过时所获得的对应分值为无效分值;

313.当所述芯片或芯片模块的第二设计信息与对应的第三设计信息进行验证未通过、且所述芯片或芯片模块的第二设计信息与对应的第四设计信息进行验证未通过时,所述芯片或芯片模块的第三设计信息与对应的第四设计信息的验证在实际开展并通过时所获得的对应分值为无效分值。

314.本发明实施例中,对于由一个或多个芯片模块组成的芯片,该芯片的自主度和/或可控度的判定包括但不限于以下一种或多种:

315.针对芯片中的各芯片模块,根据各芯片模块实现的难易程度和/或关键程度,分配相应的权值,芯片的得分为各芯片模块得分的加权求和值,基于所述加权求和值对芯片的自主度和/或可控度进行判定;

316.所述分配相应的权值,需要确保一个既定功能的芯片在不同方案下由一个或多个芯片模块组成时,在相同的自主度和/或可控度所对应的得分均相同;所述确保在相同的自主度和/或可控度所对应的得分均相同的实现方法包括但不限于以下一种或多种:权值分配归一化,在不同方案下、所述既定功能的芯片的各芯片模块的权值之和均相同,判定所述各芯片模块自主度和/或可控度最高时、所述各芯片模块的得分均相同,所述各芯片模块的满分均相同;

317.针对芯片中的各个芯片模块,在确定各个芯片模块的实物信息时,确保各芯片模块的实物信息不交叠和/或不重复、且各芯片模块的实物信息的总和为整个芯片的实物信息;

318.针对芯片中的各个芯片模块,在确定各个芯片模块的设计信息时,确保各芯片模块的设计信息不交叠和/或不重复、且各芯片模块的设计信息的总和为整个芯片的设计信息;

319.各自芯片模块的实物信息与设计信息保持对应的关系。

320.本发明实施例中,所述组成所述芯片的芯片模块中有相同型号的芯片模块时,将所述相同型号的芯片模块统一视作检测的一个整体芯片模块,统一计算一次分值、分配一个权值;所述判定模块203将所述相同型号的芯片模块统一视作检测的一个整体芯片模块的处理方法包括但不限于以下一种或多种:

321.将所述相同型号的芯片模块的实物信息的总和确定为所述检测的一个整体芯片模块的实物信息,将所述相同型号的芯片模块的设计信息的总和确定为所述检测的一个整体芯片模块的设计信息,并针对所述检测的一个整体芯片模块计算得分;

322.从所述相同型号的芯片模块中,随机或按照规则选取一个芯片模块,将其得分作为所述检测的一个整体芯片模块的得分;

323.针对所述相同型号的芯片模块,从中选取所有数量或者部分数量的芯片模块,分别计算选取的各个芯片模块的得分,将选取的各个芯片模块的得分的平均值作为所述检测的一个整体芯片模块的分值。

324.本发明实施例中,所述判定由一个或多个芯片模块组成的芯片的自主度和/或可控度的方法的适用范围,包括但不限于以下一种或多种:

325.由数字芯片模块和模拟芯片模块共同组成的模数混合芯片;

326.由多个裸片封装在一起形成的多芯片组件mcm;

327.射频前端模组。

328.本发明实施例还提供了一种芯片或芯片模块的检测装置,该装置包括:处理器和用于存储能够在处理器上运行的计算机程序的存储器,

329.其中,所述处理器用于运行所述计算机程序时,执行:

330.确定芯片或芯片模块的实物信息,和/或确定芯片或芯片模块的设计信息;

331.将所述实物信息与所述设计信息进行比对,和/或对所述设计信息进行验证;

332.基于比对结果和/或验证结果,对芯片或芯片模块的自主度和/或可控度进行判定。

333.本发明实施例中,所述处理器用于运行所述计算机程序时,还执行上述方法实施例所述的内容,此处不再详述。

334.需要说明的是:上述实施例提供的装置在进行芯片或芯片模块检测时,仅以上述各程序模块的划分进行举例说明,实际应用中,可以根据需要而将上述处理分配由不同的程序模块完成,即将设备的内部结构划分成不同的程序模块,以完成以上描述的全部或者部分处理。另外,上述实施例提供的装置与相应方法实施例属于同一构思,其具体实现过程详见方法实施例,这里不再赘述。

335.下面结合场景实施例对本发明进行描述。

336.本实施例提供了一种芯片或芯片模块的检测方法,通过追溯芯片或芯片模块的设计过程、对芯片或芯片模块各个环节的输出进行比对、验证的方式,检查芯片自主可控度。通过比对和/或验证、按照一定规则逻辑计算总得分,得到的分值越高,则说明此芯片设计过程自主化和/或可控程度越高,相应的自主度和/或可控度越高。该实施例为芯片或芯片模块的自主度和/或可控度的评估提供一个简便、客观的检测依据,提高了芯片或芯片模块的自主度和/或可控度评估的客观性、实操性和全面性。

337.场景实施例1:

338.针对某型号封装了一个裸片的、不含数字模块的芯片,提供一个实施例,可按照包括但不限于如下流程(流程图见图3,为了清楚显示,图中仅给出各操作的编号)判定此芯片的自主度和/或可控度:

339.一、确定芯片的实物信息和设计信息:

340.1.1,确定芯片与封装基板间的实物连接关系(实物信息的一种):

341.确定芯片(含内部的裸片)与封装基板间的实物连接关系,本实施例中确定其为描述连接关系的实物图-图a;

342.这里假定实物连接关系都集中在一层中、该层的实物图即代表了整个实物连接关系。若实物连接关系有多层,则可根据实际情况,记录所有层、部分层、或者其中一层的连接关系,得到描述连接关系的实物图。

343.1.2,确定封装基板的实物信息(实物信息的一种):

344.确定封装基板的实物信息,本实施例中确定其为封装基板实物,记录为封装基板实物图-图bi、图bj(i、j是选取的层号);

345.确定封装基板实物作为封装基板的实物信息,对于封装基板线路有多层的情况,随机(也可以是按照规则选取、设定等其他方式)选取i层、j层,通过显微镜与拍照相结合方式将其记录为图像,得到图bi、图bj;

346.这里假定封装基板线路有多层、并选取了部分层(这里是两层,也可以是三层、四层等其他数量的层数)作为实物信息并记录了图像。对于封装基板线路有多层的情况,也可以选取所有层作为实物信息并记录图像、或者选取其中一层作为实物信息并记录图像。对于封装基板线路仅一层的情况,则可以直接记录该层图像。

347.1.3,确定芯片的实物信息(实物信息的一种):

348.确定芯片的实物信息,本实施例中确定其为芯片实物版图,记录为芯片实物版图-图cp、图cq(p、q是选取的层号);

349.确定芯片实物版图作为芯片的实物信息,对于芯片版图有多层的情况,设定(也可以是随机、按照规则选取等其他方式选取)p层、q层作为实物信息,通过显微镜与拍照相结合方式将其记录为图像,得到图cp、图cq;

350.这里假定芯片版图有多层、并选取了部分层(这里是两层,也其可以是三层、四层等其他数量的层数)作为实物信息并记录了图像。对于芯片版图有多层的情况,也可以选取所有层作为实物信息并记录图像、或者选取其中一层作为实物信息并记录图像。对于芯片版图仅一层的情况,则可以直接记录该层图像。

351.1.4,确定芯片与封装基板间的设计连接关系(设计信息的一种):

352.确认芯片(含内部的裸片)与封装基板间的设计连接关系,本实施例中确定其为描述连接关系的设计图-图a;

353.描述连接关系的设计图中层号的选取,与描述连接关系的实物图相对应。

354.1.5,确定封装基板的设计信息(设计信息的一种):

355.确定封装基板的设计信息,本实施例中确定其为封装基板设计线路图-图bi、图bj(i、j是选取的层号);

356.封装基板设计线路图中层号的选取,与封装基板实物图相对应。

357.1.6,确定芯片的第一设计信息(设计信息的一种):

358.确定芯片的第一设计信息,本实施例中确定其为芯片的设计版图-图c(芯片的全部设计版图)、图cp、图cq(p、q是选取的层号);

359.图c是芯片的全部设计版图,即所有层整个区域的版图,便于后续与第二设计信息做验证,是用于验证的第一设计信息;图cp、图cq是芯片设计版图中的p层、q层的版图,即为图c的部分版图,层号的选取,与芯片实物版图相对应,便于后续与芯片实物版图比对,是用于比对的第一设计信息。

360.1.7,确定芯片的第二设计信息(设计信息的一种):

361.确定芯片的第二设计信息,本实施例中确定第二设计信息为芯片的原理图。

362.二、将实物信息与设计信息进行比对,对设计信息进行验证:

363.2.1,将芯片与封装基板间的实物连接关系,与对应的设计连接关系进行比对,检查二者是否一致(比对的一种):

364.比对图a中各管脚之间的连接关系与图a中各管脚之间的连接关系是否一致。

365.2.2,将封装基板的实物信息与对应的封装基板的设计信息进行比对,检查二者是否一致(比对的一种):

366.将图bi与图bi做比对,将图bj与图bj作比对,检查图中线路等的几何形状、几何形状特征等是否一致。

367.2.3,将芯片的实物信息与对应的芯片的第一设计信息进行比对,检查二者是否一致(比对的一种):

368.将图cp与图cp做比对,将图cq与图cq作比对,检查图中版图等的几何形状、几何形状特征等是否一致。

369.2.4,将芯片的第一设计信息与对应的第二设计信息进行验证(验证的一种),验证方法包括但不限于lvs检查或验证:

370.将芯片的设计版图(图c)与芯片的原理图进行lvs验证。

371.三、基于比对结果和验证结果,对芯片的自主度和/或可控度进行判定:

372.基于比对结果和验证结果,对芯片的自主度和/或可控度进行判定,包括但不限于以下一种或多种:

373.根据芯片的特点,确定为判定芯片的自主度和/或可控度,所需要的比对种类和/或验证种类:本实施例中,确定需要的比对种类为:芯片与封装基板间的实物连接关系、与对应的设计连接关系的比对(2.1条),封装基板的实物信息与对应的封装基板的设计信息的比对(2.2条),芯片的实物信息与对应的芯片的第一设计信息的比对(2.3条);确定需要的验证种类为:芯片的第一设计信息与对应的第二设计信息的验证(2.4条);

374.针对所述需要的比对种类和/或验证种类,根据所述各种类所代表的环节的难易程度和/或关键程度,分配所述各种需要的比对和/或验证各自对应的分值:本实施例中,针对如下比对、验证分配各自对应的分值:芯片与封装基板间的实物连接关系、与对应的设计连接关系的比对(2.1条),封装基板的实物信息与对应的封装基板的设计信息的比对(2.2条),芯片的实物信息与对应的芯片的第一设计信息的比对(2.3条),芯片的第一设计信息与对应的第二设计信息的验证(2.4条);

375.针对所述需要的比对和/或验证中的每一种,在实际开展并通过时,芯片获得该种比对和/或验证对应的分值;在实际开展未通过或实际未开展时,芯片不获得该种比对和/或验证对应的分值;

376.综合实际开展的各种比对和/或验证的结果,在所述芯片获得的各种比对和/或验证对应的分值中,梳理出无效分值;

377.在芯片获得的各种比对和验证对应的分值中、去除无效分值、其余分值为有效分值,将有效分值求和、并将此求和结果作为所述芯片的最终得分;

378.根据所述芯片的最终得分,对芯片的自主度和/或可控度进行判定。

379.场景实施例2:

380.针对某型号封装了一个裸片的数字芯片,提供一个实施例,可按照包括但不限于如下流程(流程图见图4,为了清楚显示,图中仅给出各操作的编号,另外,2.5中的和/或关系,图中无法一一展示,只展示其中一种情况-将1.7条中的第二设计信息与1.8条中的第三设计信息进行验证)判定此芯片的自主度和/或可控度:

381.一、确定芯片的实物信息和设计信息:

382.1.1,确定芯片与封装基板间的实物连接关系(实物信息的一种):

383.确定芯片(含内部的裸片)与封装基板间的实物连接关系,本实施例中确定其为描述连接关系的实物图-图a;

384.这里假定实物连接关系都集中在一层中、该层的实物图即代表了整个实物连接关系。若实物连接关系有多层,则可根据实际情况,记录所有层、部分层、或者其中一层的连接关系,得到描述连接关系的实物图。

385.1.2,确定封装基板的实物信息(实物信息的一种):

386.确定封装基板的实物信息,本实施例中确定其为封装基板实物,记录为封装基板实物图-图bi、图bj(i、j是选取的层号);

387.确定封装基板实物作为封装基板的实物信息,对于封装基板线路有多层的情况,随机(也可以是按照规则选取、设定等其他方式)选取i层、j层,通过显微镜与拍照相结合方式将其记录为图像,得到图bi、图bj;

388.这里假定封装基板线路有多层、并选取了部分层(这里是两层,也可以是三层、四层等其他数量的层数)作为实物信息并记录了图像。对于封装基板线路有多层的情况,也可以选取所有层作为实物信息并记录图像、或者选取其中一层作为实物信息并记录图像。对于封装基板线路仅一层的情况,则可以直接记录该层图像。

389.1.3,确定芯片的实物信息(实物信息的一种):

390.确定芯片的实物信息,本实施例中确定其为芯片实物版图,记录为芯片实物版图-图cp、图cq(p、q是选取的层号);

391.确定芯片实物版图作为芯片的实物信息,对于芯片版图有多层的情况,设定(也可以是随机、按照规则选取等其他方式选取)p层、q层作为实物信息,通过显微镜与拍照相结合方式将其记录为图像,得到图cp、图cq;

392.这里假定芯片版图有多层、并选取了部分层(这里是两层,也其可以是三层、四层等其他数量的层数)作为实物信息并记录了图像。对于芯片版图有多层的情况,也可以选取所有层作为实物信息并记录图像、或者选取其中一层作为实物信息并记录图像。对于芯片版图仅一层的情况,则可以直接记录该层图像。

393.1.4,确定芯片与封装基板间的设计连接关系(设计信息的一种):

394.确认芯片(含内部的裸片)与封装基板间的设计连接关系,本实施例中确定其为描述连接关系的设计图-图a;

395.描述连接关系的设计图中层号的选取,与描述连接关系的实物图相对应。

396.1.5,确定封装基板的设计信息(设计信息的一种):

397.确定封装基板的设计信息,本实施例中确定其为封装基板设计线路图-图bi、图bj(i、j是选取的层号);

398.封装基板设计线路图中层号的选取,与封装基板实物图相对应。

399.1.6,确定芯片的第一设计信息(设计信息的一种):

400.确定芯片的第一设计信息,本实施例中确定其为芯片的设计版图-图c(芯片的全部设计版图)、图cp、图cq(p、q是选取的层号);

401.图c是芯片的全部设计版图,即所有层整个区域的版图,便于后续与第二设计信息做验证,是用于验证的第一设计信息;图cp、图cq是芯片设计版图中的p层、q层的版图,即为图c的部分版图,层号的选取,与芯片实物版图相对应,便于后续与芯片实物版图比对,是用于比对的第一设计信息。

402.1.7,确定芯片的第二设计信息(设计信息的一种):

403.确定芯片的第二设计信息,本实施例中确定第二设计信息为芯片完成最终设计的门级网表(本实施例以此举例,其实也可以是第一设计信息对应的门级网表等其他内容)。

404.需要说明的是,上述确定第二设计信息为芯片完成最终设计的门级网表,是针对lvs验证软件可将门级网表格式作为输入的情况,如果lvs软件无法将门级网表格式作为输入,则可以做以下一种或多种处理:

405.将芯片完成最终设计的门级网表转化为lvs软件可以接受的输入格式,如cdl网表等晶体管级的网表格式(确认获取的设计信息的准确性),将芯片完成最终设计的门级网表、转换格式后的cdl网表等晶体管级的网表作为第二设计信息,前者用来与第三设计信息验证,后者用来与第一设计信息验证;

406.确定并获取芯片完成最终设计的门级网表、获取芯片cdl网表等晶体管级的网表,确认门级网表转换格式后与获取的cdl网表等晶体管级的网表内容相同或一致(确认获取的设计信息的准确性),将芯片完成最终设计的门级网表、芯片cdl网表等晶体管级的网表作为第二设计信息,前者用来与第三设计信息验证,后者用来与第一设计信息验证。

407.1.8,确定芯片的第三设计信息(设计信息的一种):

408.确定芯片的第三设计信息,本实施例中确定第三设计信息为芯片rtl代码综合形成的门级网表。

409.1.9,确定芯片的第四设计信息(设计信息的一种):

410.确定芯片的第四设计信息,本实施例中确定第四设计信息为芯片的rtl代码。

411.二、将实物信息与设计信息进行比对,对设计信息进行验证:

412.2.1,将芯片与封装基板间的实物连接关系,与对应的设计连接关系进行比对,检查二者是否一致(比对的一种):

413.比对图a中各管脚之间的连接关系与图a中各管脚之间的连接关系是否一致。

414.2.2,将封装基板的实物信息与对应的封装基板的设计信息进行比对,检查二者是否一致(比对的一种):

415.将图bi与图bi做比对,将图bj与图bj作比对,检查图中线路等的几何形状、几何形状特征等是否一致。

416.2.3,将芯片的实物信息与对应的芯片的第一设计信息进行比对,检查二者是否一致(比对的一种):

417.将图cp与图cp做比对,将图cq与图cq作比对,检查图中版图等的几何形状、几何形状特征等是否一致。

418.2.4,将芯片的第一设计信息与对应的第二设计信息进行验证(验证的一种),验证

方法包括但不限于lvs检查或验证:

419.将芯片的设计版图(图c)与芯片完成最终设计的门级网表进行lvs验证。

420.2.5,将芯片的第二设计信息与对应的第三设计信息进行验证,和/或将芯片的第二设计信息与对应的第四设计信息进行验证(验证的一种),验证方法包括但不限于形式验证:

421.本实施例中,将芯片完成最终设计的门级网表与芯片rtl代码综合形成的门级网表进行形式验证,和/或将芯片完成最终设计的门级网表与芯片的rtl代码进行形式验证。

422.2.6,将芯片的第三设计信息,与对应的第四设计信息进行验证(验证的一种),验证方法包括但不限于形式验证:

423.本实施例中,将芯片rtl代码综合形成的门级网表与芯片的rtl代码进行形式验证。

424.三、基于比对结果和验证结果,对芯片的自主度和/或可控度进行判定:

425.基于比对结果和验证结果,对芯片的自主度和/或可控度进行判定,包括但不限于以下一种或多种:

426.根据芯片的特点,确定为判定芯片的自主度和/或可控度,所需要的比对种类和/或验证种类:本实施例中,确定需要的比对种类为:芯片与封装基板间的实物连接关系、与对应的设计连接关系的比对(2.1条),封装基板的实物信息与对应的封装基板的设计信息的比对(2.2条),芯片的实物信息与对应的芯片的第一设计信息的比对(2.3条);确定需要的验证种类为:芯片的第一设计信息与对应的第二设计信息的验证(2.4条),芯片的第二设计信息与对应的第三设计信息的验证、和/或芯片的第二设计信息与对应的第四设计信息的验证(2.5条),芯片的第三设计信息与对应的第四设计信息的验证(2.6条);

427.针对所述需要的比对种类和/或验证种类,根据所述各种类所代表的环节的难易程度和/或关键程度,分配所述各种需要的比对和/或验证各自对应的分值:本实施例中,针对如下比对、验证分配各自对应的分值:芯片与封装基板间的实物连接关系、与对应的设计连接关系的比对(2.1条),封装基板的实物信息与对应的封装基板的设计信息的比对(2.2条),芯片的实物信息与对应的芯片的第一设计信息的比对(2.3条),芯片的第一设计信息与对应的第二设计信息的验证(2.4条),芯片的第二设计信息与对应的第三设计信息的验证、和/或芯片的第二设计信息与对应的第四设计信息的验证(2.5条),芯片的第三设计信息与对应的第四设计信息的验证(2.6条);

428.针对所述需要的比对和/或验证中的每一种,在实际开展并通过时,芯片获得该种比对和/或验证对应的分值;在实际开展未通过或实际未开展时,芯片不获得该种比对和/或验证对应的分值;

429.综合实际开展的各种比对和/或验证的结果,在所述芯片获得的各种比对和/或验证对应的分值中,梳理出无效分值;

430.在芯片获得的各种比对和验证对应的分值中、去除无效分值、其余分值为有效分值,将有效分值求和、并将此求和结果作为所述芯片的最终得分;

431.根据所述芯片的最终得分,对芯片的自主度和/或可控度进行判定。

432.场景实施例3:

433.针对某型号封装了一个裸片的模数混合芯片,提供一个实施例(两种方法),可按

照包括但不限于如下一种或多种方法的流程判定此芯片的自主度和/或可控度:

434.方法一:

435.将模数混合芯片看做由模拟芯片模块、数字芯片模块等芯片模块组成的芯片:

436.针对芯片中的模拟芯片模块、数字芯片模块,根据各芯片模块实现的难易程度和/或关键程度,分配相应的权值,芯片的得分为各芯片模块得分的加权求和值,基于所述加权求和值对芯片的自主度和/或可控度进行判定;

437.所述分配相应的权值,需要确保一个既定功能的芯片在不同方案下由一个或多个芯片模块组成时,在相同的自主度和/或可控度所对应的得分均相同;所述确保在相同的自主度和/或可控度所对应的得分均相同的实现方法包括但不限于以下一种或多种:权值分配归一化,在不同方案下、所述既定功能的芯片的各芯片模块的权值之和均相同,判定所述各芯片模块自主度和/或可控度最高时、所述各芯片模块的得分均相同,所述各芯片模块的满分均相同:如在本实施例中,将模拟芯片模块、数字芯片模块的权值之和设为1,将各芯片模块的满分均设为100;

438.针对模数混合芯片中的模拟芯片模块、数字芯片模块,根据模块与芯片间的关系,将模数混合芯片的实物信息、设计信息拆分给模拟芯片模块、数字芯片模块,使得模拟芯片模块、数字芯片模块的实物信息不交叠和/或不重复,且各芯片模块的实物信息的总和为整个芯片的实物信息,使得模拟芯片模块、数字芯片模块的设计信息不交叠和/或不重复,且各芯片模块的设计信息的总和为整个芯片的设计信息,各自芯片模块的实物信息与设计信息保持对应的关系;

439.参照场景实施例1(模拟芯片模块视作场景实施例1中的芯片)计算模拟芯片模块的得分,参照场景实施例2(数字芯片模块视作场景实施例2中的芯片)计算数字芯片模块的得分,芯片的得分为各芯片模块得分的加权求和值,基于所述加权求和值对芯片的自主度和/或可控度进行判定。其中,需要补充说明的是,场景实施例1、场景实施例2的连接关系(包括实物连接关系、设计连接关系)只有芯片(芯片模块)与封装基板间的实物连接关系,而本实施例参照场景实施例1(模拟芯片模块视作场景实施例1中的芯片)计算模拟芯片模块的得分、参照场景实施例2(数字芯片模块视作场景实施例2中的芯片)计算数字芯片模块的得分时,连接关系应当补充模拟芯片模块、数字芯片模块之间的连接关系、并将其合理的拆分给模拟芯片模块、数字芯片模块,再根据场景实施例1、场景实施例2中的方法进行操作。

440.方法二:

441.一、确定芯片的实物信息和设计信息:

442.1.1,确定芯片与封装基板间的实物连接关系(实物信息的一种):

443.确定芯片(含内部的裸片)与封装基板间的实物连接关系,本实施例中确定其为描述连接关系的实物图-图a;

444.这里假定实物连接关系都集中在一层中、该层的实物图即代表了整个实物连接关系。若实物连接关系有多层,则可根据实际情况,记录所有层、部分层、或者其中一层的连接关系,得到描述连接关系的实物图。

445.1.2,确定封装基板的实物信息(实物信息的一种):

446.确定封装基板的实物信息,本实施例中确定其为封装基板实物,记录为封装基板

实物图-图bi、图bj(i、j是选取的层号);

447.确定封装基板实物作为封装基板的实物信息,对于封装基板线路有多层的情况,随机(也可以是按照规则选取、设定等其他方式)选取i层、j层,通过显微镜与拍照相结合方式将其记录为图像,得到图bi、图bj;

448.这里假定封装基板线路有多层、并选取了部分层(这里是两层,也可以是三层、四层等其他数量的层数)作为实物信息并记录了图像。对于封装基板线路有多层的情况,也可以选取所有层作为实物信息并记录图像、或者选取其中一层作为实物信息并记录图像。对于封装基板线路仅一层的情况,则可以直接记录该层图像。

449.1.3,确定芯片的实物信息(实物信息的一种):

450.确定芯片的实物信息,本实施例中确定其为芯片实物版图,记录为芯片实物版图-图cp、图cq(p、q是选取的层号);

451.确定芯片实物版图作为芯片的实物信息,对于芯片版图有多层的情况,设定(也可以是随机、按照规则选取等其他方式选取)p层、q层作为实物信息,通过显微镜与拍照相结合方式将其记录为图像,得到图cp、图cq;

452.这里假定芯片版图有多层、并选取了部分层(这里是两层,也其可以是三层、四层等其他数量的层数)作为实物信息并记录了图像。对于芯片版图有多层的情况,也可以选取所有层作为实物信息并记录图像、或者选取其中一层作为实物信息并记录图像。对于芯片版图仅一层的情况,则可以直接记录该层图像。

453.1.4,确定芯片与封装基板间的设计连接关系(设计信息的一种):

454.确认芯片(含内部的裸片)与封装基板间的设计连接关系,本实施例中确定其为描述连接关系的设计图-图a;

455.描述连接关系的设计图中层号的选取,与描述连接关系的实物图相对应。

456.1.5,确定封装基板的设计信息(设计信息的一种):

457.确定封装基板的设计信息,本实施例中确定其为封装基板设计线路图-图bi、图bj(i、j是选取的层号);

458.封装基板设计线路图中层号的选取,与封装基板实物图相对应。

459.1.6,确定芯片的第一设计信息(设计信息的一种):

460.确定芯片的第一设计信息,本实施例中确定其为芯片的设计版图-图c(芯片的全部设计版图)、图cp、图cq(p、q是选取的层号);

461.图c是芯片的全部设计版图,即所有层整个区域的版图,便于后续与第二设计信息做验证,是用于验证的第一设计信息;图cp、图cq是芯片设计版图中的p层、q层的版图,即为图c的部分版图,层号的选取,与芯片实物版图相对应,便于后续与芯片实物版图比对,是用于比对的第一设计信息。

462.1.7,确定芯片的第二设计信息(设计信息的一种):

463.确定芯片的第二设计信息,本实施例中确定第二设计信息为芯片晶体管级的网表(如cdl网表)、芯片中数字芯片模块完成最终设计的门级网表(本实施例以此举例,其实也可以是第一设计信息对应的门级网表等其他内容)。

464.其中,芯片晶体管级的网表(如cdl网表)用于与芯片的第一设计信息进行验证,数字芯片模块完成最终设计的门级网表用于与第三设计信息进行验证、和/或与第四设计信

息进行验证;

465.验证前确认获取的设计信息的准确性,包括但不限于:针对数字芯片模块完成最终设计的门级网表,将格式转化为芯片晶体管级的网表的格式,并将其中的内容与芯片晶体管级的网表中关于数字芯片模块的内容进行相似性比对,二者应相同和/或保持一致和/或相似度大于等于某预设门限。

466.(或者:确定芯片的第二设计信息,确定第二设计信息为芯片晶体管级的网表、芯片中数字芯片模块完成最终设计的门级网表,芯片中模拟芯片模块的原理图;

467.此时,其中芯片晶体管级的网表、芯片中模拟芯片模块的原理图用于与芯片的第一设计信息进行验证(二者可以分别与第一设计信息去做验证,综合二者结果作为第一设计信息与第二设计信息进行验证的结果;其中模拟芯片模块的原理图进行验证时,版图侧输入可将图c作为lvs输入、设置模拟芯片模块作为顶层设计和/或顶层单元和/或顶层逻辑和/或顶层模块,或者,在第一设计信息中增加模拟芯片模块版图作为第一设计信息,作为版图侧输入,此时第一设计信息中应注意补充此设计信息准确性的确认),数字芯片模块完成最终设计的门级网表用于与第三设计信息进行验证、和/或与第四设计信息进行验证;

468.验证前确认获取的设计信息的准确性,包括但不限于:针对数字芯片模块完成最终设计的门级网表,将格式转化为芯片晶体管级的网表的格式,并将其中的内容与芯片晶体管级的网表中关于数字芯片模块的内容进行相似性比对,二者应相同和/或保持一致和/或相似度大于等于某预设门限;针对模拟芯片模块的原理图,将格式转化为芯片晶体管级的网表的格式,并将其中的内容与芯片晶体管级的网表中关于模拟芯片模块的内容进行相似性比对,二者应相同和/或保持一致和/或相似度大于等于某预设门限;

469.其他模块亦可以参照模拟芯片模块做独立的验证,再通过设计信息准确性确认与其他设计信息建立联系,这里不再赘述。)

470.1.8,确定芯片的第三设计信息(设计信息的一种):

471.确定芯片的第三设计信息,本实施例中确定第三设计信息为芯片中数字芯片模块rtl代码综合形成的门级网表。

472.1.9,确定芯片的第四设计信息(设计信息的一种):

473.确定芯片的第四设计信息,本实施例中确定第四设计信息为芯片中数字芯片模块的rtl代码。

474.二、将实物信息与设计信息进行比对,对设计信息进行验证:

475.2.1,将芯片与封装基板间的实物连接关系,与对应的设计连接关系进行比对,检查二者是否一致(比对的一种):

476.比对图a中各管脚之间的连接关系与图a中各管脚之间的连接关系是否一致。

477.2.2,将封装基板的实物信息与对应的封装基板的设计信息进行比对,检查二者是否一致(比对的一种):

478.将图bi与图bi做比对,将图bj与图bj作比对,检查图中线路等的几何形状、几何形状特征等是否一致。

479.2.3,将芯片的实物信息与对应的芯片的第一设计信息进行比对,检查二者是否一致(比对的一种):

480.将图cp与图cp做比对,将图cq与图cq作比对,检查图中版图等的几何形状、几何形

状特征等是否一致。

481.2.4,将芯片的第一设计信息与对应的第二设计信息进行验证(验证的一种),验证方法包括但不限于lvs检查或验证:

482.将芯片的设计版图(图c)与芯片晶体管级的网表(如cdl网表)进行lvs验证。

483.2.5,将芯片的第二设计信息与对应的第三设计信息进行验证,和/或将芯片的第二设计信息与对应的第四设计信息进行验证(验证的一种),验证方法包括但不限于形式验证:

484.本实施例中,将芯片中数字芯片模块完成最终设计的门级网表与芯片中数字芯片模块rtl代码综合形成的门级网表进行形式验证,和/或将芯片中数字芯片模块完成最终设计的门级网表与芯片中数字芯片模块的rtl代码进行形式验证。

485.2.6,将芯片的第三设计信息,与对应的第四设计信息进行验证(验证的一种),验证方法包括但不限于形式验证:

486.本实施例中,将芯片中数字芯片模块rtl代码综合形成的门级网表与芯片中数字芯片模块的rtl代码进行形式验证。

487.三、基于比对结果和验证结果,对芯片的自主度和/或可控度进行判定:

488.基于比对结果和验证结果,对芯片的自主度和/或可控度进行判定,包括但不限于以下一种或多种:

489.根据芯片的特点,确定为判定芯片的自主度和/或可控度,所需要的比对种类和/或验证种类:本实施例中,确定需要的比对种类为:芯片与封装基板间的实物连接关系、与对应的设计连接关系的比对(2.1条),封装基板的实物信息与对应的封装基板的设计信息的比对(2.2条),芯片的实物信息与对应的芯片的第一设计信息的比对(2.3条);确定需要的验证种类为:芯片的第一设计信息与对应的第二设计信息的验证(2.4条),芯片的第二设计信息与对应的第三设计信息的验证、和/或芯片的第二设计信息与对应的第四设计信息的验证(2.5条),芯片的第三设计信息与对应的第四设计信息的验证(2.6条);

490.针对所述需要的比对种类和/或验证种类,根据所述各种类所代表的环节的难易程度和/或关键程度,分配所述各种需要的比对和/或验证各自对应的分值:本实施例中,针对如下比对、验证分配各自对应的分值:芯片与封装基板间的实物连接关系、与对应的设计连接关系的比对(2.1条),封装基板的实物信息与对应的封装基板的设计信息的比对(2.2条),芯片的实物信息与对应的芯片的第一设计信息的比对(2.3条),芯片的第一设计信息与对应的第二设计信息的验证(2.4条),芯片的第二设计信息与对应的第三设计信息的验证、和/或芯片的第二设计信息与对应的第四设计信息的验证(2.5条),芯片的第三设计信息与对应的第四设计信息的验证(2.6条);

491.针对所述需要的比对和/或验证中的每一种,在实际开展并通过时,芯片获得该种比对和/或验证对应的分值;在实际开展未通过或实际未开展时,芯片不获得该种比对和/或验证对应的分值;

492.综合实际开展的各种比对和/或验证的结果,在所述芯片获得的各种比对和/或验证对应的分值中,梳理出无效分值;

493.在芯片获得的各种比对和验证对应的分值中、去除无效分值、其余分值为有效分值,将有效分值求和、并将此求和结果作为所述芯片的最终得分;

494.根据所述芯片的最终得分,对芯片的自主度和/或可控度进行判定。

495.场景实施例4:

496.针对某型号封装了n个裸片(分别称作裸片1、裸片2

…

裸片n)的芯片,将每个裸片视作一个芯片模块,则该型号芯片可视作由n个芯片模块(分别称作芯片模块1、芯片模块2

…

芯片模块n)组成。

497.为判定该型号芯片的自主度和/或可控度,从一批或者多批该型号芯片产品中,随机或按照规则选取一个或多个该型号的芯片(如果一个芯片可以获取其所有实物信息,则选取一个芯片,如果获取实物信息时有破坏性操作等情况、致使一个芯片不足以获取所有实物信息,则选取多个芯片),按照如下流程分别判定此芯片中芯片模块1、芯片模块2

…

芯片模块n的自主度和/或可控度,在此基础上判定芯片的自主度和/或可控度:

498.对于由一个或多个芯片模块组成的芯片,该芯片的自主度和/或可控度的判定包括但不限于以下一种或多种(在本实施例中,是对于由芯片模块1、芯片模块2

…

芯片模块n组成的芯片,该芯片的自主度和/或可控度的判定包括但不限于以下一种或多种):

499.针对芯片中的各芯片模块(本实施例中,即芯片模块1、芯片模块2

…

芯片模块n),根据各芯片模块实现的难易程度和/或关键程度,分配相应的权值,芯片的得分为各芯片模块得分的加权求和值,基于所述加权求和值对芯片的自主度和/或可控度进行判定;

500.其中,各芯片模块得分的计算,可以根据芯片模块的类别参照场景实施例1(芯片模块视作场景实施例1中的芯片)和/或场景实施例2(芯片模块视作场景实施例2中的芯片)和/或场景实施例3(芯片模块视作场景实施例3中的芯片)和/或本发明开展。

501.其中,需要补充说明的是,场景实施例1、场景实施例2、场景实施例3的连接关系(包括实物连接关系、设计连接关系)只有芯片(等同于本实施例中的芯片模块)与封装基板间的实物连接关系,而本实施例参照场景实施例1和/或场景实施例2和/或场景实施例3计算芯片模块的得分时,连接关系需要视情补充芯片模块之间的连接关系(即芯片模块与其他芯片模块间的连接关系)、并将其合理的拆分给各芯片模块,再根据场景实施例1和/或场景实施例2和/或场景实施例3中的方法进行操作;所述连接关系需要视情补充芯片模块之间的连接关系的情况,即指一个或多个芯片模块与其他一个或多个芯片模块之间有连接时。

502.分配相应的权值时,需要确保一个既定功能的芯片在不同方案下由一个或多个芯片模块组成时,在相同的自主度和/或可控度所对应的得分均相同;所述确保在相同的自主度和/或可控度所对应的得分均相同的实现方法包括但不限于以下一种或多种:权值分配归一化(如,本实施例中,芯片模块1、芯片模块2

…

芯片模块n的权值之和为1),在不同方案下、所述既定功能的芯片的各芯片模块的权值之和均相同,判定所述各芯片模块自主度和/或可控度最高时、所述各芯片模块的得分均相同,所述各芯片模块的满分均相同(如,本实施例中,芯片模块1、芯片模块2

…

芯片模块n的满分均为100);

503.针对芯片中的各个芯片模块,在确定各个芯片模块的实物信息时,确保各芯片模块的实物信息不交叠和/或不重复、且各芯片模块的实物信息的总和为整个芯片的实物信息;针对芯片中的各个芯片模块,在确定各个芯片模块的设计信息时,确保各芯片模块的设计信息不交叠和/或不重复、且各芯片模块的设计信息的总和为整个芯片的设计信息;各自芯片模块的实物信息与设计信息保持对应的关系(如本实施例中,芯片模块1、芯片模块2

…

芯片模块n放置在同一封装基板上时,针对封装基板的实物信息与对应的设计信息,根据其与芯片模块1、芯片模块2

…

芯片模块n的关系进行划分,确保芯片模块1、芯片模块2

…

芯片模块n所分配到的封装基板的实物信息不交叠、且其总和恰为封装基板的所有实物信息,确保芯片模块1、芯片模块2

…

芯片模块n所分配到的封装基板的设计信息不交叠、且其总和恰为封装基板的所有设计信息);

504.如果芯片模块1、芯片模块2

…

芯片模块n中,有些芯片模块为相同型号(如,芯片模块1、芯片模块2是相同型号),则可将相同型号的芯片模块统一视作检测的一个整体芯片模块,统一计算一次分值、分配一个权值(即分配权值时,不再给芯片模块1、芯片模块2分别分配权值,而是将其视作一个整体,分配一个权值,该权值与除芯片模块1、芯片模块2之外的芯片模块的权值,在分配时继续满足归一化的要求);所述将所述相同型号的芯片模块统一视作检测的一个整体芯片模块的处理方法包括但不限于以下一种或多种:将所述相同型号的芯片模块的实物信息的总和确定为所述检测的一个整体芯片模块的实物信息(如,将芯片模块1、芯片模块2的实物信息的总和确定为一个整体芯片模块的实物信息),将所述相同型号的芯片模块的设计信息的总和确定为所述检测的一个整体芯片模块的设计信息(如,将芯片模块1、芯片模块2的设计信息的总和确定为一个整体芯片模块的设计信息),并针对所述检测的一个整体芯片模块计算得分;从所述相同型号的芯片模块中,随机或按照规则选取一个芯片模块,将其得分作为所述检测的一个整体芯片模块的得分(如,将芯片模块1的得分作为一个整体芯片模块的得分);针对所述相同型号的芯片模块,从中选取所有数量或者部分数量的芯片模块,分别计算选取的各个芯片模块的得分,将选取的各个芯片模块的得分的平均值作为所述检测的一个整体芯片模块的分值。

505.场景实施例5:

506.针对所述综合实际开展的各种比对和/或验证的结果,在所述芯片或芯片模块获得的各种比对和/或验证对应的分值中,梳理出无效分值,做如下举例说明:

507.若根据芯片或芯片模块的特点,确定为判定所述芯片或芯片模块的自主度和/或可控度,所需要的比对种类和/或验证种类如下:芯片或芯片模块与封装基板间的实物连接关系、和/或芯片或芯片模块与其他芯片或芯片模块间的实物连接关系,与对应的设计连接关系的比对(比对1),封装基板的实物信息与对应的封装基板的设计信息的比对(比对2),芯片或芯片模块的实物信息与对应的芯片或芯片模块的第一设计信息的比对(比对3),芯片或芯片模块的第一设计信息与对应的第二设计信息的验证(验证1),芯片或芯片模块的第二设计信息与对应的第三设计信息的验证、和/或芯片或芯片模块的第二设计信息与对应的第四设计信息的验证(验证2),芯片或芯片模块的第三设计信息与对应的第四设计信息的验证(验证3);

508.其中梳理出无效分值,包括但不限于以下一种或多种:

509.当比对3未通过时,芯片模块针对需要的验证中的每一种在实际开展并通过时所获得的对应分值均为无效分值,在本实施例中,此时验证1、验证2、验证3在实际开展并通过时所获得的对应分值均为无效分值;

510.当验证1未通过时,验证2中芯片或芯片模块的第二设计信息与对应的第三设计信息的验证在实际开展并通过时所获得的对应分值为无效分值;

511.当验证1未通过时,验证2中芯片或芯片模块的第二设计信息与对应的第四设计信

息的验证在实际开展并通过时所获得的对应分值为无效分值;

512.当验证1未通过时,验证3在实际开展并通过时所获得的对应分值为无效分值;

513.当验证2中芯片或芯片模块的第二设计信息与对应的第三设计信息进行验证未通过、且验证2中芯片或芯片模块的第二设计信息与对应的第四设计信息进行验证未通过时,验证3在实际开展并通过时所获得的对应分值为无效分值。

514.场景实施例6:

515.针对所述实物信息的获取方法,做如下举例说明(有些实物信息的获取方法已在说明书中做了解释,这里不再赘述):

516.关于芯片或芯片模块与封装基板间的实物连接关系、和/或芯片或芯片模块与其他芯片或芯片模块间的实物连接关系的获取的一些举例说明:

517.对于采用引线键合方式将芯片或芯片模块与封装基板连接在一起、和/或将芯片或芯片模块与其他芯片或芯片模块连接在一起、引线建立起的连接关系不被遮挡的情况,可以通过显微镜(和/或显微成像仪器和/或ct和/或x射线和/或x光和/或放射线和/或超声和/或无损检测等形式)与拍照相结合的方式获取实物连接关系;对于芯片中使用倒装焊的连接方式将芯片或芯片模块与封装基板连接在一起、和/或将芯片或芯片模块与其他芯片或芯片模块连接在一起、倒装焊建立起的连接关系被芯片和/或芯片模块和/或封装基板等所遮挡的情况,可以借助ct(和/或x射线和/或x光和/或放射线和/或超声和/或无损检测等形式)获取实物连接关系,或者通过平磨(和/或去层和/或磨削和/或研磨和/或打磨和/或抛光和/或腐蚀和/或刻蚀和/或剖片和/或解剖和/或染色等形式)露出倒装焊界面(此界面表征了实物连接关系)、再通过显微镜等形式与拍照相结合方式获取实物连接关系,其中平磨等可以从芯片和/或芯片模块侧开始或者从封装基板侧开始,如此则芯片和/或芯片模块和/或封装基板会被破坏,若还需要从中获取其他实物信息,需要选取另外一个或多个芯片和/或芯片模块获取(这也是取得或选取一个或多个待测芯片或芯片模块并获取实物信息的情况之一);

518.关于将芯片或芯片模块与封装基板分离、和/或将芯片或芯片模块与其他芯片或芯片模块分离的一些举例说明:如果多个芯片模块在同一封装基板上、其他芯片模块影响了该芯片模块实物信息的获取,则可以先将芯片模块与封装基板分离,包括但不限于以下一种或多种:断开或移除或去除连接线、腐蚀、刻蚀、加热、去层、平磨、磨削、研磨、打磨、剖片、解剖、取下芯片;

519.关于获取一层或多层的实物信息的一些举例说明:对于实物连接关系和/或封装基板的实物信息和/或芯片或芯片模块的实物信息,若选取的层号对应了表面层、且信息未被遮挡,则可以直接获取实物信息,和/或通过显微镜等形式与拍照相结合方式将其记录为图像;若选取的层号对应了中间层、或信息被遮挡,则可以通过去层(和/或平磨和/或磨削和/或研磨和/或打磨和/或抛光和/或腐蚀和/或刻蚀和/或剖片和/或解剖和/或染色和/或断开或移除或去除连接线等形式)露出该层,再直接获取实物信息,和/或通过显微镜等形式与拍照相结合方式将其记录为图像。

520.场景实施例7:

521.针对所述比对的方法包括但不限于以下一种或多种:通过检测装置自动比对,通过人工比对,做如下举例说明:

522.当比对方法为通过检测装置自动比对时,需要判断所述实物信息的格式是否为检测装置所能识别和/或使用的格式;当所述实物信息的格式不是检测装置所能识别和/或使用的格式时,需要将所述实物信息的格式调整为检测装置所能识别和/或使用的格式;所述将所述实物信息的格式调整为检测装置所能识别和/或使用的格式的方法,包括但不限于以下一种或多种:将实物信息记录为实物图像、将实物连接关系转化为描述实物连接关系的表格;

523.当比对方法为通过检测装置自动比对时,需要判断所述设计信息的格式是否为检测装置所能识别和/或使用的格式;当所述设计信息的格式不是检测装置所能识别和/或使用的格式时,需要将所述设计信息的格式调整为检测装置所能识别和/或使用的格式;所述将所述设计信息的格式调整为检测装置所能识别和/或使用的格式的方法,包括但不限于以下一种或多种:将设计信息转化为设计图像、将设计连接关系转化为描述设计连接关系的表格;所述设计图像包括但不限于将设计信息保存为或/和转化为或/和记录为图像格式的图像;

524.针对将所述设计信息的格式调整为检测装置所能识别和/或使用的格式的方法,举以下几个例子:当实物连接关系和/或封装基板的实物信息和/或芯片或芯片模块的实物信息被记录为实物图像,设计连接关系和/或封装基板的设计信息和/或芯片或芯片模块的第一设计信息的格式为矢量图格式等检测装置无法用于图像比对的格式时,将设计信息的格式由矢量图等格式转化成图像格式(将设计信息转化为设计图像),由检测装置对实物图像、设计图像两幅图像进行比对;对于实物连接关系、设计连接关系,还有一种方式,将各自的连接关系转化为表格,再由检测装置对两个表格(描述实物连接关系的表格、描述设计连接关系的表格)比对。

525.所述判断所述实物信息和/或所述设计信息的格式是否为检测装置所能识别和/或使用的格式的方法,包括但不限于以下一种或多种:通过检测装置自动判断,通过人工判断;

526.所述将所述实物信息和/或所述设计信息的格式调整为检测装置所能识别和/或使用的格式的方法,包括但不限于以下一种或多种:通过检测装置自动调整,通过人工调整。

527.场景实施例8:

528.针对将芯片或芯片模块的实物图像、与设计图像进行比对(也可以是图像板块的比对,也可以是其他实物信息与设计信息的比对,本实施例中不再赘述),所述比对的比对方式采用整体比对与采样比对相结合的方式(也可以是其实方式,本实施例中不再赘述),做如下举例说明:

529.整体比对时,本实施例进行整体粗略比对,重点比对芯片或芯片模块的面积、轮廓、模块结构等在两幅图像中是否一致;

530.采样比对时,针对图像的比对,计算和/或设定可用于比对的面积;根据可用于比对的面积、从图像中选取若干采样块,若干采样块的面积之和不得超过可用于比对的面积;选取采样块时,两幅图像中的采样块保持对应关系;采样块的选取方法包括但不限于以下一种或多种:随机采样,按照规则采样,正比于图形密度和/或复杂度分配采样块数量,正比于图形密度和/或复杂度分配采样块的面积,设定;对两幅图像中对应关系的采样块进行比

对;综合各采样块的比对结果分析本采样比对的结果;

531.其中,计算可用于比对的面积的一种方法为:根据完成单位面积比对所需要的时间,以及本次比对预期完成的时间,计算可用于比对的面积;可用于比对的面积=单位面积*本次比对预期完成的时间/完成单位面积比对所需要的时间;

532.综合整体比对和采样比对的结果分析本次图像比对的结果;

533.在整体粗略比对时,和/或选取采样块后,可以针对要比对的实物图像和/或设计图像,调整实物图像和/或设计图像的分辨率和/或像素数量,在调整结果的基础上针对实物图像与设计图像进行比对;

534.在整体粗略比对,和/或采样比对时,针对包括但不限于以下一种或多种情况,调整比对的实现算法:不同的比对目的、不同的比对内容、不同的对比方法、不同的对比方式、比对中不同的工作阶段。

535.场景实施例9:

536.针对将实物信息或实物图像、与设计信息或设计图像进行比对(和/或将实物信息板块或实物图像板块、与设计信息板块或设计图像板块,本实施例不再赘述)进行比对,当所述比对方法为通过检测装置自动比对时,针对本次计划比对的颗粒度,根据实物图像和/或设计图像的分辨率、和/或本次计划比对的颗粒度在实物图像和/或设计图像中包含的像素数量,以及检测装置的比对能力,调整实物图像和/或设计图像的分辨率和/或像素数量,在所述调整结果的基础上针对实物图像与设计图像进行比对,做如下举例说明:

537.所述检测装置的比对能力包括但不限于:检测装置在所述颗粒度下为完成比对、针对实物图像和/或设计图像各自需要的最小分辨率、和/或所述颗粒度需包含的最小像素数量;

538.所述调整的方法包括但不限于:针对本次计划比对的颗粒度,确保比对准确的前提下,减小实物图像和/或设计图像的分辨率和/或像素数量,使实物图像和/或设计图像的分辨率减小、和/或实物图像和/或设计图像中所述颗粒度所包含的像素数量减小,且大于等于检测装置的比对能力;

539.如,在整体粗略比对时,确定本次计划粗略比对的颗粒度为0.1mm(举例),要比对的实物图像、设计图像的分辨率在本实施例中使用单位英寸中所包含的像素点数为单位表述,均为2000万/英寸(举例),检测装置的比对能力为:在0.1mm颗粒度时,针对实物图像、设计图像各自需要的最小分辨率为1万/英寸(举例),那么一种调整方法为:减小实物图像、设计图像的分辨率,使实物图像、设计图像的分辨率减小(即小于2000万/英寸),且大于等于检测装置的比对能力(即大于等于1万/英寸)。针对调整后的实物图像与设计图像,进行比对。

540.场景实施例10:

541.针对所述确认获取的设计信息的准确性的方法,做如下举例说明:

542.确认获取的设计信息的准确性的目的之一是确认获取的设计信息内容和格式等满足需求、确认获取的设计信息确为该芯片的设计信息、设计信息之间保持联系等,取其中一部分方法做举例说明:

543.对于获取的用于与第一设计信息验证的第二设计信息、获取的用于与第三设计信息验证的第二设计信息、与获取的用于与第四设计信息验证的第二设计信息中,对于三者

中任意和/或设定的一种或多种两两组合的组合内部之间、和/或三者之间,确认交叠部分和/或重复部分设计信息相同、和/或保持一致;所述确认所述交叠部分和/或重复部分的设计信息相同、和/或保持一致的方法,包括但不限于以下一种或多种:将设计信息格式统一;针对交叠部分和/或重复部分进行图像比对;针对交叠部分和/或重复部分进行图形比对;针对交叠部分和/或重复部分进行相似性比对;确定相似度大于等于第三十预设门限;确定获取的用于与第一设计信息验证的第二设计信息、获取的用于与第三设计信息验证的第二设计信息、与获取的用于与第四设计信息验证的第二设计信息中,其中一种或多种信息的所有或者部分信息、是从另一种或多种信息中提取所有或者部分信息获得,和/或其中一种或多种信息的所有或者部分信息是由另一种或多种信息格式转换后从中提取所有或者部分信息获得;所述确认所述交叠部分和/或重复部分的设计信息相同、和/或保持一致的方法的应用场景,包括但不限于:对于模数混合芯片,确认其中的数字芯片模块的门级网表在格式转换为晶体管级的网表后,其内容与芯片晶体管级的网表中的数字芯片模块部分,相同或者保持一致;

544.举例:如果验证时,用到了第一设计信息与第二设计信息的验证、第二设计信息与第三设计信息的验证、第二设计信息与第四设计信息的验证,那么用于与第一设计信息验证的第二设计信息(本实施例简称信息1)、用于与第三设计信息验证的第二设计信息(本实施例简称信息2)、与用于与第四设计信息验证的第二设计信息(本实施例简称信息3)中,任意两者之间为相同的或者不同的设计信息,即信息1、信息2之间为相同的或者不同的设计信息,信息1、信息3之间为相同的或者不同的设计信息,信息2、信息3之间为相同的或者不同的设计信息;用于与第一设计信息验证的第二设计信息格式、用于与第三设计信息验证的第二设计信息格式、与用于与第四设计信息验证的第二设计信息格式中,任意两者之间为相同的或者不同的格式,即信息1、信息2之间为相同的或者不同的格式,信息1、信息3之间为相同的或者不同的格式,信息2、信息3之间为相同的或者不同的格式。

545.确认获取的设计信息准确性,对于获取的信息1、信息2、信息3,对于三者中任意和/或设定的一种或多种两两组合的组合内部之间、和/或三者之间,确认交叠部分和/或重复部分设计信息相同、和/或保持一致(若获取的信息1、信息2、信息3确为该芯片的设计信息,那么信息1、信息2、信息3都是所述第二设计信息的所有或者部分信息,应当满足此要求);即为以下一种或多种:获取的信息1、信息2中的交叠部分和/或重复部分设计信息相同、和/或保持一致;获取的信息1、信息3中的交叠部分和/或重复部分设计信息相同、和/或保持一致;获取的信息2、信息3中的交叠部分和/或重复部分设计信息相同、和/或保持一致;获取的信息1、信息2、信息3中的交叠部分和/或重复部分设计信息相同、和/或保持一致;对于交叠部分的说明:如获取的信息1由a、b三部分信息组成,获取的信息2由b信息组成,那么交叠部分和/或重复部分此时即为b信息,确认获取的信息1、信息2中的交叠部分和/或重复部分设计信息相同、和/或保持一致,即:确认获取的信息1中的b信息,与获取的信息2中的b信息相同、和/或保持一致(即,由于获取的信息1、获取的信息2都属于第二设计信息,那么其中的交叠部分和/或重复部分b信息,应当相同、和/或保持一致)。

546.确认所述交叠部分和/或重复部分的设计信息相同、和/或保持一致的方法,包括但不限于以下一种或多种:将设计信息格式统一;针对交叠部分和/或重复部分进行图像比对;针对交叠部分和/或重复部分进行图形比对;针对交叠部分和/或重复部分进行相似性

比对;确定相似度大于等于第三十预设门限;确定获取的用于与第一设计信息验证的第二设计信息、获取的用于与第三设计信息验证的第二设计信息、与获取的用于与第四设计信息验证的第二设计信息中,其中一种或多种信息的所有或者部分信息、是从另一种或多种信息中提取所有或者部分信息获得,和/或其中一种或多种信息的所有或者部分信息是由另一种或多种信息格式转换后从中提取所有或者部分信息获得;以确认获取的信息1、信息2中的交叠部分和/或重复部分设计信息相同、和/或保持一致举例,包括但不限于以下一种或多种:如果获取的信息1、获取的信息2的格式不同(如一个是晶体管级的网表、一个是门级网表),将设计信息格式统一(如都统一成晶体管级的网表);针对交叠部分和/或重复部分进行图像比对;针对交叠部分和/或重复部分进行图形比对;针对交叠部分和/或重复部分进行相似性比对(如将获取的信息1中的b信息,与获取的信息2中的b信息进行相似性比对);确定相似度大于等于某预设门限(本实施例简称门限1,比如门限1设为95%、100%等数值);确认获取的信息1中的信息b,是由获取的信息2格式转换(如由门级网表转化为晶体管级的网表)后从中提取所有信息-即信息b获得。

547.同样对于确认获取的信息1、信息3中的交叠部分和/或重复部分设计信息相同、和/或保持一致,获取的信息2、信息3中的交叠部分和/或重复部分设计信息相同、和/或保持一致,获取的信息1、信息2、信息3中的交叠部分和/或重复部分设计信息相同、和/或保持一致的方法,与上述确认获取的信息1、信息2中的交叠部分和/或重复部分设计信息相同、和/或保持一致的举例方法类似,且其相似度设定的预设门限,假定分别命名为门限2、门限3、门限4,那么门限1、门限2、门限3、门限4之间,任意两者间均可以相同或不同。

548.需要说明的是:上述场景实施例仅是本发明的保护范围的一部分,并非用于限定本发明的保护范围,其他更多实施例不再赘述。

549.可见,本实施例为芯片或芯片模块的评估提供了一个简便、客观的检测依据,提高了芯片或芯片模块的自主度和/或可控度评估的客观性、实操性和全面性,并可为芯片或芯片模块的自主度和/或可控度评估取证材料的真实性做佐证依据,可作为芯片或芯片模块的自主度和/或可控度评估的有力支撑。

550.以上所述,仅为本发明的较佳实施例而已,并非用于限定本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。