1.本发明属于新型半导体信息器件中场效应晶体管领域,具体涉及一种利用双层侧墙技术抑制纳米尺度负电容鳍式场效应晶体管中由于金属栅极功函数的随机变异引起的器件性能参数波动的方法。

背景技术:

2.电子信息产业和集成电路技术的快速发展是基于晶体管器件尺寸的持续缩小、结构的不断演变、性能的不断提高、功耗的降低以及成品率和可靠性的提升。然而,随着cmos技术的不断发展,芯片上集成的晶体管数量已经突破百亿个,导致芯片的功耗和发热急剧增加,严重制约了cmos技术的进一步发展。

3.为此,一些新型超低功耗纳米cmos器件被不断开发出来。其中负电容鳍式场效应晶体管(nc-finfet)由于较好的工艺兼容性、结构先进性和与传统mosfet器件类似的工作机理而脱颖而出,见图1。该器件普遍采用高介电常数作为栅氧化物并以金属材料作为器件栅极。金属相比多晶硅材料融点低,其沉积工艺较为简单。而且金属晶粒形成的金属-氧化层-半导体(mis)结构具有更轻微的界面缺陷,使得栅极堆叠层可以更好地相互兼容。然而,栅极金属会因为晶粒取向分布不同引起功函数取值不同,导致器件的阈值电压等参数产生随机波动现象,进而影响器件性能,导致电路芯片性能退化和可靠性降低。研究表明,功函数波动的影响与晶粒面积和栅极面积的比值密切相关,由于晶粒的尺寸相对固定,因此越小的器件受影响越大,而增加栅极长度和栅极面积则有利于减少其对器件的影响。

4.目前,实际工艺中采用绝缘层的侧墙结构将源/漏极与栅极隔开,目的是避免它们彼此之间的连通。以侧墙作为硬掩模可实现小尺度图案的转移,用来形成鳍式结构和制造鳍式场效应晶体管。为了增大器件的开态电流,可使用高介电(high-k)常数侧墙来代替低介电常数(low-k)的侧墙。然而,high-k侧墙会增加栅与源/漏外延之间的电容。因此,源/漏侧墙结构也可由单层结构变为双层结构,其中high-k侧墙能提高栅极对沟道电荷的耦合,增加开态电流(i

on

);low-k侧墙保证了较小的寄生电容,提高器件的开关速度。

技术实现要素:

5.针对目前负电容鳍式场效应晶体管(nc-finfet)中因金属栅极功函数的随机变异而导致器件和电路性能波动的问题,本发明提供了一种抑制负电容鳍式晶体管功函数变异影响的方法。

6.本发明是在传统的负电容鳍式场效应晶体管工艺上,增加了不同材料、厚度可调的双层侧墙的工艺步骤,具体是:

7.通过在源/漏极与栅极之间引入两种不同介质和不同厚度的双层侧墙,形成在靠近金属栅极的一定区域内同时引入high-k侧墙和low-k侧墙的结构。

8.其中:

9.所述high-k侧墙使得沟道耗尽程度加深,从而增加沟道的有效长度和有效面积,

用于抑制金属栅极功函数随机分布引起的阈值电压提高栅极对沟道的控制性能。

10.所述low-k侧墙用于负电容鳍式晶体管的寄生电容与串联电阻。

11.优选的,在所述工艺步骤中先完成high-k侧墙,其材质为hfo2,在源端high-k侧墙和漏端high-k侧墙的外侧再沉积low-k侧墙,其材质为sio2,从而构成所述的双层侧墙。

12.优选的,所述的双层侧墙的厚度不超过负电容鳍式场效应晶体管的总栅长,双层侧墙的厚度超出栅极高度的11%。

13.优选的,所述的high-k侧墙的厚度不超过low-k侧墙的25%。

14.本发明提出的具有双层侧墙结构的nc-finfet中,所述源端low-k侧墙和漏端low-k侧墙材料与所述源端high-k侧墙和漏端high-k侧墙均是通过改变沉积介电材料来实现,从而有效地抑制金属栅极功函数随机变异导致的器件性能波动的影响。

15.本发明提出的具有双层侧墙结构的nc-finfet中,由于双层侧墙结构中high-k材料的存在,增加了沟道的有效长度和有效面积,从而增加了栅极面积和tin金属晶粒尺寸的比值,也增强了器件的栅极控制能力;同时由于侧墙引入的栅-源电容和栅-漏电容可以更好地匹配铁电负电容,进而提升了器件的开态电流(i

on

)。又由于双层侧墙中存在low-k材料,又可以有效地降低寄生电容,不会增加器件的本征延时,保证了器件的总体性能。

附图说明

16.图1为n型负电容鳍式场效应晶体管(nc-finfet)结构示意图;

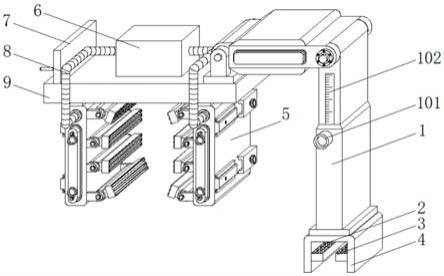

17.图2为具有双层(双材料)侧墙结构的nc-finfet示意图。

具体实施方式

18.本实施例提出了一种具有不同材料厚度可调双层结构的侧墙技术,通过调节双层侧墙结构中的low-k与high-k侧墙的材料种类和厚度,增加有效栅极长度和栅极面积,从而有效的抑制金属栅极功函数的随机分布而导致的器件性能波动的问题,进而提高芯片的成品率和可靠性。

19.本实施例的具体技术方案见图2,晶体管结构包括:沟道区、栅氧化层、栅极铁电层、栅极金属层、衬底、源极、漏极、源端low-k侧墙、源端high-k侧墙、漏端low-k侧墙、漏端high-k侧墙。沟道外围沿水平方向依次设置源端low-k侧墙、源端high-k侧墙、栅极介电层和漏端high-k侧墙、漏端low-k侧墙。

20.所述衬底的结构为体硅结构,材料为硅本征半导体并掺杂硼元素构成p型衬底。

21.所述源端low-k侧墙和漏端low-k侧墙的厚度和使用的材料类型相同,为低介电常数材料,包括氮化硅(sin)或二氧化硅(sio2)。

22.所述源端high-k侧墙和漏端high-k侧墙的厚度和使用的材料类型相同,为高介电常数的材料二氧化铪(hfo2)。

23.所述栅极氧化层为high-k材料hfo2。

24.所述栅极铁电层为掺杂的铪基氧化物zr-hfo2。

25.所述栅极金属层为氮化钛(tin)材料。

26.本实施例中的晶体管工艺步骤主要如下:

27.制备硼掺杂的体硅衬底;

28.采用反应离子刻蚀技术,将硅锗层刻蚀成鱼鳍状,并进行一次热退火;

29.采用化学气相沉积技术,积淀high-k介质hfo2和掺杂锆;

30.采用原子层沉积技术,沉积栅极,沉积完成后进行一次快速热退火;

31.采用化学气相沉积技术,淀积双层电介质薄膜,形成high-k漏侧墙,low-k漏侧墙和high-k源侧墙,low-k源侧墙;

32.源漏外延区的生长以及五族元素砷的掺杂;

33.积淀光刻胶与刻蚀工艺;

34.完成1050℃的快速退火;

35.温度为1398℃和时间为1.0ms的激光退火;

36.进行电极触点的镍硅化。

37.本发明相对于传统的nc-finfet增加了不同材料、厚度可调的双层侧墙的工艺步骤。本发明先完成第一层high-k侧墙,其材质为hfo2等高介电常数的材料,在源端high-k侧墙和漏端high-k侧墙的外侧沉积low-k侧墙,其材质为sio2等低介电常数的材料。在靠近栅极的位置使用high-k侧墙,而在外围使用low-k侧墙,目的是在保证提高栅极控制能力的同时减小器件的寄生电容。其可以有效抑制金属栅极功函数变异带来的性能波动影响,又可以减小器件的本征延迟。其特点是这种方法与目前业界普遍使用的后栅工艺(gate-last)制备nc-finfet的工艺大致相同,整个实现方案和制造步骤与现有工艺相比并没有明显增加难度与复杂度。

38.进一步,关于侧墙工艺的几何结构细节如下:整个侧墙的厚度不超过nc-finfet器件总栅长(lg)的大小,high-k侧墙的厚度不超过low-k侧墙的25%,侧墙的高度一般超出栅极高度11%。

39.本发明的主要原理是:由于原子层沉积(ald)技术导致金属栅极晶粒的取向不同,又因为不同的晶粒取向具有不同的功函数值,且该值服从二项分布,因此实际器件会由于功函数随机变异引起器件阈值电压、驱动电流、本征延时等性能参数的波动,进而改变器件的预期性能,导致芯片实际制造成品率下降和可靠性降低。本发明通过在源/漏极与栅极之间引入两种不同介质和不同厚度的双层侧墙,形成在靠近金属栅极的一定区域内同时引入high-k侧墙和low-k侧墙的结构。由于high-k侧墙的存在,使得沟道耗尽程度加深,从而增加沟道的有效长度和有效面积,这可以抑制金属栅极功函数随机分布引起的阈值电压等变化,还能够提高栅极对沟道的控制性能。此外,由于high-k侧墙的存在能够有效的增加势垒高度,减小器件的漏致势垒降低(dibl)效应,降低器件的关态电流(i

off

),从而改善器件的短沟道性能和静态功耗。其余部分引入的low-k侧墙,目的是减小器件的寄生电容与串联电阻,不仅有效的减小了器件的本征延时,还可以缓解器件的自热效应。

40.本领域的普通技术人员应当认识到,以上实施步骤和方案仅是用来对本发明的说明和解释,而非作为对本发明的限定,只要是在本发明的范围内,对以上实施步骤和方案的变化,变形都将落在本发明的保护范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。