1.本发明涉及计算架构领域,更具体地,涉及用于脉冲神经网络的硬件架构和操作网络的方法。

背景技术:

2.由于在许多诸如图像分类和对象辨识等应用环境中取得的最新成果,机器学习在研究和工业中引发了空前的兴趣。然而,由于这些系统的配置要求巨大的计算能力,使得他们不适合于嵌入式系统。为了解决这样的限制,许多研究者正在研究类脑计算(brain-inspired computing),类脑计算是满足计算性能要求的传统的基于冯诺依曼架构的计算机(cpu/gpu)的替代品。然而,该方法存在能量效率问题,并且需要设计既适用于并行计算又适用于分布式计算的神经形态硬件电路。

3.过去十年,人工智能(ai)越来越多地引起了工业机构和研究机构的关注。人工神经网络(ann)源自生物大脑并从生物大脑得到启发,已成为最知名和最频繁使用的ai形式。尽管近年来ann受到了许多关注,但其源于20世纪40年代第一台计算机的出现。随后的工作和进步引起了多种ann模型的发展。然而,这些模型中的许多都只停留在理论上,当时并没有针对工业用途而实施。

4.近来,这些算法之所以变得有竞争力,是因为两个因素:一、现代计算机已达到充分的计算性能来处理ann训练和推理;二、可用的数据量呈指数增长,满足了用于ann的大量的训练数据需求。

5.然而,由复杂形式的ann计算所带来的能量和硬件资源集中与另一种当前的新兴技术,即iot(物联网)和边缘计算不匹配。为了使ann在嵌入式环境中执行,必须为ann加速部署专用硬件架构。在这种情况下,神经形态结构的设计在与脉冲神经网络的研究相结合时尤其有趣。

6.用于深度学习和知识表示的脉冲神经网络(snn)是当前的一个问题,尤其与对神经科学和机器学习两者都感兴趣的研究者的团体有关。文献中已提出了若干特定的硬件解决方案,但它们仅仅是与网络拓扑常常受电路架构的特性的约束的整体空间设计隔离开的解决方案。

7.发明人的文章“脉冲神经网络的信息编码和硬件架构”,2019年第二十二届欧洲数字系统设计(dsd)会议(euromicro conference on digital system design),ieee,2019年8月28日,第291页-第298页,xp033637577中提出了两个不同的用于脉冲神经网络的硬件架构的设计:时分多路复用结构(tma)和全并行结构(fpa)。

8.这些架构方案是硬件实施的经典模型。在snn的情况下,这些结构没有利用贯穿网络深度的活动减少的优势。实际上,对这些网络的动态进行更多精确的分析表明大多数的脉冲是由输入层生成的。第一神经层(尤其在卷积层的情况下)充当低通滤波器,其大幅度地减少了输出脉冲的数量。因此,端到端以全并行方式工作未充分利用hw处理元件的数量并造成能量消耗。此外,fpa的实施方式不支持基于事件的处理,并且基于帧的方式操作。另

一方面,端到端以时分多路复用方式工作需要顺序地处理所有脉冲。这导致了剩下较大数量的脉冲的第一神经层中的时间开销。

9.发明人推荐截然不同的方法,其在于生成最佳地支持网络拓扑的结构。

10.因此,需要一个解决方案以解决前述问题。并且需要既可以适用于并行计算也可以适用于分布式计算的神经形态硬件电路。本发明提供了这种解决方案。

技术实现要素:

11.根据本发明的第一实施例,提供了一种如在随附的独立权利要求1中所进一步描述的系统。

12.本发明的目的在于一种适于脉冲神经网络的实施方式的神经形态硬件架构。具体地,本发明提供了一种结合全并行硬件层和时分多路复用硬件层的混合架构。本发明的混合架构满足特定于应用的约束。

13.有利地,描述了结合时分多路复用硬件和并行硬件实施方式的优点的新颖的混合架构。

14.实际上,在该架构中,称为全并行隐藏层的第一隐藏层在全并行处理模块中实现,称为时分多路复用隐藏层的多个更深的隐藏层在时分多路复用处理模块中实现。该混合架构非常适合脉冲选择编码方法。

15.在snn中,混合架构通过使并行性适应每个层的活动来使得脉冲的高效处理成为可能。混合架构模型打破了fpa和tma的统一处理。因此,实现了异步处理脉冲的特定控制单元。混合架构保证了最优的基于事件的处理,其中单元仅在脉冲出现时被激活。此外,混合架构通过调整并行性和延迟提供优化的能量消耗。

16.混合架构使用神经编码方案将输入数据转换为具有编码范式的脉冲序列,其以在网络中传播较少数量脉冲为特征。

17.有利地,在保持相同的分类准确度的同时减少了待处理的脉冲事件数量。通过这样做,硬件所消耗的电力量减少。

18.混合架构已在vhdl中开发并在寄存器传输级(rtl)中进行了仿真。

19.网络中的大多数脉冲活动位于第一层。因此,第一隐藏层是在处理期间最需要的层。为了利用该方面优势,设计的混合架构混合了时分多路复用架构(tma)和全并行架构(fpa),其中,一、初始两个层通过使用具有类似于fpa的结构的神经核模块实施;以及二、如在tma中那样,其余层是每层使用一个npu的时分多路复用的层。在大型的脉冲神经网络的情况下,时分多路复用部分由网络控制器驱动,网络控制器管理npu并将npu连接到持有npu的逻辑权重的sdram,以及从外部的sdram存储器检索权重并将权重转发至对应的npu。这种新颖的混合架构尤其适于使用脉冲选择编码,在脉冲选择编码中脉冲活动集中在第一层。

20.本发明的混合架构利用了随着进入到更深层的网络而增加的脉冲活动稀疏性。这种新颖的混合架构针对最需要的层具有全并行计算核且针对更深的层具有时分多路复用计算单元架构,当与所建议的脉冲选择编码结合时,似乎成为针对将来的深度snn在嵌入系统中实施的最适当的方法之一。

21.本发明的混合架构适于基于全连接的snn的实施和脉冲卷积神经网络的实施。

22.所请求保护的用于脉冲神经网络的硬件架构包括:

[0023]-用于接收输入像素和生成脉冲流的脉冲生成器;

[0024]-用于接收脉冲流和对脉冲流进行滤波以生成数量减少的脉冲的神经核模块;

[0025]-用于处理数量减少的脉冲的神经处理单元模块;

[0026]-用于选择输出赢者类的分类模块;

[0027]

硬件架构的特征在于神经核模块包括隐藏的全并行层以并行地处理所接收的输入脉冲,以及神经处理单元模块包括多个隐藏的时分多路复用层以顺序地处理数量减少的脉冲。

[0028]

根据各个实施例的:

[0029]-脉冲生成器被实施为神经编码功能,如速率编码或者脉冲选择编码。

[0030]-神经核模块包括接收脉冲流的输入层和实施为全并行电路以处理脉冲的第一隐藏层。

[0031]-多个隐藏层中的每一层包括神经处理单元模块,从而仿真时分多路复用层。

[0032]-分类模块是终止增量类模块(termination delta like module)。

[0033]-脉冲流在基于事件的数据模式中被处理,在该模式下,只有脉冲事件被架构的每个层处理。

[0034]-脉冲流在基于帧的数据模式中被处理,在该模式下,输入帧中的每一个“0”和“1”被架构的每个层处理。

[0035]

本发明还请求包括所请求的混合架构的现场可编程门阵列(fpga)或专用集成电路(asic)。

[0036]

本发明还提出了操作所请求的混合架构的方法。

[0037]

基于对附图和详细描述的审视,本发明的其他优点将对于本领域技术人员而言变得清楚。任何附加的优点旨在合并在其中。

附图说明

[0038]

现在将参考附图举例说明本发明的实施方式,在附图中,相同的参考标记表示相似的元件,以及在附图中:

[0039]

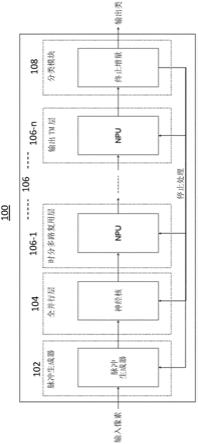

图1a示出了本发明的硬件混合架构的一般框图;

[0040]

图1b示出了用于大型的snn和基于帧的脉冲数据的实施例中硬件混合架构的一个实施方式;

[0041]

图2a示出了实施例中本发明的神经核模块的详细框图;

[0042]

图2b示出了本发明的神经核模块的另一个实施例;

[0043]

图3示出了实施例中本发明的神经处理单元模块的详细框图;

[0044]

图4a和图4b示出了两个实施例中本发明的分类模块的详细框图;

[0045]

图5示出了实施例中用于实施例的本发明的网络控制器模块的详细框图;

[0046]

图6是关于操作本发明的混合架构的一般步骤的流程图;

[0047]

图7是实施例中关于操作本发明的神经核模块的步骤的流程图;

[0048]

图8是实施例中关于操作本发明的神经处理单元模块的步骤的流程图;以及

[0049]

图9示出了实施例中if神经元模块的框图。

具体实施方式

[0050]

在进行附图的说明之前,先参考发明人发表的文章,文章名为“用于嵌入式人工智能的硬件脉冲神经元的空间设计探索”,2019,其全文合并与此。

[0051]

首先参考非限制示例图1a,描述了本发明的硬件混合架构的一般架构。本发明的混合架构允许处理基于事件的数据,其中只有脉冲事件(例如,输入数据等于

‘1’

)被架构的每个层处理,或者允许处理基于帧的数据,其中输入帧中的每一个“0”和“1”均被架构的每个层处理。

[0052]

脉冲事件表示在架构的前一个层中的发射脉冲的神经元的地址。

[0053]

系统100被图示为具有若干功能块电路,包括脉冲生成器102、全并行层或实现隐藏的全并行层的神经核(nc)模块104、时分多路复用层或实现多个隐藏的时分多路复用层(106-1、106-i至106-n)的神经处理单元(npu)模块106、以及终止增量(termination delta)或分类模块108。

[0054]

系统100的一般操作是从图像的输入像素生成脉冲流,之后脉冲流输入到神经核104,在神经核104中脉冲以并行处理被滤波。之后数量减少的脉冲通过多个神经处理单元106-i以时分多路复用方法被处理;以及最终操作允许对嬴者输出类进行分类和选择。

[0055]

受神经科学启发,信息(输入像素)通过脉冲生成器102被编码到脉冲中。实际上,神经元模型模拟了基于动作电位的突触通信机制和生物神经元。信息因此通过多种神经编码技术(举几个例子来说,如速率编码、脉冲选择、单突发)表示为脉冲流。本领域技术人员将参考先前引用的发明人的文章来得到这些方法的更多细节。

[0056]

在图2a中示出了优选实施方式的神经核模块104为仿真了两个层(输入层202和全并行层204)的计算单元。输入层202包括输入神经元模块,其将“输入事件”即脉冲流转发到下游神经元电路,下游神经元电路被实施为全并行架构(fpa),其允许并行地处理脉冲流的脉冲事件,以对多个脉冲进行过滤并生成数量减少的脉冲。每个逻辑神经元由专用硬件电路“神经元1至神经元n”来表示,在说明书中不同地命名为“神经元电路”或“硬件神经元”或“if神经元模块”(针对整合发放integrate-and-fire神经元)。

[0057]

输出自fp层204的减少的脉冲流输入到神经核控制206。神经核控制由

‘

1:n’计数器、多路复用器(mux)和输出先进先出(fifo)缓冲器组成。可以注意到

‘

n’是fp层204的神经元电路的数量。当fp层204的n个神经元电路并行地处理输入的脉冲事件(即,源自所输入的脉冲流的脉冲)时,n个神经元电路的输出脉冲通过多路复用器mux顺序地连接到输出fifo缓冲器的写入使能端。mux块被配置为通过使用由1:n计数器给定的地址(@neuron)一个接着一个地选择输出脉冲。这些地址也连接到fifo模块的输入数据。在输出脉冲为高(脉冲=1)的情况下,计数器的输出(即,神经元的地址)写入到输出缓冲器(fifo)中。一旦计数器结束fp层204的所有输出脉冲的转发,计数器重置计数并为接下来的脉冲重复相同的过程。

[0058]

接下来,神经核104的输出

‑‘

输出事件

’‑

成为混合架构的时分多路复用部分的输入。

[0059]

图7是用于操作在图2a中示出的神经核模块的步骤的流程图。

[0060]

步骤700从读取输入脉冲地址(@in)和由终止增量模块108提供的

‘

stop_network’信号开始。一方面703,过程允许验证

‘

stop_network’信号是否等于“1”来结束过程700。另一方面704,输入脉冲地址@in被发送到fp层的神经元电路以执行整合发放规则。对每一个

神经元进行计算704,输入地址@in用于检索对应于累积到神经元si的内部电位的权重。如在706中,以并行的方式将每个累积电位与阈值“th”相比较。当电位高于阈值时,发射脉冲,即,脉冲=1,并且通过将电位减少到阈值“th”来更新电位。之后这些脉冲在fifo中用于写入输出脉冲地址作为脉冲事件。由计数器控制的多路复用器用于一个接一个地顺序地转发脉冲708。如果发射了脉冲710,则已经发射脉冲的神经元的地址(脉冲事件)被保存在fifo缓冲器中711。一旦计数器转发了所有脉冲,在712中验证“计数=n-1”712,计数重置(计数=0)713,并且通过读取新的输入(@in和stop_network)702重复上述过程。

[0061]

有利地,由于脉冲的数量通过fpa模块而大幅度地减少,因此不需要这样的并行计算,并且多个npu模块106-i被实施为时分多路复用架构以允许顺序处理脉冲。计算循环与在npu中实施的逻辑神经元的数量一样多,分多路复用(tm)层的数量是针对特定的机器学习应用预定义的。

[0062]

最后一个npu的输出,即输出tm层成为分类模块(还被指定为终止增量、最大终止或赢者类模块)108的输入,其通过确定是否已经接收足以分类输入图像的足够数量的脉冲来确定是否结束分类过程。如果不是的话,重复过程,或者停止过程

‘

停止处理’。

[0063]

图6是关于操作本发明的混合架构的一般步骤(例如如图1a上所示)流程图。

[0064]

过程600通过加载或接收输入数据的第一步骤602开始。

[0065]

接下来,过程允许脉冲生成器从输入数据生成脉冲流604。

[0066]

在下一个步骤606,过程允许神经核模块以全并行处理通过减少数量的脉冲来处理脉冲流并且允许生成输出事件。

[0067]

接下来在步骤608-1至608-n,过程允许通过多个神经处理单元顺序地处理每个输出事件。

[0068]

在下一个步骤610,过程允许通过终止增量或分类模块处理最后一个npu的输出以确定赢者类。在最后步骤期间,如果终止增量确定赢者类,则过程允许激活

‘

stop_network’信号以停止过程。

[0069]

应当理解,过程600的所有步骤随着时间的推移以流水线方式工作,最优地使用架构的部件。例如,当步骤602加载下一个输入数据时,脉冲生成器渐进地转换先前产生的脉冲流的像素。同时,神经核处理这些输入脉冲,多个npu处理其他最近的数据,以及终止增量验证从最后一个npu(608-n)接收的当前的数据的分类。

[0070]

转到图1b,本发明的硬件混合架构的另一个实施方式示出了关于适于处理基于帧的(非基于事件)输入数据的实施例,其中输入帧中的每个

‘0’

和

‘1’

由架构的每个层处理。系统还包括网络控制器110和存储器112以覆盖大型的脉冲神经网络。

[0071]

网络控制器110允许管理用于处理的地址和权重。网络控制器耦接到能够存储权重的存储器112。存储器使用是snn架构的普遍限制,原因在于神经元的参数和活动必须被存储。从这个角度看,为了处理需要相当大的存储器尺寸的更深度的网络,fpga片上存储器是不够的。因此,外部存储器优选用于克服该问题。为了加强fpga结构的存储能力,在优选的实施例中使用sdram。网络控制器模块将其他模块连接到外部存储器。

[0072]

图2b示出本发明的适于处理基于帧的输入数据的神经核模块104的变型。在基于帧的或者非基于事件的数据中,输入脉冲不表现为指示已发射脉冲的像素地址的事件。然而,数据表现为一系列的“0”和“1”。脉冲等于“0”对应于没有发射脉冲的像素以及脉冲等于“1”对应于已发射脉冲的像素。为了处理这种数据,使用第一隐藏计数器来向神经元电路指示等于“1”的输入脉冲的地址以检索合适的权重,并且然后执行与图2a中描述的相同的处理。

[0073]“if神经元模块”整合从输入神经元模块进入的脉冲并且根据“整合发放”规则生成脉冲。权重存储在寄存器中,从而使得每个“if神经元模块”具有存储在专用寄存器中的自己的权重。if神经元模块的数量与fp层中的逻辑神经元的数量相同。if神经元模块的输出存储在fifo缓冲器中作为脉冲事件,计数器模块指示将被存储的对应神经元地址。输入神经元一个脉冲接一个脉冲地转发输入脉冲,其中每个脉冲指示其来源的地址(例如,图像中的像素的地址)。这些输入像素的输入脉冲地址被传送到隐藏的fp层神经元。fp层神经元使用这些地址访问它们的片上存储器权重以检索其适当的突触权重,并且然后执行“整合发放”规则。计数器(1:n)控制mux部件以读取隐藏的fp层神经元的输出脉冲并将其存储在输出fifo缓冲器中。

[0074]

图3示出了实施例中本发明的一个隐藏的时分多路复用层的神经处理单元模块106-i的详细框图。npu用于仿真时分多路复用层。当存在将被npu处理的输入事件时,首先,硬件神经元308被npu控制器302启用以从计数器304检索其代表的逻辑神经元的地址,并从存储块306检索对应的权重。其次,硬件神经元操作其计算,并且每当其发射时,输出脉冲被存储在fifo模块310中作为脉冲事件。

[0075]

单个if神经元模块对层中的所有神经元相继地进行操作(关于if神经元模块的实施方式在图9中示出)。此外,npu包括fifo存储器模块310、计数器模块304和npu控制器302。这些模块如图3中所示那样连接以形成npu,npu以连贯的方式处理脉冲事件。除npu控制器外,npu还使用如先前所描述的所有其他模块来完成它们的专用任务。npu控制器的目标是管理不同的npu部件以顺序地触发逻辑神经元,允许向硬件神经元提供有效的权重和活动。此外,不同npu的npu控制器彼此连接以保证网络级别的同步。需要同步是因为输出分类过程(终止模块)取决于脉冲的到达顺序。由于npu控制器和计数器,若干逻辑神经元能够被时分多路复用并且因此在单个npu中计算。

[0076]

图8是操作在图3上示出的神经处理单元模块的步骤的流程图。

[0077]

过程800通过加载输入事件(空的输入信号和停止处理信号)的第一步骤802开始。每当终止增量模块激活停止处理信号时,过程结束803。否则,npu通过验证空的输入信号“i_empty”的状态来检查输入事件的存在804。然后根据层类型(即,全连接层或卷积层)806,逻辑神经元的地址被转发到硬件神经元以检索内部活动和权重从而执行整合发放规则808。如果脉冲是高的(脉冲=1),则该神经元的输出保存在fifo缓冲器中810。对层的所有逻辑神经元重复由计数器控制812的过程。一旦所有神经元被处理,则新的输入被加载802以计算下一个输入脉冲。

[0078]

图4a和图4b示出了最大终止和终止增量实施例中本发明的分类模块108的详细框图。在开始描述之前,给出一个关于类选择过程的快速提醒。首先,注意每个输出神经元对应于数据类。在推理期间,嬴者类被选择作为最大值脉冲输出神经元。在终止增量(图4a)过程中,当最大值脉冲神经元具有增量倍于第二大值脉冲神经元的脉冲时实施类预测。另外,在最大终止(图4b)中,每当输出神经元(最大值脉冲神经元)达到最大值脉冲时,完成分类过程。增量值和最大值是用户定义的参数,通常设置成4。

[0079]

对于当前的混合架构的设计,为了选择输出赢者类,优选地选择终止增量或最大终止,这是因为它们提供了最先进的准确度和快速的类选择。图4a和图4b示出了这些模块的内部结构。模块的输入是包含snn的输出活动(到目前为止由每一个输出神经元发射的脉冲数量)的向量“激活”。

[0080]

一方面,在终止增量模块中,两个最大子模块被设计为检测阵列的最大值,其用于确定赢者类和停止处理。第一最大子模块,即max1,检测输出激活向量的最大值,并且第二最大子模块,即max2,检测相同向量的第二最大值。然后计算max1模块的输出和max2模块的输出之间的差。最后,如果差大于阈值增量值,则对应于max1模块的类被定为赢者。

[0081]

另一方面,最大终止模块仅整合了一个最大块,该最大块返回具有最高脉冲活动的输出神经元的索引和该输出神经元的活动。然后,比较该活动与用户定义的阈值最大值。如果最大脉冲活动大于最大值,则对应的输出神经元被定为赢者类,并且结束处理。

[0082]

图5示出了实施例中的本发明的网络控制器模块110的详细框图。网络控制器模块是fifo模块(队列)502和解复用器(demux)504的结合。fifo模块以先来先服务策略根据npu请求来访问sdram,即,当npu请求权重时,该请求被放入fifo队列中。然后,每当权重就绪,通过选择对应的npu模块经由demux块传送权重。

[0083]

应当理解,尽管本发明已经具体地示出并参考优选的实施例进行了描述,在不背离精神和本发明的范围的情况下,可以在其中作出形式和细节方面的各种改变。本发明可以有利地在现场可编程门阵列(fpga)或者专用集成电路(asic)上实现。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。