一种gan晶体管驱动电路

技术领域

1.本发明涉及gan晶体管,尤其涉及gan晶体管驱动电路。

背景技术:

2.随着电力电子系统的快速发展,功率半导体器件市场得到了快速的发展。硅基器件的性能已经逐渐达到了材料的理论极限,越来越不能满足现代高功率电力电子系统的需求。在这种情况下,以gan、sic为代表的第三代宽禁带半导体逐渐取代了si材料而成为了高温高频环境下器件设计的首选。

3.现有si器件的栅极驱动器不适用于gan器件的驱动,主要表现在增强型gan晶体管的栅极驱动电压较低(6v),而栅极击穿电压与完全开通电压之间的差值也很低(3v)。传统的使用simosfet产生栅极电压的栅极驱动器虽然对于大多数si mosfet器件有效,但是它却不能为gan器件提供低压栅极电压。不仅如此,现有的驱动采用的是与gan不兼容的si工艺制造,因此会增加栅极回路的电感,由于gan器件开通速度在纳秒级别,功率回路的dv/dt普遍大于100v/ns,这会导致栅极回路感应形成巨大的震荡。因此,使用传统的栅极驱动器直接驱动gan器件不仅可能会造成器件击穿,从而使得系统失效,还会引入电路震荡影响系统效率提升。

4.另一方面,现有技术中完全集成的gan驱动器虽然可以有效的驱动主gan器件正常工作,但是驱动器的内部结构往往较为复杂,开通和关断延迟较长。

技术实现要素:

5.本发明鉴于现有技术的以上情况作出,用于克服或缓解现有技术中存在的一个或更多个技术问题,至少提供一种有益的选择。

6.根据本发明的一个方面,提供了一种gan晶体管驱动电路,所述gan晶体管驱动电路包括上下管电路和上下管控制电路,所述上下管电路包括上管和下管所述上管和所述下管均为gan晶体管,所述上管的漏极与电源电压相连,所述上管的栅极与数字输入相连,所述上管的源极与所述下管的漏极相连,并作为所述gan晶体管驱动电路的输出与所述被驱动gan晶体管的栅极相连;所述下管的栅极与所述上下管控制电路相连接;所述上下管控制电路利用工作电压、电源电压以及数字输入,对所述下管进行控制,从而使所述gan晶体管驱动电路的输出与数字输入同相,所述上下管控制电路包括晶体管,并且所包括的晶体管均为gan晶体管,在栅极被施加高于阈值电压的电压时导通。

7.根据本发明的实施方式,驱动电路结构简单,延迟短。

8.依据本发明的一些实施方式,gan晶体管驱动电路和gan功率器件集成在单个芯片中,可以缩减系统的体积,降低功耗。

附图说明

9.结合附图,可以更好地理解本发明,在附图中:

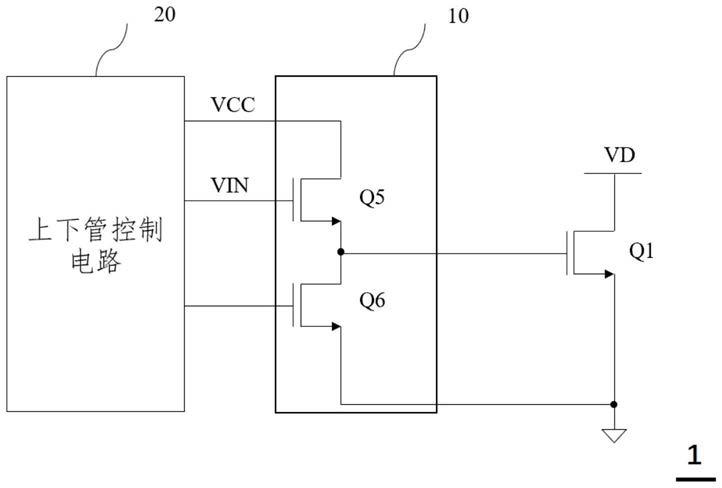

10.图1是依据本发明一种实施方式的gan晶体管驱动电路的概略示意图;

11.图2示出了依据本发明的另一种实施方式的gan晶体管驱动电路的示意图;

12.图3示出了依据图4所示的实施方式的输入输出波形;

13.图4示出了依据本发明的再一种实施方式的gan晶体管驱动电路的示意图;以及

14.图5示出了依据图4所示的实施方式的输入输出波形。

具体实施方式

15.图1是依据本发明一种实施方式的gan晶体管驱动电路的概略示意图。如图1所示,依据本发明的一种实施方式的gan晶体管驱动电路1用于驱动一被驱动gan晶体管q1,被驱动gan晶体管q1的漏极与母线电压vd相连接,源极与地相连接。该gan晶体管驱动电路1包括上下管电路10和上下管控制电路20。该上下管电路10包括上管q5和下管q6,所述上管和下管均为gan晶体管,具体地可以是增强型gan高电子迁移率晶体管(hemt),在栅极被施加高于阈值电压的高电压时导通。本领域技术人员应该理解,在本发明中,高于晶体管的阈值电压的电压均可被称为高电压,反之则可以被称为低电压。根据本发明的一种实施方式,母线电压vd可以为100v~650v的高压,电源电压vcc可以为6v,数字输入vin的逻辑高电平为12v,逻辑低电平为0v。因而电源电压vcc和数字输入vin的逻辑高电平均为高电压。

16.上管q5的漏极与电源电压vcc相连,栅极与数字输入vin相连,源极与下管q6的漏极相连,并作为该gan晶体管驱动电路1的输出与该被驱动gan晶体管q1的栅极相连。下管q6的栅极与上下管控制电路20相连接。该上下管控制电路20利用母线电压vd、电源电压vcc以及数字输入vin,对所述下管进行控制,从而使所述gan晶体管驱动电路的输出与数字输入vin同相。该上下管控制电路20包括晶体管,并且所包括的晶体管均为gan晶体管,在栅极被施加高于阈值电压的电压时导通。

17.根据该实施方式,上下管电路10以及上下管控制电路20所采用的晶体管均为gan晶体管,功能简单,因而整个电路结构简单、延迟短。

18.图2示出了依据本发明的一种实施方式的gan晶体管驱动电路的示意图。对照图1,上下管控制电路20包括第一晶体管q3、第二晶体管q4和第三晶体管q2。

19.该第一晶体管q3的漏极与该第三晶体管q2的源极以及下管q6的栅极相连,该第一晶体管q3的栅极与该第二晶体管q4的源极相连,该第一晶体管q3的源极接地。

20.第二晶体管q4的漏极与数字输入vin相连,第二晶体管q4的栅极与电源电压vcc相连,第二晶体管q4的源极与第一晶体管q3的栅极相连。

21.第三晶体管q2的漏极与工作电压vd相连,第三晶体管q2的栅极与下管q6的漏极以及上管q5的源极相连,第三晶体管q2的源极与第一晶体管q3的漏极相连。

22.当vin为高电压时,上管q5导通。同时,由于第二晶体管q4处于常开的状态,因而vin通过第二晶体管q4施加到第一晶体管q3的栅极,从而第一晶体管q3被导通。这样下管q6的栅极被施加了低电压,从而下管q6关断。由于如上所述,上管q5导通而下管q6关断,晶体管q2开通,因而被驱动gan晶体管q1的栅极被施加了高电压。当vin为低电压时,上管q5关断。同时,由于第二晶体管q4处于常开的状态,因而低电压的vin通过第二晶体管q4施加到第一晶体管q3的栅极,从而第一晶体管q3也关断。在晶体管q3关断的瞬间,由于电路存在延迟,晶体管q2依然处于导通状态,使得下管q6的栅极与母线电压处于同一电位,由于保护二

极管d1的存在,使得下管q6既保持开通又不会被母线电压击穿。当电路处于稳态时,上管q5关断,下管q6开通,因而被驱动gan晶体管q1的栅极被施加了低电压。

23.根据本发明的一种实施方式,第三晶体管q2、第一晶体管q3、上管q5和下管q6的栅宽相同,第二晶体管q4的栅宽为第三晶体管q2的栅宽的5%-30%,更优选地为10%。利用这样的技术方案,可以提高驱动电路的响应速度。在本发明中,两个晶体管的栅宽相同是指一个晶体管的栅宽与另一个晶体管的栅宽之差在该一个晶体管的栅宽的10%的范围内。

24.根据一种实施方式,本发明的被驱动晶体管q1和gan晶体管驱动电路集成在单个芯片上。

25.图3示出了依据图2所示的实施方式的输入输出波形。从图3的波形图可以看出,被驱动器件q1的栅极电压与数字输入vin非常契合地同相,延迟短,并能够稳定输出。

26.图4示出了依据本发明的再一种实施方式的gan晶体管驱动电路的示意图。如图4所示,在电源电压vcc和上下管电路之间设有稳压电路30。

27.虚线框中结构与图2所示的实施方式相同,因此不予赘述。

28.虚线框外的稳压电路由晶体管q7,电阻r1、r2,电容c1和二极管d2组成ldo(低压差线性稳压器)来提供上管q5的漏极所需要的电压。

29.在此实施方式中,晶体管q7的漏极与电源电压vcc相连,源极与电容c1的一端相连,电容c1的另一端与电阻r2的一端相连,电阻r2的另一端接地。电源电压vcc还与电阻r1的一端相连,电阻r1的另一端与晶体管q7的栅极以及二极管d2的正极相连,二极管d2的负极接地。其中晶体管q7与q4栅宽相同,二极管d2为钳位二极管,钳位电压为9v。

30.电容c1可以用增强型器件源漏短接和栅极来实现替换。另外,电阻r1、r2,电容c1和二极管d2也可以在芯片的外部由分立的元件组成。

31.根据本实施方式,电源电压vcc和数字输入vin的逻辑高电可平均为12v,数字输入vin的逻辑低电平为0v。

32.图5示出了依据图4所示的实施方式的输入输出波形。从图5的波形图可以看出,被驱动器件q1的栅极电压与数字输入vin非常契合地同相,延迟短,并能够稳定输出。同时上管q5漏极处的电压也非常稳定。

33.根据本发明的实施方式,可能具有以下的一项或更多项的优点。

34.(1)整颗芯片内部全部采用gan晶体管,更加有利于栅驱动电路和主器件的单片集成。

35.(2)所设计的驱动电路可以为主器件(晶体管q1)提供更加精确的栅极电压,从而主器件可以安全稳定的工作。

36.(3)在为主器件提供符合要求的栅极电压前提下,实现了驱动器体积和功耗的进一步降低。

37.但是本领域的技术人员应该理解,根据本发明的一些实施方式,也可以不具有以上的任何优点,而只是提供另一种选择。

38.本发明的上述详细的描述仅仅用于使本领域技术人员更进一步的连接本发明,以用于实施本发明,并不会对本发明的范围进行限制。仅有权利要求用于确定本发明的保护范围。因此,在前述详细描述中的特征的结合并不必然表示本发明的最宽范围。为了获得本发明的附加有用实施例,在说明书中给出教导的各种不同的特征可通过多种方式结合,这

些组合都在本发明的范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。