1.本发明涉及半导体集成电路技术领域,更具体地涉及一种开关变换器及其时钟同步电路。

背景技术:

2.随着便携式电子产品的普及,开关电源越来越重要,现代电子设备使用的电源大致分为线性稳压电源和开关稳压电源。线性稳压电源的调整管工作在放大区,具有不会引入额外的干扰,可靠性好和成本低的优势,但是它还有体积较大,变换效率低的缺点。开关稳压电源与线性稳压电源相比,具有可以升压和降压,供电效率高的特点。然而,开关稳压电源调节电压和电流时会产生电磁干扰噪声(emi),这种电气噪声可以传输到交流电力线上,不仅会通过传导影响电源附近的其他电子设备的允许,还可能从电源线辐射或泄露,影响没有连接到电源线上的设备。这些干扰会随着开关频率的提高,输出功率的增大会显著的增强,对电子设备的正常工作构成了潜在的威胁。

3.开关电源的工作时钟一般由内部振荡器来提供,但是由于内部提供的频率固定,不能随时改变来适应不同的应用环境。因此,对于开关电源来说,需要有外部时钟同步功能,即由外部时钟来代替内部振荡器产生的内部时钟作为开关电源的工作时钟,以抑制差频噪声,并适应于不同的应用环境。

4.现有的内部时钟和外部时钟之间切换的方法是在振荡器上设置两个引脚,一个引脚作为固定频率设定引脚,另一个引脚作为时钟同步引脚。当外部时钟信号输入时,通过外部时钟信号覆盖电路内部的固定频率,从而使得振荡器产生的时钟信号与外部时钟信号同步。这种方法的缺点是外部时钟信号的频率必须大于电路内部的固定频率才能正常同步时钟,所以在实际应用时外部时钟信号的频率变化的范围非常小,限制了开关电源的应用范围。另外,这种方法在内部时钟切换到外部时钟时,芯片的频率会发生突变,从而导致开关电源的输出端在切换瞬间出现较大的电压波动,降低了系统的稳定性,甚至可能会导致芯片的损坏。

技术实现要素:

5.有鉴于此,本发明的目的在于提供一种开关变换器的时钟同步电路和开关变换器,只需要在芯片上设置一个引脚就可以自动识别外部要求的工作模式,外部时钟的频率范围不受电路内部时钟的频率限制,并且可以实现内部时钟和外部时钟之间的平滑切换。

6.根据本发明的一方面,提供了一种开关变换器的时钟同步电路,包括:内部时钟控制电路,用于在内部频率模式下根据输入引脚的外接电阻的电阻值生成对应的第一控制电压;锁相环电路,用于在同步频率模式下根据所述输入引脚的外部时钟信号生成对应的第二控制电压;信号检测电路,用于根据所述输入引脚是否存在外部时钟信号以控制所述时钟同步电路工作于所述内部频率模式或者所述同步频率模式,其中,所述锁相环电路包括压控振荡器,所述压控振荡器用于在所述内部频率模式下根据所述第一控制电压产生与内

部时钟信号频率同步的时钟信号作为所述开关变换器的工作时钟,或者在所述同步频率模式下根据所述第二控制电压产生与所述外部时钟信号频率同步的时钟信号作为所述开关变换器的工作时钟。

7.可选的,所述信号检测电路用于在所述输入引脚存在所述外部时钟信号的情况下使能所述锁相环电路,关闭所述内部时钟控制电路,以控制所述时钟同步电路工作于所述同步频率模式,以及在所述输入引脚不存在所述外部时钟信号的情况下使能所述内部时钟控制电路,关闭所述锁相环电路中的部分电路,以控制所述时钟同步电路工作于所述内部频率模式。

8.可选的,所述电流产生模块包括:串联连接于电源电压和所述外接电阻之间的第一晶体管和第二晶体管;第三晶体管,第一端与所述电源电压连接,第二端用于提供与所述外接电阻的电阻值对应的输出电流,所述第三晶体管与所述第一晶体管构成电流镜;第一运算跨导放大器,同相输入端用于接收第一参考电压,反相输入端连接于所述第二晶体管和所述外接电阻的中间节点,输出端与所述第二晶体管的控制端连接;第一电阻,第一端与所述第三晶体管的第二端连接,第二端接地;第二运算跨导放大器,同相输入端与所述第一电阻的第一端连接,反相输入端与输出端连接,输出端用于输出所述第一控制电压;以及第一开关,连接于所述第二运算跨导放大器的输出端与所述压控振荡器之间,所述信号检测电路用于控制所述第一开关的导通和关断,以控制所述第二运算跨导放大器与所述压控振荡器的通路的通断。

9.可选的,所述锁相环电路还包括:史密斯触发器,用于根据所述外部时钟信号生成时钟参考信号;鉴频鉴相器,与所述史密斯触发器连接,用于比较所述时钟参考信号与时钟反馈信号的相位和频率;电荷泵,与所述鉴频鉴相器连接,用于将所述时钟参考信号与时钟反馈信号的相位差和频率差对应的所述电压信号转换为电流信号;环路滤波器,通过第二开关与所述电荷泵连接,用于滤除所述电流信号中的高频分量,从而生成所述第二控制电压,所述第二控制电压用于调节所述压控振荡器的输出频率,以使得所述压控振荡器生成与所述外部时钟信号频率同步的时钟信号;以及分频器,与所述压控振荡器和所述鉴频鉴相器连接,用于根据所述压控振荡器输出的时钟信号生成所述时钟反馈信号,并反馈至所述鉴频鉴相器的输入端,其中,所述信号检测电路控制所述第二开关的导通和关断,以控制所述电荷泵和所述环路滤波器之间通路的通断。

10.可选的,所述信号检测电路用于在所述输入引脚检测到外部时钟信号的情况下关断所述第一开关,并导通所述第二开关,以及在所述输入引脚未检测到所述外部时钟信号的情况下导通所述第一开关,并关断所述第二开关。

11.可选的,所述环路滤波器的输出端与所述第一开关的第二端连接,以在所述内部频率模式下用于所述第一控制电压的输出补偿。

12.可选的,所述环路滤波器选自无源电容电阻网络。

13.可选的,所述压控振荡器包括:连接于电源电压和地之间的压控电流源和电容,所述压控电流源用于生成与所述第一控制电压或所述第二控制电压对应的充电电流;第三开关,第一端与所述电容的第一端连接,第二端接地;比较器,同相输入端与所述电容的第一端连接以接收一斜坡电压,反相输入端用于接收第二参考电压,所述比较器用于比较所述斜坡电压与所述第二参考电压,以输出一比较信号;以及逻辑单元,用于根据所述比较信号

生成所述时钟信号。

14.可选的,所述第三开关的导通和关断受控于所述时钟信号,以在所述第三开关关断期间基于所述充电电流对所述电容进行充电,在所述第三开关导通期间对所述电容进行放电。

15.根据本发明的另一方面,提供了一种开关变换器,包括:主电路,采用至少一个开关管控制输入端向输出端的电能传输,从而根据直流输入电压产生直流输出电压;控制电路,用于根据一时钟信号控制所述至少一个开关管的导通时刻;以及上述的时钟同步电路,用于生成所述时钟信号。

16.可选的,所述主电路采用选自以下任一种的拓扑结构:降压型、升压型、升降压型、非逆变升降压型、正激型、反激型。

17.本发明实施例的开关变换器及其时钟同步电路包括内部时钟控制电路、锁相环电路和信号检测电路,信号检测电路根据输入引脚是否存在外部时钟信号以控制时钟同步电路工作于内部频率模式或者同步频率模式,内部时钟控制电路在内部频率模式下根据输入引脚的外接电阻的电阻值生成对应的第一控制电压,锁相环电路在同步频率模式下根据输入引脚的外部时钟信号生成对应的第二控制电压,其中,锁相环电路包括压控振荡器,用于在内部频率模式下根据第一控制电压产生与内部时钟信号频率同步的时钟信号,或者在同步频率模式下根据第二控制电压生成与外部时钟信号同步的时钟信号,只需要在芯片上设置一个引脚就可以自动识别外部要求的工作模式,同时完成内部时钟频率设置和外部时钟频率同步的功能,配置方式简单,可靠性高,能够满足不同的应用要求。

18.进一步的,本发明实施例的信号检测电路通过检测外部时钟信号的上升沿的方式使能控制内部时钟控制电路和锁相环电路的工作状态,不需要外部时钟信号的频率必须大于电路内部的固定频率也可以正常同步时钟,提高了外部时钟信号的频率变化范围,解决了开关变换器的工作频率受到限制的问题。

19.进一步的,锁相环电路还包括环路滤波器,该环路滤波器还用于在内部频率模式下对内部时钟控制电路生成的第一控制电压进行输出补偿,提高了环路稳定性,解决了从内部时钟切换到外部时钟时芯片的频率会发生突变的问题,继而降低了开关变换器在切换瞬间的输出电压纹波,提高了系统的稳定性和可靠性。

附图说明

20.通过以下参照附图对本发明实施例的描述,本发明的上述以及其他目的、特征和优点将更为清楚。

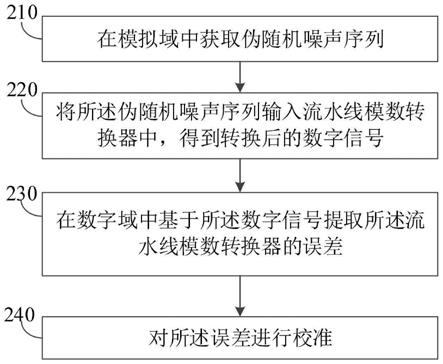

21.图1示出了根据本发明第一实施例的一种开关变换器的示意性电路图;

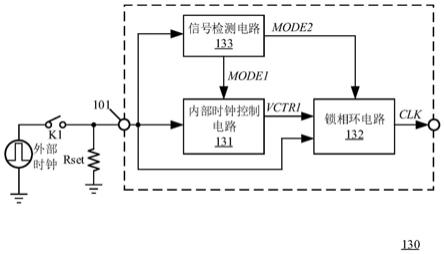

22.图2示出了根据本发明第二实施例的一种开关变换器的时钟同步电路的结构示意图;

23.图3示出了根据本发明第二实施例的时钟同步电路的一种示意性电路图;

24.图4示出了根据本发明第二实施例的时钟同步电路中的环路滤波器的示意性电路图;

25.图5示出了根据本发明第二实施例的时钟同步电路中的压控振荡器的示意性电路图;

26.图6a示出了根据本发明第一实施例的开关变换器从内部频率模式切换至同步频率模式的工作波形图;

27.图6b示出了根据本发明第一实施例的开关变换器从同步频率模式切换至内部频率模式的工作波形图。

具体实施方式

28.以下将参照附图更详细地描述本发明。在各个附图中,相同的元件采用类似的附图标记来表示。为了清楚起见,附图中的各个部分没有按比例绘制。此外,在图中可能未示出某些公知的部分。

29.在下文中描述了本发明的许多特定的细节,例如部件的结构、材料、尺寸、处理工艺和技术,以便更清楚地理解本发明。但正如本领域的技术人员能够理解的那样,可以不按照这些特定的细节来实现本发明。

30.应当理解,在以下的描述中,“电路”可包括单个或多个组合的硬件电路、可编程电路、状态机电路和/或能存储由可编程电路执行的指令的元件。当称元件或电路“连接到”或者“耦合到”另一元件,或称元件/电路“连接在”或者“耦合在”两个节点之间时,它可以直接耦合或连接到另一元件或者二者之间也可以存在中间元件,元件之间的连接或耦合可以是物理上的、逻辑上的、或者其结合。相反,当称元件“直接耦合到”或“直接连接到”另一元件时,意味着两者不存在中间元件。

31.在本技术中,开关管是工作开关模式以提供电流路径的晶体管,包括选自双极晶体管或场效应晶体管的一种。开关管的第一端和第二端分别是电流路径上的高电位端和低电位端,控制端用于接收驱动信号以控制开关管的导通和关断。

32.图1示出根据本发明第一实施例的一种开关变换器的示意性电路图。如图1所示,开关变换器100的主电路包括串联连接在输入端和接地端之间的开关管md1和md2,电感lx连接在开关管md1和md2的中间节点和输出端之间,输出电容co连接在输出端和接地端之间。开关变换器100的输入端接收直流输入电压vin,输出端提供直流输出电压vout。电阻r1和r2组成的分压网络用于得到直流输出电压vout的反馈电压vfb。

33.控制电路包括误差放大器110、比较器120、时钟同步电路130和逻辑控制电路140。

34.误差放大器110用于根据反馈电压vfb与参考电压vref1得到误差信号verr,比较器120将电流检测信号isen与误差信号verr进行比较,根据比较结果生成脉宽调制信号pwm,逻辑控制电路140根据所述脉宽调制信号pwm和时钟同步电路130提供的时钟信号clk生成开关驱动信号,控制开关管md1和md2的导通和关断。其中,时钟信号clk用于控制开关管md1和md2的开关频率,继而控制整个开关变换器的工作频率。

35.本领域技术人员应该理解,逻辑控制电路140可以通过不同的架构来实现。同时,同步整流的降压型开关变换器100的控制原理应该是本领域技术人员所熟知的。

36.上述实施例中的开关管md1和md2可以是各种晶体管,例如npn达林顿管、npn型双极性晶体管、pnp型双极性晶体管、以及n型mosfet和p型mosfet等。控制电路例如封装成芯片ic。在一些实施例中,主电路中的开关管md1和md2也封装在芯片ic中。

37.图2示出根据本发明第二实施例的一种开关变换器的时钟同步电路的结构示意图。如图2所示,时钟同步电路130包括输入引脚101、内部时钟控制电路131、锁相环电路132

和信号检测电路133。输入引脚101一方面与外接电阻rset连接,另一方面通过开关k1与外部时钟信号连接,内部时钟控制电路131、锁相环电路132以及信号检测电路133与所述输入引脚101连接。通过外部配置可以使得时钟同步电路130工作在内部频率模式或者同步频率模式下,例如,当开关k1关断时,时钟同步电路130工作在内部频率模式下,可根据外接电阻rset的电阻值调节输出的时钟信号clk的频率;当开关k1导通时,时钟同步电路130工作在同步频率模式下,时钟同步电路130输出的时钟信号clk的频率与外部时钟信号的频率同步。

38.进一步的,内部时钟控制电路131用于在内部频率模式下根据输入引脚101的外接电阻rset的电阻值生成对应的第一控制电压vctr1。

39.锁相环电路132用于在同步频率模式下根据输入引脚101的外部时钟信号生成对应的第二控制电压(图中未示出)。进一步的,锁相环电路132包括压控振荡器(图中未示出),所述压控振荡器用于在内部频率模式下根据所述第一控制电压vctr1产生与内部时钟信号频率同步的时钟信号作为所述开关变换器的工作时钟,或者在同步频率模式下根据所述第二控制电压产生与外部时钟信号频率同步的时钟信号作为所述开关变换器的工作时钟。

40.信号检测电路133通过检测输入引脚101是否存在外部时钟信号来控制时钟同步电路130工作于内部频率模式或者同步频率模式。进一步的,信号检测电路133根据输入引脚101是否存在外部时钟信号分别向内部时钟控制电路131和锁相环电路132提供第一模式信号mode1和第二模式信号mode2,第一模式信号mode1和第二模式信号mode2分别用于控制内部时钟控制电路131和锁相环电路132的工作状态。示例的,在输入引脚存在外部时钟信号的情况下,信号检测电路133输出有效的(例如“高电平的”)第二模式信号mode2和无效的(例如“低电平的”)第一模式信号mode1,以使能锁相环电路132,关闭内部时钟控制电路131,控制时钟同步电路130工作在同步频率模式下。在输入引脚不存在外部时钟信号的情况下,信号检测电路133输出有效的(例如“高电平的”)第一模式信号mode1和无效的(例如“低电平的”)第二模式信号mode2,以使能内部时钟控制电路131,关闭锁相环电路132中的部分电路,控制时钟同步电路130工作在内部频率模式下。

41.图3示出根据本发明第二实施例的时钟同步电路的示意性电路图。如图3所示,内部时钟控制电路131包括晶体管mp1和mp2、晶体管mn1、运算跨导放大器ota1和ota2、电阻r3以及开关k2。

42.晶体管mp1和mn1依次连接于电源电压vdd和外接电阻rset的第一端之间,晶体管mp2的第一端与电源电压vdd连接,第二端与电阻r3的第一端连接,电阻r3的第二端接地。

43.运算跨导放大器ota1的同相输入端用于接收参考电压vref2,反相输入端与晶体管mn1和外接电阻rset之间的节点a连接,运算跨导放大器ota1用于根据所述节点a的节点电压控制所述晶体管mn1的导通电阻,以控制流经晶体管mp1和mn1的电流。

44.晶体管mp2与晶体管mp1构成电流镜,从而以镜像的方式获得与外接电阻rset对应的输出电流,晶体管mp2的第二端的输出电流通过以下公式得到:

[0045][0046]

其中,iset表示晶体管mp2第二端的输出电流,rset表示外接电阻rset的电阻值,

因此通过调节外接电阻rset的电阻值即可调节所述输出电流的电流值。

[0047]

电阻r3和运算跨导放大器ota2将所述输出电流转换为对应的电压信号,从而得到所述第一控制电压vctr1。结合上式可以得到第一控制电压vctr1的电压值为:

[0048][0049]

其中,vb表示电阻r3与晶体管mp2之间的节点b的电压,m表示晶体管mp2和mp1之间的宽长比的比值,r3表示电阻r3的电阻值。

[0050]

开关k2连接于运算跨导放大器ota2的输出端和锁相环电路132中的压控振荡器1325之间,信号检测电路133通过控制开关k2的导通和关断来控制运算跨导放大器ota2与压控振荡器1324之间的通路的通断。

[0051]

例如,当时钟同步电路130工作于内部频率模式下时,信号检测电路133输出高电平的第一模式信号mode1,开关k2导通,压控振荡器1325根据接收的第一控制电压vctr1产生与内部时钟信号频率同步的时钟信号clk作为开关变换器的工作时钟,当时钟同步电路130工作于同步频率模式下时,信号检测电路133输出低电平的第一模式信号mode1,开关k2关断。

[0052]

锁相环电路132还包括史密斯触发器1321、鉴频鉴相器1322、电荷泵1323、环路滤波器1324、分频器1326和开关k3。

[0053]

史密斯触发器1321的输入端与输入引脚连接,用于根据外部时钟信号生成时钟参考信号clk-ref。

[0054]

鉴频鉴相器1322的一个输入端接收所述时钟参考信号clk-ref,另一个输入端接收内部的时钟反馈信号clk-fb,所述鉴频鉴相器1322用于检测时钟参考信号clk-ref和时钟反馈信号clk-fb之间的相位差和频率差,输出正比于该相位差的电压信号,所述鉴频鉴相器1322输出的电压信号为脉冲控制信号up和down。

[0055]

电荷泵1323与鉴频鉴相器1322的输出端连接,用于将所述电压信号转换成电流信号。

[0056]

环路滤波器1324的输入端通过开关k3与电荷泵1323的输出端连接,用于在开关k3导通时滤除所述电流信号中的高频分量,从而生成第二控制电压vctr2,第二控制电压vctr2用于调节压控振荡器1325的输出频率,以使得压控振荡器1325生成与外部时钟信号频率同步的时钟信号clk作为开关变换器的工作时钟。

[0057]

进一步的,信号检测电路133通过控制开关k3的导通和关断来控制电荷泵1323和环路滤波器1324之间通路的通断。例如,当时钟同步电路130工作于同步频率模式下时,信号检测电路133输出高电平的第二模式信号mode2,开关k3导通,以接通电荷泵1323和环路滤波器1324之间的通路,当时钟同步电路130工作于内部频率模式下时,信号检测电路133输出低电平的第二模式信号mode2,开关k3关断,以断开电荷泵1323和环路滤波器1324之间的通路。

[0058]

分频器1326的输入端与压控振荡器1325的输出端连接,分频器1326的输出端与鉴频鉴相器1322的输入端连接,分频器1326用于对压控振荡器1325输出的时钟信号clk进行分频以输出内部的时钟反馈信号clk-fb,并将该时钟反馈信号clk-fb发送至鉴频鉴相器1322。进一步的,分频器1326例如通过n分频器实现。

[0059]

本发明实施例的时钟同步电路130的工作原理是:信号检测电路133判断输入引脚是否存在外部时钟信号,如果信号检测电路133没有检测到外部时钟信号,则输出第一模式信号mode1为高电平,输出第二模式信号mode2为低电平,开关k2导通,开关k3关断,内部时钟控制电路131根据输入引脚的外接电阻rset的电阻值输出对应的第一控制电压vctr1,压控振荡器1325根据第一控制电压vctr1调节其自身的输出频率,从而输出与内部时钟频率同步的时钟信号clk。如果信号检测电路133在输入引脚检测到外部时钟信号(例如外部时钟信号的上升沿),则输出第一模式信号mode1为低电平,输出第二模式信号mode2为高电平,开关k2关断,开关k3导通,同时鉴频鉴相器1322根据第二模式信号mode2使能开启,锁相环电路132中的鉴频鉴相器1322、电荷泵1323以及环路滤波器1324根据外部时钟信号得到对应的第二控制电压vctr2,压控振荡电路1325根据第二控制电压vctr2调节其自身的输出频率,从而输出与外部时钟信号频率同步的时钟信号clk。

[0060]

图4示出根据本发明第二实施例的时钟同步电路中的环路滤波器的示意性电路图。在本实施例中,环路滤波器1324例如通过无源电容电阻网络实现,包括电阻r11以及电容c11和c12。电阻r11的第一端作为环路滤波器1324的输入端in与图3中的开关k3的第二端连接,电阻r11的第二端作为环路滤波器1324的输出端与图3中的开关k2的第二端以及压控振荡器1325的输入端连接,电容c11的第一端与电阻r11的第一端连接,第二端接地,电容c12的第一端与电阻r11的第二端连接,第二端接地。在本实施例中,环路滤波器1324同时与开关k2的第二端连接,以在时钟同步电路130工作于内部频率模式下时用于第一控制电压vctr1的输出补偿,使得环路稳定,可以避免在时钟同步电路130从内部频率模式切换至同步频率模式的过程中开关变换器的工作时钟频率出现较大的波动,实现内部频率模式与同步频率模式之间的平滑切换。

[0061]

图5示出根据本发明第二实施例的时钟同步电路中的压控振荡器的示意性电路图。如图5所示,压控振荡器1325包括压控电流源351、电容c21、开关k4、比较器352以及逻辑单元353。

[0062]

压控电流源351和电容c21依次连接于电源电压vdd和地之间,压控电流源351用于生成与第一控制电压vctr1或者第二控制电压vctr2对应的充电电流。开关k4的第一端与电容c21的第一端连接,第二端接地。比较器352的同相输入端与电容c21的第一端连接以接收斜坡电压vslope,反相输入端用于接收参考电压vref3,比较器352用于比较斜坡电压vslope和参考电压vref3,以输出一比较信号。逻辑单元353的输入端与比较器352的输出端连接,用于根据所述比较信号生成所述时钟信号clk。其中,开关k4的导通和关断受控于所述时钟信号clk,以在开关k4关断期间由压控电流源351对电容c21进行充电,并在开关k4导通期间对电容c21进行放电,从而在电容c21的第一端生成所述斜坡电压vslope。

[0063]

下面结合图3和图5来说明当时钟同步电路130工作于内部频率模式下时,如何通过调节外接电阻rset的电阻值来控制时钟信号clk的频率。当时钟同步电路130工作于内部频率模式下时,压控电流源351提供的充电电流为:

[0064]

ictr=gm

×

vctr1

ꢀꢀꢀ

公式3

[0065]

其中,ictr表示压控电流源351输出的充电电流,vctr1表示第一控制电压,gm表示压控电流源351的跨导系数,其值为:gm=1/r,其中,r为芯片内部电阻。

[0066]

又因为时钟信号clk的频率为:

[0067][0068]

其中,c21表示电容c21的电容值,结合公式2至公式4可以得到时钟信号clk的频率为:

[0069][0070]

在公式5中,参考电压vref2和vref3是芯片内部的基准电压,不随温度和工艺改变,m表示晶体管mp1和晶体管mp2组成的电流镜的比例系数,为常数,r3和r均为芯片内部的电阻,由于采用同一电阻类型,所以r3和r的比值为固定的常数且不随温度或者工艺的变化而变化,所以只需要通过改变rset和c21的值即可得到想要的时钟频率,而电容c21可以选用零温度系数电容,这样就可以使得时钟信号的频率仅与外接电阻rset的电阻值有关。

[0071]

图6a和图6b分别示出了根据本发明第一实施例的开关变换器从内部频率模式切换至同步频率模式和从同步频率模式切换至内部频率模式的工作波形图。在图中,曲线vout、ilx、sw、clk-rt和clk分别表示直流输出电压、开关变换器的电感电流、开关节点的波形变化、输入引脚的外部时钟信号和时钟同步电路输出的时钟信号。从图6a可以看出,在输入引脚接收到外部时钟信号时,开关变换器的开关节点sw的频率平滑切换到与外部时钟信号的频率同步,可以看到电感电流ilx和直流输出电压vout的纹波变化都很平滑且变化幅度很小。从图6b可以看出,在输入引脚一段时间未接收到外部时钟信号时,开关变换器的工作模式从同步频率模式切换至内部频率模式,开关节点sw在短暂波动之后其频率与内部时钟信号的频率同步,在此期间电感电流ilx和直流输出电压vout的纹波变化幅度也很小。

[0072]

综上所述,本发明实施例的开关变换器及其时钟同步电路包括内部时钟控制电路、锁相环电路和信号检测电路,信号检测电路根据输入引脚是否存在外部时钟信号以控制时钟同步电路工作于内部频率模式或者同步频率模式,内部时钟控制电路在内部频率模式下根据输入引脚的外接电阻的电阻值生成对应的第一控制电压,锁相环电路在同步频率模式下根据输入引脚的外部时钟信号生成对应的第二控制电压,其中,锁相环电路包括压控振荡器,用于在内部频率模式下根据第一控制电压产生与内部时钟信号频率同步的时钟信号,或者在同步频率模式下根据第二控制电压生成与外部时钟信号同步的时钟信号,只需要在芯片上设置一个引脚就可以自动识别外部要求的工作模式,同时完成内部时钟频率设置和外部时钟频率同步的功能,配置方式简单,可靠性高,能够满足不同的应用要求。

[0073]

进一步的,本发明实施例的信号检测电路通过检测外部时钟信号的上升沿的方式使能控制内部时钟控制电路和锁相环电路的工作状态,不需要外部时钟信号的频率必须大于电路内部的固定频率也可以正常同步时钟,提高了外部时钟信号的频率变化范围,解决了开关变换器的工作频率受到限制的问题。

[0074]

进一步的,锁相环电路还包括环路滤波器,该环路滤波器还用于在内部频率模式下对内部时钟控制电路生成的第一控制电压进行输出补偿,提高了环路稳定性,解决了从内部时钟切换到外部时钟时芯片的频率会发生突变的问题,继而降低了开关变换器在切换瞬间的输出电压纹波,提高了系统的稳定性和可靠性。

[0075]

在上述的实施例中,尽管结合图1描述了降压型拓扑结构的开关变换器,然而,可以理解,本发明实施例的振荡器100也可以用于其他拓扑结构的开关变换器中,包括但不限

于降压型、升压型、升降压型、正激型、反激型等拓扑结构。

[0076]

应当说明的是,在本文中,诸如第一和第二等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括所述要素的过程、方法、物品或者设备中还存在另外的相同要素。

[0077]

依照本发明的实施例如上文所述,这些实施例并没有详尽叙述所有的细节,也不限制该发明仅为所述的具体实施例。显然,根据以上描述,可作很多的修改和变化。本说明书选取并具体描述这些实施例,是为了更好地解释本发明的原理和实际应用,从而使所属技术领域技术人员能很好地利用本发明以及在本发明基础上的修改使用。本发明仅受权利要求书及其全部范围和等效物的限制。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。