1.本发明属于编码器检测技术领域,特别是涉及到一种基于可编程逻辑阵列增量编码器脉冲检测电路。

背景技术:

2.增量式编码器是位移转换成周期性的模拟电信号,再将模拟电信号装换成增量式a、b、z脉冲信号,用于反馈相对角度信息或速度信息。其中a为增量式编码器顺时针旋转产生的脉冲信号,b为增量式编码器逆时针旋转产生的脉冲信号,z为零位脉冲信号。

3.现有的增量式检测装置通常是应用微处理器的内部计数器或外部中断判断编码器一个周期的脉冲数量。由于受到微处理器外部中断相应时间的限制,在增量脉冲数量达到十万级以上时,无法捕捉到零位脉冲z或者a、b脉冲信号的跳变边沿变化,导致无法进行计数检测。

4.因此现有技术当中亟需要一种新型的技术方案来解决这一问题。

技术实现要素:

5.本发明所要解决的技术问题是:提供一种基于可编程逻辑阵列增量编码器脉冲检测电路用于解决现有的增量式检测装置无法捕捉到零位脉冲z或者a、b脉冲信号的跳变边沿变化,导致无法进行计数检测的技术问题。

6.一种基于可编程逻辑阵列增量编码器脉冲检测电路,包括光耦接收电路、可编程逻辑阵列、微处理器和lcd显示系统,所述光耦接收电路将接收的被测增量编码器顺时针旋转产生的脉冲信号a、逆时针旋转产生的脉冲信号b和零位脉冲信号z相应转换成3.3v ttl电平信号a0、b0和z0并输入到可编程逻辑阵列;

7.所述可编程逻辑阵列包括两个32位脉冲捕捉计数器、一个32位加法器、四个8位锁存器和逻辑输出电路,可编程逻辑阵列用于实现被测增量编码器顺时针旋转或逆时针旋转的脉冲信号的增减计数和对接收到的零位脉冲信号z清零;所述两个32位脉冲捕捉计数器接收光耦接收电路的输出信号a0、b0和z0,两个32位脉冲捕捉计数器分别用于被测增量编码器顺时针旋转或逆时针旋转的脉冲信号的增减计数;所述32位加法器的输入端分别与两个32位脉冲捕捉计数器的输出端连接,32位加法器用于将两个32位脉冲捕捉计数器的数据合并,32位加法器的输出端分别与四个8位锁存器的输入端连接;所述四个8位锁存器还连接可编程逻辑阵列的零位脉冲信号z的清零输出端,四个8位锁存器用于在采集到零位脉冲信号z输入条件下,同步锁存32位加法器的当前计数数据;所述逻辑输出电路的输入端分别与四个8位锁存器的输出端以及光耦接收电路的输出信号a0、b0、z0连接,逻辑输出电路将四个8位锁存器的32位输出信号拆分成4个8位的分时读取输出接口电路;微处理器分别与逻辑输出电路的输出端以及lcd显示系统电性连接。

8.所述8位锁存器采用74373三态缓冲输出的8位锁存器。

9.所述逻辑输出电路中还采用译码器74138。

10.通过上述设计方案,本发明可以带来如下有益效果:

11.本发明中由于a、b脉冲信号的脉冲计数及零位脉冲信号z锁存和清零功能电路都是由可编程逻辑阵列硬件电路完成,通过高速的硬件电路取代mcu程序低速检测算法真正实现了高速脉冲计数的检测,可广泛应用于高脉冲,高精度,高转速的增量编码器的脉冲检测领域,为研制更高细分倍率的增量编码器提供标准测量及验证。

附图说明

12.以下结合附图和具体实施方式对本发明作进一步的说明:

13.图1为现有技术中增量式检测装置的结构框图。

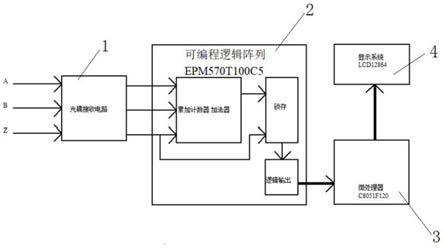

14.图2为本发明一种基于可编程逻辑阵列增量编码器脉冲检测电路的结构框图。

15.图3为本发明一种基于可编程逻辑阵列增量编码器脉冲检测电路中光耦接收电路的电路图。

16.图4为本发明一种基于可编程逻辑阵列增量编码器脉冲检测电路中两个32位脉冲捕捉计数器与32位加法器的电路连接原理图。

17.图5为本发明一种基于可编程逻辑阵列增量编码器脉冲检测电路中四个8位锁存器的电路连接原理图。

18.图6为本发明一种基于可编程逻辑阵列增量编码器脉冲检测电路中逻辑输出电路的连接原理图。

19.图7为本发明一种基于可编程逻辑阵列增量编码器脉冲检测电路中微处理器的电路连接原理图。

20.图8为本发明一种基于可编程逻辑阵列增量编码器脉冲检测电路中lcd显示系统的电路连接原理图。

21.图中1-光耦接收电路、2-可编程逻辑阵列、3-微处理器、4-lcd显示系统、5-四个8位锁存器的电路、6-逻辑输出电路。

具体实施方式

22.如图所示,一种基于可编程逻辑阵列增量编码器脉冲检测电路,包括光耦接收电路1、可编程逻辑阵列2、微处理器3和lcd显示系统4,所述光耦接收电路1采用两个tlp2168光电耦合器将接收的被测增量编码器顺时针旋转产生的脉冲信号a、逆时针旋转产生的脉冲信号b和零位脉冲信号z相应转换成3.3vttl电平信号a0、b0和z0并输入到可编程逻辑阵列2;

23.所述可编程逻辑阵列2包括两个32位脉冲捕捉计数器、一个32位加法器、四个8位锁存器和逻辑输出电路6,可编程逻辑阵列2用于实现被测增量编码器顺时针旋转或逆时针旋转的脉冲信号的增减计数和对接收到的零位脉冲信号z清零;所述两个32位脉冲捕捉计数器接收光耦接收电路1的输出信号a0、b0和z0,两个32位脉冲捕捉计数器分别用于被测增量编码器顺时针旋转或逆时针旋转时脉冲信号进行相应的增或减计数;所述32位加法器的输入端分别与两个32位脉冲捕捉计数器的输出端q[31..0]一一对应连接,32位加法器用于将两个32位脉冲捕捉计数器的数据合并,32位加法器的输出端result[31..0]每8个数据为一组进行拆分并依次对应与四个8位锁存器的输入端连接;所述四个8位锁存器还连接可编

程逻辑阵列2的零位脉冲信号z的清零输出端z/,四个8位锁存器用于在采集到零位脉冲信号z输入条件下,同步锁存32位加法器的当前计数数据,四个8位锁存器的电路5如图5所示;所述逻辑输出电路6的输入端分别与四个8位锁存器的输出端以及光耦接收电路1的输出信号a0、b0、z0连接,逻辑输出电路6将四个8位锁存器的32位输出信号拆分成4个8位的分时读取输出接口电路;微处理器3分别与逻辑输出电路6的输出端d0~d7以及lcd显示系统4电性连接。

[0024]

所述8位锁存器采用74373三态缓冲输出的8位锁存器。

[0025]

所述逻辑输出电路6中还采用译码器74138。

[0026]

所述微处理器3采用c8051f120单片机。

[0027]

按图3所示的电路结构实施,将被测增量编码器顺时针旋转产生的脉冲信号a、逆时针旋转产生的脉冲信号b和零位脉冲信号z相应通过光耦接收转换成3.3v ttl电平信号a0、b0以及z0并输入到epm570t100c5可编程逻辑阵列2中。

[0028]

按图4所示电路中应用两个32位脉冲捕捉计数器作为32位上升沿捕获加计数器阵列和减计数器阵列对b0信号进行计数。加计数器阵列:当a0反为高电平时,b0上升沿状态,计数器加1;减计数器阵列:当a0反为高电平时,b0反上升沿状态,计数器减1,实现了被测增量编码器正反转加减计数的功能。当z0高电平有效时,计数器将当前计数值清除为0,并重新计数。然后将两个计数器的计数结果同步输入到32位加法器进行合并数据,并和零位反信号一起输出到四个8位锁存器电路中。

[0029]

如图5所示为数据同步锁存电路,当z0有效时,4个8位锁存器将当前计数数据同步锁存,得到两个零位脉冲信号z之间的脉冲总数,也就得到了增量编码器旋转一周的脉冲总数。

[0030]

如图6所示是通过数据逻辑输出电路6将32位数据拆分成4个8位的可分时读取的输出接口电路,减少了外围数据连接接口的数量,便于与单片机等mcu芯片连接,节省资源。

[0031]

如图7和图8所示,单片机与lcd12864组成显示电路,是将可编程逻辑阵列的脉冲计数数据读取并驱动和显示到lcd12864液晶屏,从而得到直观的脉冲检测数据。

[0032]

在整体电路中,图3到图8中标有相同标记的连接节点电性连接在一起。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。