半导体封装

1.相关申请的交叉引用

2.本技术要求2020年11月10日向韩国知识产权局递交的韩国专利申请no.10-2020-0149330的优先权,其公开内容通过引用其全部内容结合于此。

技术领域

3.本公开涉及半导体封装。

背景技术:

4.一种典型的堆叠封装具有堆叠多个基板的结构。例如,堆叠封装可以包括顺序堆叠在印刷电路板(pcb)上的半导体芯片。连接焊盘形成在半导体芯片上。接合线可用于连接连接焊盘,使得半导体芯片可以彼此电耦接。印刷电路板上设置有控制半导体芯片的逻辑芯片。

5.在近来的电子产品市场中,对便携式设备的需求日益增加,因此,对减小安装在便携式设备上的电子部件的尺寸和重量的需求增加。为了实现电子部件尺寸和重量的减小,需要将多个单独设备集成到单个封装中的技术以及减小安装部件的各个尺寸的技术。特别是,在高频信号下工作的半导体封装可能需要具有紧凑性和优良的电气特性。

技术实现要素:

6.本发明构思的一些实施例提供具有改进的结构稳定性的半导体封装。

7.根据本发明构思的一些实施例,半导体封装可以包括:位于基板上的第一半导体芯片;位于基板与第一半导体芯片之间的第二半导体芯片;以及位于基板与第一半导体芯片之间且与第二半导体芯片间隔开的间隔物。基板可以包括位于第二半导体芯片和间隔物之间的第一基板焊盘。第二半导体芯片可以包括在所述第二半导体芯片的顶面上的芯片焊盘和从所述芯片焊盘向第一基板焊盘延伸的信号线。间隔物可以包括位于间隔物的顶面上的第一虚拟焊盘和耦接到第一虚拟焊盘的第一虚拟线。第一虚拟焊盘可以在第二半导体芯片附近。第一半导体芯片可以通过所述第一半导体芯片的底面上的粘合层附着到第二半导体芯片的顶面和所述间隔物的顶面。信号线的一部分和第一虚拟线的一部分可以位于粘合层中。

8.根据本发明构思的一些实施例,一种半导体封装可以包括:基板,包括在第一方向上彼此对齐的多个第一基板焊盘;第一半导体芯片,位于所述基板上;间隔物,位于所述基板上且跨越所述多个第一基板焊盘在第二方向上与第一半导体芯片间隔开,所述第二方向与所述第一方向相交;第二半导体芯片,通过粘合层附着到第一半导体芯片的顶面和所述间隔物的顶面;多条信号线,分别从第一半导体芯片的顶面朝所述多个第一基板焊盘延伸;多个第一接合部,位于所述间隔物的顶面上的相应虚拟焊盘上;以及模塑层,位于第一半导体芯片、所述间隔物和第二半导体芯片上,该模塑层位于第一半导体芯片和所述间隔物之间的空间中。虚拟焊盘可以在间隔物的第一侧表面附近沿第一方向彼此对齐。第一侧表面

可以在第一半导体芯片附近。

9.根据本发明构思的一些实施例,一种半导体封装可以包括:第一半导体芯片和间隔物,其在基板上彼此间隔开;以及第二半导体芯片,通过粘合层附着到第一半导体芯片和间隔物。第一半导体芯片可以包括多条信号线,该多条信号线从第一半导体芯片的顶面延伸并穿过第一半导体芯片与所述间隔物之间的空间以连接至所述基板。间隔物可以包括连接至间隔物的顶面的多条虚拟线。多条信号线可以在第一半导体芯片的第一侧表面附近彼此对齐。第一半导体芯片的第一侧表面可以面向间隔物。多条虚拟线可以在间隔物的第二侧表面附近彼此对齐。间隔物的第二侧表面可以面向第一半导体芯片。粘合层可以与第一半导体芯片的顶面和间隔物的顶面接触。在第一半导体芯片和间隔物之间,粘合层可以与第一半导体芯片的第一侧表面和间隔物的第二侧表面间隔开。

附图说明

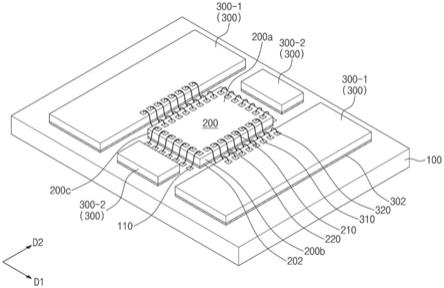

10.图1是根据本发明构思的一些实施例的半导体封装的透视图。

11.图2和图3是示出了根据本发明构思的一些实施例的半导体封装的截面图。

12.图4是示出了根据本发明构思的一些实施例的半导体封装的平面图。

13.图5至图7是示出了根据本发明构思的一些实施例的半导体封装的放大截面图。

14.图8是示出了根据本发明构思的一些实施例的半导体封装的平面图。

15.图9是示出了根据本发明构思的一些实施例的半导体封装的图8的放大截面图。

16.图10是示出了根据本发明构思的一些实施例的半导体封装的平面图。

17.图11是示出了根据本发明构思的一些实施例的半导体封装的图10的放大截面图。

18.图12是示出了根据本发明构思的一些实施例的半导体封装的平面图。

19.图13是示出了根据本发明构思的一些实施例的半导体封装的图12的截面图。

20.图14至图20是示出了根据本发明构思的一些实施例的制造半导体封装的方法的截面图。

21.图21是示出了根据本发明构思的一些实施例的制造半导体封装的方法的平面图。

22.图22是示出了根据本发明构思的一些实施例的制造半导体封装的方法的截面图。

23.图23是示出了根据本发明构思的一些实施例的制造半导体封装的方法的平面图。

具体实施方式

24.现在将在下文参照附图描述根据本发明构思的半导体封装。

25.图1是示出了根据本发明构思的一些实施例的半导体封装的透视图,并且为了便于描述省略了一些组件。图2和图3是示出了根据本发明构思的一些实施例的半导体封装的截面图。图4是示出了根据本发明构思的一些实施例的半导体封装的平面图。图2对应于沿图4的a-a’线截取的截面,图3对应于沿图4的b-b’线截取的截面。图5至图7是示出了根据本发明构思的一些实施例的半导体封装的图2中描绘的a部分的放大截面图。

26.参照图1至图4,半导体封装可以包括基板100、第一半导体芯片200和基板100上的间隔物300、第一半导体芯片200和间隔物300上的芯片堆叠cs、以及覆盖芯片堆叠cs的模塑层500。

27.基板100可以是在其顶面上设置有信号图案的印刷电路板(pcb)。基板100可以具

有交替堆叠一层或多层介电层和一层或多层布线层的结构。信号图案可以包括第一基板焊盘110和第二基板焊盘120。第一基板焊盘110可以是与将要讨论的第一半导体芯片200的多条信号线耦接的焊盘,并且第二基板焊盘120可以是与将要讨论的芯片堆叠cs的多条信号线耦接的焊盘。基板100可以具有设置在其底面上的外部端子105。外部端子105可以包括焊球或焊盘,并且基于外部端子105的类型,半导体封装可以包括球栅阵列(bga)类型、精细球栅阵列(fbga)类型和接点栅格阵列(lga)类型中的一种。

28.芯片堆叠cs可以设置在基板100上。芯片堆叠cs可以包括堆叠在基板100上的第二半导体芯片400。第二半导体芯片400可以是存储器芯片。第二半导体芯片400可以布置为偏移堆叠结构。例如,第二半导体芯片400可以在第一方向d1上倾斜地堆叠,从而可以导致上升的台阶形状。第二半导体芯片400可以通过芯片堆叠信号线415彼此相连。粘合层420可以设置在第二半导体芯片400之间。第二半导体芯片400可以通过设置在上第二半导体芯片400的底面上的粘合层420附着到其下第二半导体芯片400的顶面。最下面的第二半导体芯片400’可以经过(即,通过)设置在其底面上的粘合层420’附着到第一半导体芯片200的顶面200a和间隔物件300的顶面。由于第二半导体芯片400是台阶式堆叠的,所以第二半导体芯片400的顶面可以被部分地暴露(即,每个第二半导体芯片400上的一部分可以不具有另一个第二半导体芯片400)。顶面可以是第二半导体芯片400的有源表面。例如,第二半导体芯片400的暴露的顶面上可以设置有与芯片堆叠信号线415接触的芯片堆叠焊盘410。

29.第二半导体芯片400可以通过芯片堆叠信号线415引线接合到基板100。芯片堆叠信号线415可以将第二半导体芯片400上的芯片堆叠焊盘410电连接至基板100的第二基板焊盘120。芯片堆叠信号线415可以从芯片堆叠cs沿与第一方向d1相反的方向布置。

30.第一半导体芯片200可以设置在基板100上。第一半导体芯片200可以设置在基板100和芯片堆叠cs之间。当在平面图中观察时,第一半导体芯片200可以设置在最下面的第二半导体芯片400

′

的中央部分下方。例如,第一半导体芯片200可以被布置为与最下面的第二半导体芯片400

′

的侧表面间隔开。第一半导体芯片200可以是诸如控制第二半导体芯片400的控制器的逻辑芯片。顶面200a可以是第一半导体芯片200的有源表面。第一半导体芯片200可以通过第一粘合层202附着到基板100的顶面。

31.第一半导体芯片200可以具有设置在其顶面200a上的芯片焊盘210。芯片焊盘210可以在第一半导体芯片200的侧表面附近对齐。例如,第一半导体芯片200可以在第一方向d1上具有第一侧表面200b,并且第一侧表面200b附近的芯片焊盘210可以布置在与第一方向d1相交的第二方向d2上。第一半导体芯片200可以在第二方向d2上具有第二侧表面200c,并且第二侧表面200c附近的芯片焊盘210可以布置在第一方向d1上。芯片焊盘210可以围绕第一半导体芯片200的顶面200a(例如,在顶面200a上限定周边),同时以有规则的间隔彼此隔开。相邻芯片焊盘210之间的间隔可以在从约50微米(μm)到约100μm的范围内。芯片焊盘210可以是耦接到第一半导体芯片200的集成电路并将电信号传输到第一半导体芯片200的信号焊盘。

32.第一半导体芯片200可以通过信号线220引线接合到基板100。信号线220可以将第一半导体芯片200上的芯片焊盘210电连接至基板100的第一基板焊盘110。第一基板焊盘110可以设置为在第一半导体芯片200附近。例如,当在平面图中观察时,第一基板焊盘110可以被布置为围绕第一半导体芯片200。第一基板焊盘110中在第一半导体芯片200的第一

侧表面200b附近的一些焊盘可以布置在第二方向d2上,并且第一基板焊盘110中在第一半导体芯片200的第二侧表面200c附近的一些焊盘可以布置在第一方向d1上。第一半导体芯片200可以通过第一基板焊盘110和信号线220电连接至基板100。

33.每条信号线220可以将一个芯片焊盘210连接至一个第一基板焊盘110。以下描述将基于一根信号线220。如图5所示,信号线220可以缝焊或球焊到芯片焊盘210和第一基板焊盘110。例如,信号线220可以包括附着到芯片焊盘210的第一接合部222、附着到第一基板焊盘110的第二接合部224以及将第一接合部222连接至第二接合部224的第一环线226。第一接合部222和第二接合部224可以均具有球形或折叠形状。第一接合部222和第二接合部224各自的宽度可以大于第一环线226的宽度。信号线220之间的间隔可以在从约50μm到约100μm的范围内。

34.仍然参照图1至图5,间隔物300可以设置在基板100上。间隔物300可以设置在基板100和芯片堆叠cs之间。间隔物300可以被布置为与第一半导体芯片200间隔开。在基板100上,间隔物300可以支撑芯片堆叠cs。间隔物300可以通过第二粘合层302附着到基板100。

35.第一半导体芯片200可以设置在最下面的第二半导体芯片400

′

的中心部分下方,并且间隔物300可以被布置为围绕第一半导体芯片200(例如,限定第一半导体芯片200的周长)。例如,一个间隔物300之一可以布置在第一半导体芯片200的第一侧表面200b附近,而其他间隔物300可以布置在第一半导体芯片200的第二侧表面200c附近。间隔物300可以布置在最下面的第二半导体芯片400

′

的拐角下方。因此,芯片堆叠cs的重量可以均匀地分布在间隔物300上,并且芯片堆叠cs可以被均匀地支撑。此外,由于间隔物300被布置为围绕第一半导体芯片200,因此可以防止/抑制芯片堆叠cs的重量集中在第一半导体芯片200上,并且可以保护第一半导体芯片200免受外部冲击。

36.当在平面图中观察时,第一半导体芯片200和间隔物300之间的间隙可以具有网格形状。例如,第一半导体芯片200和间隔物300之间的间隙可以具有在第一方向d1上延伸的第一线区lr1和在第二方向d2上延伸的第二线区lr2。第一半导体芯片200与一个间隔物300-1(以下称为第一间隔物)之间的间隙可以窄于间隔物300之间的间隙或第一半导体芯片200与另一间隔物300-2(以下称为第二间隔物)之间的间隙。为了描述方便,第二线区lr2被定义为指代相对较窄的间隙,而第一线区lr1被定义为指相对较宽的间隙。可以给出约500μm至约1,000μm的范围作为跨越第二线区lr2彼此相对的第一半导体芯片200和第一间隔物300-1之间的间隔。跨越第一线区lr1彼此相对的第一半导体芯片200和第二间隔物300-2之间的间隔可以大于第一半导体芯片200和第一间隔物300-1之间的间隔,并且可以给出约500μm至约1,000μm的范围作为第一半导体芯片200和第二间隔物300-2之间的间隔。

37.第一基板焊盘110可以位于第一线区lr1和第二线区lr2中。例如,第一基板焊盘110可以设置在第一半导体芯片200和第一间隔物300-1之间以及第一半导体芯片200和第二间隔物300-2之间。

38.第一虚拟焊盘310可以设置在间隔物300的第一间隔物300-1上。例如,第一虚拟焊盘310可以跨越第二线区lr2设置在第一半导体芯片200附近的第一间隔物300-1的顶面上。第一虚拟焊盘310可以在第一间隔物300-1的侧表面附近(例如,靠近并平行于)彼此对齐。例如,第一间隔物300-1可以具有面对第一半导体芯片200的第三侧表面300-1a,并且第三侧表面300-1a附近的第一虚拟焊盘310可以布置在第二方向d2上。可以给出约50μm到约100

μm的范围作为相邻的第一虚拟焊盘310之间的间隔。第一虚拟焊盘310可以是与第一间隔物300-1电绝缘并且与第一间隔物300-1没有电信号通信的虚拟(例如,绝缘)焊盘。

39.第一虚拟焊盘310可以通过第一虚拟线320引线接合到基板100。第一虚拟线320可以耦接到第一间隔物300-1的第一虚拟焊盘310和基板100的第一基板焊盘110。在这种情况下,一个第一基板焊盘110可以同时耦接到一个信号线220和一个第一虚拟线320。由于第一虚拟焊盘310与第一间隔物300-1电绝缘,因此即使第一虚拟线320之一与信号线220之一共用一个第一基板焊盘110,也不会在第一半导体芯片200和第一间隔物300-1之间建立电连接,并且不会从第一半导体芯片200向外泄漏电信号。

40.第一虚拟线320中的每一个可以将一个第一虚拟焊盘310连接到一个第一基板焊盘110。以下示例基于一个第一虚拟线320。如图5所示,第一虚拟线320可以缝焊或球焊到第一虚拟焊盘310和第一基板焊盘110。例如,第一虚拟线320可以包括附着到第一虚拟焊盘310的第三接合部322、附着到第一基板焊盘110的第四接合部324以及将第三接合部322连接至第四接合部324的第二环线326。第三接合部322和第四接合部324可以均具有球形或折叠形状。第三接合部322和第四接合部324各自的宽度可以大于第二环线326的宽度。第一虚拟线320之间的间隔可以在从约50μm到约100μn的范围内。

41.图5描绘了一个第一基板焊盘110由第一虚拟线320之一和信号线220之一共享,但是本发明构思不限于此。如图6所示,基板100的信号图案可以包括第一基板焊盘110和第二基板焊盘120,并且还可以包括第三基板焊盘130。第三基板焊盘130可以是与第一虚拟线320耦接的焊盘。第三基板焊盘130可以布置在第一间隔物300-1附近。例如,在第一半导体芯片200和第一间隔物300-1之间,第一基板焊盘110可以布置在第一半导体芯片200的第一侧表面200b附近,并且第三基板焊盘130可以布置在第一间隔物300-1的第三侧表面300-1a附近,该第三侧表面300-1a面向第一半导体芯片200。第三基板焊盘130可以布置在第二方向d2上。第三基板焊盘130可以在第一方向d1上与第一基板焊盘110间隔开。

42.第一虚拟线320中的每一个可以将一个第一虚拟焊盘310连接到一个第三基板焊盘130。如图6所示,第一虚拟线320可以缝焊或球焊到第一虚拟焊盘310和第三基板焊盘130。例如,第一虚拟线320可以包括附着到第一虚拟焊盘310的第三接合部322、附着到第三基板焊盘130的第四接合部324以及将第三接合部322连接至第四接合部324的第二环线326。下面将重点介绍图5的实施例。

43.再次参照图1至图5,信号线220和第一虚拟线320可以具有位于最下面的第二半导体芯片400

′

的粘合层420

′

中的相应部分。例如,最下面的第二半导体芯片400

′

的粘合层420

′

可以与第一半导体芯片200的顶面200a和间隔物300的顶面接触,在这种情况下,芯片焊盘210和第一虚拟焊盘310可以掩埋在粘合层420

′

中。粘合层420’中可以具有耦接到芯片焊盘210的信号线220的第一接合部222和从第一接合部222延伸的第一环线226的部分。粘合层420’中也可以具有耦接到第一虚拟焊盘310的第一虚拟线320的第三接合部322和从第三接合部322延伸的第二环线326的部分。此外,第一半导体芯片200的第一侧表面200b和第一间隔物300-1的第三侧表面300-1a可以各自与粘合层420’间隔开(例如,完全不接触)。

44.在第一半导体芯片200和第一间隔物300-1之间,或者在第二线区lr2上,粘合层420’可以具有底面,该底面与第一半导体芯片200的顶面200a具有交界面(例如,在同一水平面上)。备选地,如图7所示,粘合层420’可以具有在第一半导体芯片200和第一间隔物

300-1之间突出的部分422(以下称为第一突出部)。粘合层420

′

的第一突出部422的最低端/点422a的高度可以高于基板100的顶面和第一半导体芯片200的顶面200a之间的中间(例如,中途)点。根据本发明构思,由于具有小宽度的第二线区lr2上设置有在第一半导体芯片200和第一间隔物300-1之间不突出或仅略微突出的粘合层420

′

,所以在半导体封装的后续制造工艺中模塑层500可以容易地引入到第一半导体芯片200和第一间隔物300-1之间的空间中。这将在下面与制造半导体封装的方法一起详细讨论。

45.在第一半导体芯片200和第二间隔物300-2之间以及在第一间隔物300-1和第二间隔物300-2之间,或者在第一线区lr1和第三线区lr3上,粘合层420

′

的底面的高度可以低于第一半导体芯片200的顶面200a。如图3所示,粘合层420

′

可以具有在第一间隔物300-1和第二间隔物300-2之间突出的部分424(以下称为第二突出部)。

46.再次参照图1至图5,可以设置模塑层500以覆盖芯片堆叠cs和基板100的顶面。模塑层500的一部分510可以填充第一半导体芯片200和间隔物300之间的间隙。例如,在制作半导体封装时,可以在第一半导体芯片200与间隔物300之间的间隙、或第一线区lr1、第二线区lr2和第三线区lr3中引入介电聚合物材料,从而形成模塑层500。例如,第一半导体芯片200和间隔物300之间的间隙可以所用于引入聚合物材料的流动路径。在第二线区lr2上,模塑层500的部分510可以填充第一半导体芯片200和第一间隔物300-1之间的空间,并且可以接触粘合层420

′

的第一突出部422的底面。在第一线区lr1上,模塑层500的部分510可以填充第一半导体芯片200和第二间隔物300-2之间的空间,并且可以接触粘合层420

′

的第二突出部424的底面。模塑层500的一部分可以围绕第一半导体芯片200。模塑层500可以包括介电聚合材料,例如环氧模塑化合物(emc)。

47.根据本发明构思的一些实施例,模塑层500的部分510可以围绕第一半导体芯片200,并且可以完全填充第一半导体芯片200和间隔物300之间的空间。因此,模塑层500可以保护第一半导体芯片200,并且可以提供具有增加的结构稳定性的半导体封装。

48.可以如上所述提供半导体封装。

49.图8是示出了根据本发明构思的一些实施例的半导体封装的截面图。图9是示出了根据本发明构思的一些实施例的半导体封装的图8的放大截面图。在下面的实施例中,为了便于描述,与参照图1和图7讨论的那些相同的部件被分配相同的附图标记,并且将省略或删减对其的重复解释。

50.参照图8和图9,第一虚拟线320可以耦接到彼此相邻的第一虚拟焊盘310。例如,第一虚拟线320可以包括耦接到第一虚拟焊盘310的第三接合部322和将相邻的第三接合部322彼此相连的第二环线326。例如,相邻的第一虚拟焊盘310可以通过第一虚拟线320彼此相连。

51.图10是示出了根据本发明构思的一些实施例的半导体封装的平面图。图11是示出了根据本发明构思的一些实施例的半导体封装的图10的放大截面图。在下面的实施例中,为了便于描述,与参照图1和图7讨论的那些相同的部件被分配相同的附图标记,并且将省略或删减对其的重复解释。

52.参照图10和图11,第一虚拟线320可以耦接到第一虚拟焊盘310,但不耦接到第一基板焊盘110。例如,第一虚拟线320可以包括耦接到第一虚拟焊盘310的第三接合部322和从第三接合部322延伸的第二环线326

′

。在这种情况下,第二环线326

′

可以不延伸到第一基

板焊盘110上。第二环线326

′

的一端可连接至第三接合部322,另一端位于粘合层420

′

中。第二环线326

′

可以是在第一虚拟线320的引线接合工艺中形成的线的一部分,或者是在第一虚拟线320的缝合工艺中形成的第三接合部322的尾段。例如,第二环线326

′

可以是第三接合部322的一部分,该部分可以从第三接合部322突出。

53.图12是示出了根据本发明构思的一些实施例的半导体封装的平面图。图13是沿示出了根据本发明构思的一些实施例的半导体封装的沿图12的线c-c’截取的截面图。

54.参照图12和图13,第一半导体芯片200的顶面200a处的区域可以没有芯片焊盘210。例如,第一半导体芯片200的顶面200a上可以设置第一焊盘区域pr1和第二焊盘区域pr2,第一焊盘区域pr1与第一间隔物300-1相邻且其上布置有芯片焊盘210,而第二焊盘区域pr2上不布置芯片焊盘210。第一焊盘区域pr1和第二焊盘区域pr2可以在第一半导体芯片200的第一侧表面200b附近对齐,并且可以在第二方向d2上彼此间隔开。

55.备选地,在第一半导体芯片200的顶面200a上,在第一侧表面200b附近的区域可以不设置芯片焊盘210。如图12的第一半导体芯片200的左侧所示,在第一半导体芯片200的顶面200a上,可以仅在第一侧表面200b附近的区域上设置第二焊盘区域pr2,并且芯片焊盘210可以不设置在第二焊盘区域pr2上。

56.芯片焊盘210中的一个可以设置在第一焊盘区域pr1上。第二焊盘区域pr2在第二方向d2上的长度可以是相邻芯片焊盘210之间的间隔的至少两倍。

57.芯片焊盘210中的一个可以设置在第一焊盘区域pr1上。芯片焊盘210可以在第一焊盘区域pr1上沿第二方向d2对齐。芯片焊盘210之间的间隔可以在从约50μm到约100μm的范围内。

58.第二虚拟焊盘230可以设置在第二焊盘区域pr2上。第二虚拟焊盘230可以在第二焊盘区域pr2上沿第二方向d2对齐。第二虚拟焊盘230之间的间隔可以在从约50μm到约100μm的范围内。第二虚拟焊盘230可以是与第一半导体芯片200没有电信号通信的虚拟焊盘。可以给出约50μm至约100μm的范围作为彼此相邻布置的芯片焊盘210和第二虚拟焊盘230之间的间隔。

59.设置在第一间隔物300-1上的第一虚拟焊盘310可以在与第一焊盘区域pr1的位置对应的位置上具有第一子虚拟焊盘310-1,并且还可以在与第二焊盘区域pr2的位置对应的位置上具有第二子虚拟焊盘310-2。

60.第一基板焊盘110可以位于第一焊盘区域pr1和第一子虚拟焊鼎310-1之间。基板100还可以包括在第二焊盘区域pr2和第二子虚拟焊盘310-2之间的第四基板焊盘140。第四基板焊盘140可以布置在第二方向d2上。

61.第一半导体芯片200可以通过信号线220引线接合到基板100。信号线220可以将第一焊盘区域pr1上的第一半导体芯片200的芯片焊盘210电连接至基板100的第一基板焊盘110。

62.第一虚拟焊盘310可以通过第一虚拟线320的部分320-1引线接合到基板100。第一虚拟线320的部分320-1可以耦接到第一间隔物300-1的第一子虚拟焊盘310-1和基板100的第一基板焊盘110。

63.芯片焊盘210可以通过信号线220、第一基板焊盘110和第一虚拟线320的部分320-1连接至第一子虚拟焊盘310-1。在这种情况下,第一子虚拟焊盘310-1可以与第一间隔物

300-1电绝缘,因此第一半导体芯片200和第一间隔物300-1可以电浮动。

64.第一半导体芯片200可以通过第二虚拟线240引线接合到基板100。第二虚拟线240可以将第一半导体芯片200的第二焊盘区域pr2上的第二虚拟焊盘230电连接至基板100的第四基板焊盘140。

65.第一虚拟焊盘310可以通过第一虚拟线320的其他部分320-2引线接合到基板100。第一虚拟线320的其他部分320-2可以耦接到第一间隔物300-1的第二子虚拟焊盘310-2和基板100的第四基板焊盘140。

66.第二虚拟焊盘230可以通过第二虚拟线240、第四基板焊盘140和第一虚拟线320的其他部分320-2连接至第二子虚拟焊盘310-2。在这种情况下,第二虚拟(例如,绝缘)焊盘230可以与第一半导体芯片200电绝缘,因此第一半导体芯片200和第一间隔物300-1可以电浮动。

67.根据本发明构思的一些实施例,第二虚拟焊盘230和第二虚拟线240也可以设置在其上设置有芯片焊盘210的第一半导体芯片200的顶面200a上,因此在下文将讨论的封装制造过程中,在穿过芯片焊盘210和第二虚拟焊盘230之后,可以防止/抑制最下面的粘合层420

′

形成在第一半导体芯片200的侧表面上,从而允许第一半导体芯片200和第一间隔物300-1之间具有容纳模塑层500的空间,并且使模塑层500容易进入第一半导体芯片200和第一间隔物300-1之间的空间。这将在下面与制造半导体封装的方法一起详细讨论。

68.图14至图20是示出了根据本发明构思的一些实施例的制造半导体封装的方法的截面图。图21是示出了根据本发明构思的一些实施例的制造半导体封装的方法的平面图。图22是示出了根据本发明构思的一些实施例的制造半导体封装的方法的截面图。

69.参照图4和图14,可以设置芯片基板100。基板100可以是在其顶面上设置有信号图案的印刷电路板(pcb)。基板100可以包括例如第一基板焊盘110和第二基板焊盘120。

70.第一半导体芯片200和间隔物300可以附着到基板100。例如,第一粘合层202可以设置在第一半导体芯片200的无源表面上。第一半导体芯片200可以通过第一粘合层202附着到基板100的顶面。第一半导体芯片200可以附着在基板100的第一基板焊盘110之间。例如,当在平面图中观察时,第一基板焊盘110可以围绕第一半导体芯片200。第一半导体芯片200可以具有顶面或有源表面。例如,第一半导体芯片200可以具有设置在其顶面上的第一芯片焊盘210。可以在每个间隔物300的一个表面上设置第二粘合层302。间隔物300可以各自通过第二粘合层302附着到基板100的顶面。第一虚拟焊盘310可以设置在间隔物300中包括的第一间隔物300-1的顶面上。第一间隔物300-1的顶面上的第一虚拟焊盘310可以布置在第一半导体芯片200附近。第一基板焊盘110中的一个可以位于第一半导体芯片200和第一间隔物300-1之间。

71.参照图4和图15,第一半导体芯片200可以引线接合到基板100。例如,毛细管可以设置在第一半导体芯片200的芯片焊盘210上。毛细管可以熔化引入其中的线以在毛细管的底端形成球。毛细管可以朝向芯片焊盘210行进以将该球附着到芯片焊盘210。附着到芯片焊盘210的球可以对应于参照图5讨论的第一接合部222。毛细管可以移动到第一基板焊盘110上。从毛细管延伸的线可以形成参照图5讨论的第一环线226。毛细管可以在第一环线226的端部形成附着到第一基板焊盘110的球。附着到第一基板焊盘110的球可以对应于参照图5讨论的第二接合部224。因此,可以形成信号线220以将芯片焊盘210连接到第一基板

焊盘110。

72.可以在形成信号线220的引线接合工艺中形成第一虚拟线320。例如,当毛细管从第一间隔物300-1的第一虚拟焊盘310向第一基板焊盘110移动时,毛细管可以形成附着到第一虚拟焊盘310和第二环线(参见图5的326)的第三接合部(参见图5的322)、和在第一基板焊盘110上的第四接合部(参见图5的324),该第二环线从第三接合部322向第一基板焊盘110延伸。

73.参照图4和图16,第二半导体芯片400可以设置在第一半导体芯片200和间隔物300上。例如,可以在第二半导体芯片400的无源表面上设置粘合层420。第二半导体芯片400的粘合层420可以与第一半导体芯片200的顶面和间隔物300的顶面接触。粘合层420可以在其中容纳第一半导体芯片200的芯片焊盘210、信号线220的部分、第一间隔物300-1的第一虚拟焊盘310和第一虚拟线320的部分。第二半导体芯片400可以具有顶面或有源表面。例如,第二半导体芯片400可以具有设置在其顶面上的芯片堆叠焊盘410。

74.参照图4和图17,第二半导体芯片400可以经历热压工艺以将第二半导体芯片400附着到第一半导体芯片200的顶面和间隔物300的顶面。例如,可以执行热压工艺以使得粘合层420被热压工艺产生的热量熔化,并且粘合层420完全附着到第一半导体芯片200的顶面和间隔物300的顶面。之后,粘合层420可以被固化以将第二半导体芯片400刚性地附着到第一半导体芯片200和间隔物300。

75.当进行热压工艺时,如图17中箭头所示,熔化的粘合层420可以从第二半导体芯片400和第一半导体芯片200之间以及第二半导体芯片400和间隔物300之间的空间向外排出。

76.根据本发明构思的一些实施例,第一半导体芯片200可以在其顶面上沿着第一半导体芯片200的外围设置芯片焊盘210和信号线220。芯片焊盘210和信号线220可以中断熔化的粘合层420的流动。因此,可以防止/抑制熔化的粘合层420从第一半导体芯片200和第二半导体芯片400之间的空间引入到第一半导体芯片200和第一间隔物300-1之间的空间(或第二线区lr2)中以及第一半导体芯片200和第二间隔物300-2之间的空间(或第一线区lr1)中。

77.根据本发明构思的一些实施例,第一间隔物300-1可以在其顶面上设置第一虚拟焊盘310和第一虚拟线320,这些焊盘310和线320在第一半导体芯片200附近。第一虚拟焊盘310和第一虚拟线320可以中断熔化的粘合层420的流动。因此可以防止/抑制熔化的粘合层420从第一间隔物300-1和第二半导体芯片400之间的空间引入到第一半导体芯片200和第一间隔物300-1之间的空间(或第二线区lr2)中。因此,在第一半导体芯片200和间隔物300之间,可以防止/抑制熔化的粘合层420被引入到具有小宽度的第二线区lr2中。

78.当执行热压工艺时,如图18所示,可以将熔化的粘合层420引入到第一间隔物300-1和第二间隔物300-2之间的空间中。例如,在第二间隔物300-2的顶面上可以既不设置虚拟焊盘也不设置虚拟线。熔化的粘合层420可以从第一间隔物300-1和第二半导体芯片400之间的空间以及从第二间隔物300-2和第二半导体芯片400之间的空间引入到第一间隔物300-1和第二间隔物300-2之间的空间(或第三线区lr3)中。因此,粘合层420可以包括在第一间隔物300-1和第二间隔物300-2之间突出的第二突出部424。

79.参照图4和图19,多个第二半导体芯片400可以堆叠在附着到第一半导体芯片200和间隔物300的第二半导体芯片400’上。例如,可以在第二半导体芯片400的无源表面上设

置粘合层420。第二半导体芯片400的粘合层420可以与最下面的第二半导体芯片400

′

的顶面接触。可以执行上述方式来堆叠多个第二半导体芯片400。第二半导体芯片400可以堆叠为偏移堆叠结构。第二半导体芯片400可以具有相应的顶面或有源表面。因此,第二半导体芯片400可以暴露芯片堆叠焊盘410。

80.之后,可以将第二半导体芯片400引线接合到基板100。芯片堆叠信号线415可以将芯片堆叠焊盘410连接至基板100的第二基板焊盘120。

81.参照图4、图20和图21,可以在基板100上形成模塑层(见图2的500)。例如,模塑构件515可以涂覆在基板100上,覆盖第二半导体芯片400和基板100的顶面。在这种情况下,如图21所示,模塑构件515可以填充第一半导体芯片200和间隔物300之间的空间。例如,如图21中所描绘的箭头所指示的,模塑构件515可以被引入到第一间隔物300-1和第二间隔物300-2之间以及第一半导体芯片200和间隔物300之间的空间中。模塑构件515可以平行于基板100的顶面流动。在具有小宽度的第二线区lr2上,粘合层420

′

可以不在第一半导体芯片200和第一间隔物300-1之间突出,因此模塑构件515的流动阻力可以比粘合层420’在第一半导体芯片200和第一间隔物300-1之间突出时的阻力低。因此,可以容易地引入模塑构件515,并且可以用模塑件515填充第一线区lr1以减少第一半导体芯片200和第一间隔物300-1之间的空隙(例如空气间隙)的发生。在具有大宽度的第一线区lr1上,即使当粘合层420

′

的一部分在第一半导体芯片200和第二间隔物300-2之间突出时,第一线区lr1也可以具有足够的空间以容纳引入其中的模塑构件515。因此,第一线区lr1可以被填充模塑构件515以减少第一半导体芯片200和第二间隔物300-2之间空隙的发生。

82.之后,模塑构件515可以被固化以形成模塑层500。

83.第一半导体芯片200和第一间隔物300-1之间可以具有窄的开放空间。由于这种窄的开放空间(其可能在第一半导体芯片200附近的第一间隔物300-1上既没有设置第一虚拟焊盘310也没有设置第一虚拟线320时出现),导致模塑构件515可能不容易进入第二线区lr2。图23是示出了半导体封装的制造方法的平面图,图22是沿图23的线d-d’截取的截面图。

84.参照图22和23,第一半导体芯片200和间隔物300可以附着到基板100。之后,第一半导体芯片200可以引线接合到基板100。间隔物300上可以既不设置第一虚拟焊盘也不设置第一虚拟线。

85.第二半导体芯片400可以设置在第一半导体芯片200和间隔物300上。第二半导体芯片400可以在其无源表面上设置有粘合层420,并且粘合层420可以与第一半导体芯片200的顶面和间隔物300的顶面接触。

86.第二半导体芯片400可以经历热压工艺以将第二半导体芯片400附着到第一半导体芯片200的顶面和间隔物300的顶面。例如,可以执行热压工艺以使得粘合层420被热压工艺产生的热量熔化,并且粘合层420完全附着到第一半导体芯片200的顶面和间隔物300的顶面。当进行热压工艺时,熔化的粘合层420可以从第二半导体芯片400和第一半导体芯片200之间以及第二半导体芯片400和间隔物300之间的空间向外排出。在第一间隔物300-1的顶面上既没有设置第一虚拟焊盘310也没有设置第一虚拟线320,因此第三突出部426可以由被引入到第一半导体芯片200和第一间隔物300-1之间空间中的熔化的粘合层420形成。被引入的粘合层420可以覆盖第一间隔物300-1的侧表面,并且粘合层420的第三突出部426

可以填充第二线区lr2的一部分。在这种情况下,粘合层420的第三突出部426可能会导致第二线区lr2具有窄的空间。

87.之后,多个第二半导体芯片400可以堆叠在第二半导体芯片400’上,该第二半导体芯片400’附着到第一半导体芯片200和间隔物300。第二半导体芯片400可以引线接合到基板100。

88.可以在基板100上形成模塑层。例如,模塑构件515可以涂覆在基板100上,覆盖第二半导体芯片400和基板100的顶面。模塑构件515可以被引入到第一半导体芯片200和间隔物300之间的空间中。在这种情况下,如图23所示,粘合层420的第三突出部426可以迫使模塑构件515不完全地填充第二线区lr2。例如,第三突出部426可以中断模塑构件515的流动,并且模塑构件515可以不被引入到第二线区lr2中。因此,第一半导体芯片200与第一间隔物300-1之间会产生空隙,例如气隙,且第一半导体芯片200与信号线220容易受到外界冲击。

89.根据本发明构思,模塑构件515可以容易地进入围绕第一半导体芯片200的第一线区lr1和第二线区lr2。第一半导体芯片200可以被模塑层500围绕,并且在第一半导体芯片200周围的模塑层500中不太可能出现空隙。因此,模塑层500可以保护第一半导体芯片200和信号线220,在半导体封装制造中可以较少出现缺陷,并且可以制造具有增加的结构稳定性的半导体封装。

90.返回参照图2和图4,外部端子105可以形成在基板100的底面上。外部端子105可以包括焊球或焊盘。

91.因此,可以制造如图1至图5所示的半导体封装。

92.根据本发明构思的一些实施例的半导体封装可以被配置为使得模塑层围绕下半导体芯片并且可以在(例如,可以完全填充)下半导体芯片和间隔物之间的空间中。因此,模塑层可以保护下半导体芯片,并且可以增加半导体封装的结构稳定性。

93.根据本发明构思,模塑构件可以容易地引入到围绕下半导体芯片的线区中。模塑构件可以围绕下半导体芯片,并且在围绕下半导体芯片的模塑构件中不太可能出现空隙。因此,模塑层可以保护下半导体芯片,在半导体封装制造中可以较少出现缺陷,并且可以制造半导体封装以具有增加的结构稳定性。

94.尽管已经结合附图中示出的本发明构思的一些实施例描述了本发明,但是本领域普通技术人员将理解,在不脱离本发明构思的范围的情况下可以在其中进行形式和细节的变化。因此,上述公开的实施例应被认为是说明性的而非限制性的。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。